全球電子設(shè)計(jì)創(chuàng)新企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司日前宣布其與TSMC在3D IC設(shè)計(jì)基礎(chǔ)架構(gòu)開(kāi)發(fā)方面的合作。

2012-06-11 09:47:43 1406

1406 Cadence設(shè)計(jì)系統(tǒng)公司,在TSMC最近舉辦的Open Innovation Platform Ecosystem Forum上因DRAM接口IP和技術(shù)方面的相關(guān)論文而獲得“客戶(hù)首選獎(jiǎng)”

2013-01-30 09:08:27 1074

1074 在這篇文章中,筆者將介紹各種不同型態(tài)的 3D IC 技術(shù),由最簡(jiǎn)易的開(kāi)始到目前最先進(jìn)的解決方案。不過(guò)當(dāng)我們開(kāi)始探討3D IC,第一件事情就是要先問(wèn)自己:「我們是想要透過(guò)3D達(dá)成什么目的?」這個(gè)問(wèn)題并不無(wú)厘頭,因?yàn)?b class="flag-6" style="color: red">3D對(duì)不同的人來(lái)說(shuō)可能代表的東西也不同。

2013-12-02 09:14:38 8503

8503

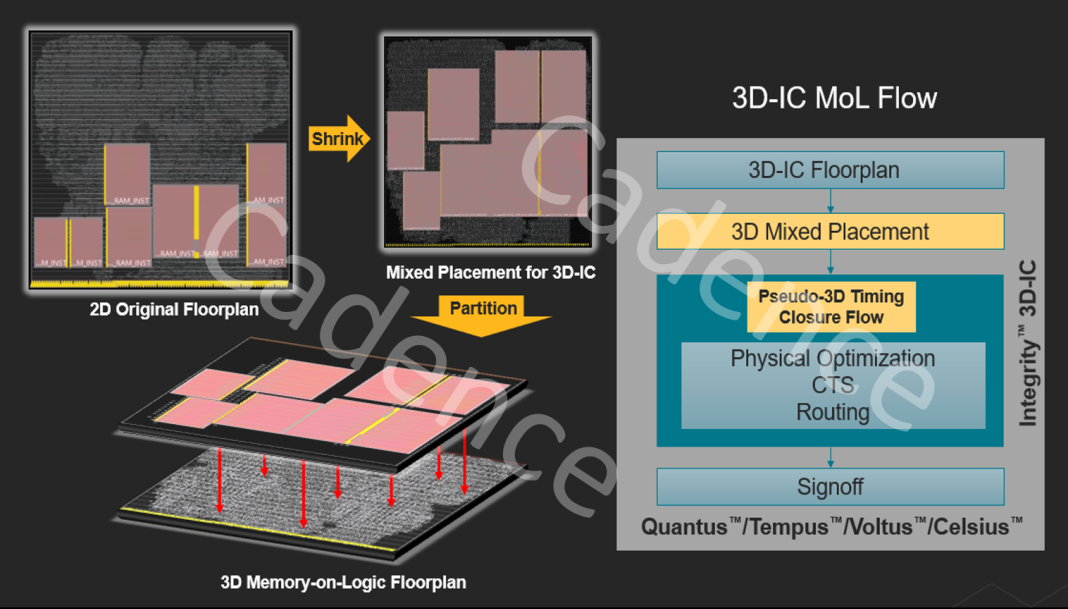

Cadence Integrity 3D-IC 平臺(tái)是業(yè)界首個(gè)全面的整體 3D-IC 設(shè)計(jì)規(guī)劃、實(shí)現(xiàn)和分析平臺(tái),以全系統(tǒng)的視角,對(duì)芯片的性能、功耗和面積 (PPA) 進(jìn)行系統(tǒng)驅(qū)動(dòng)的優(yōu)化,并對(duì) 3D-IC 應(yīng)用的中介層、封裝和印刷電路板進(jìn)行協(xié)同設(shè)計(jì)。

2022-05-23 17:13:53 6023

6023 Integrity 3D-IC 平臺(tái)具有強(qiáng)大的數(shù)據(jù)管理功能,能夠?qū)崿F(xiàn)跨團(tuán)隊(duì)的一鍵數(shù)據(jù)同步與更新。同時(shí),Integrity 3D-IC 支持靈活的 3D-IC 實(shí)現(xiàn)流程,配合其高效的數(shù)據(jù)管理機(jī)制,可以讓用戶(hù)在流程中的多個(gè)關(guān)鍵階段接入內(nèi)嵌的分析平臺(tái),進(jìn)而實(shí)現(xiàn)整個(gè)系統(tǒng)的快速迭代和 ECO。

2022-07-19 09:34:44 3855

3855

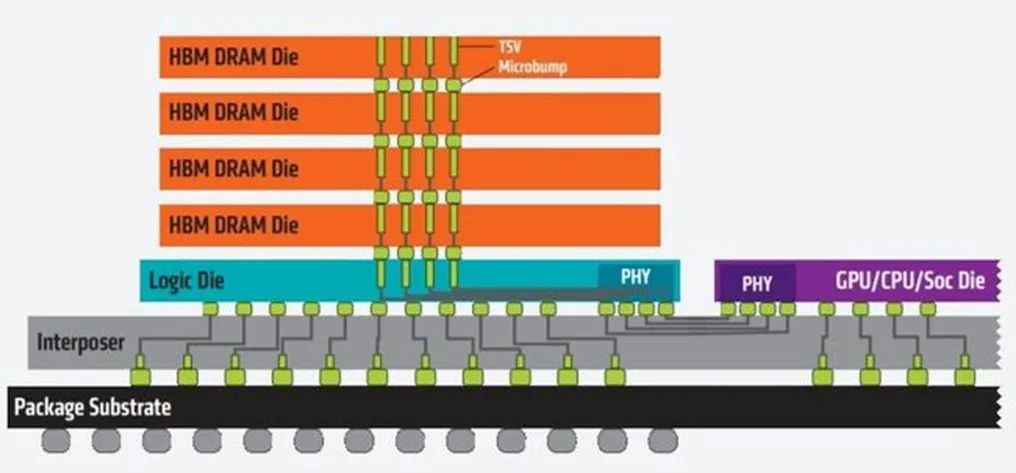

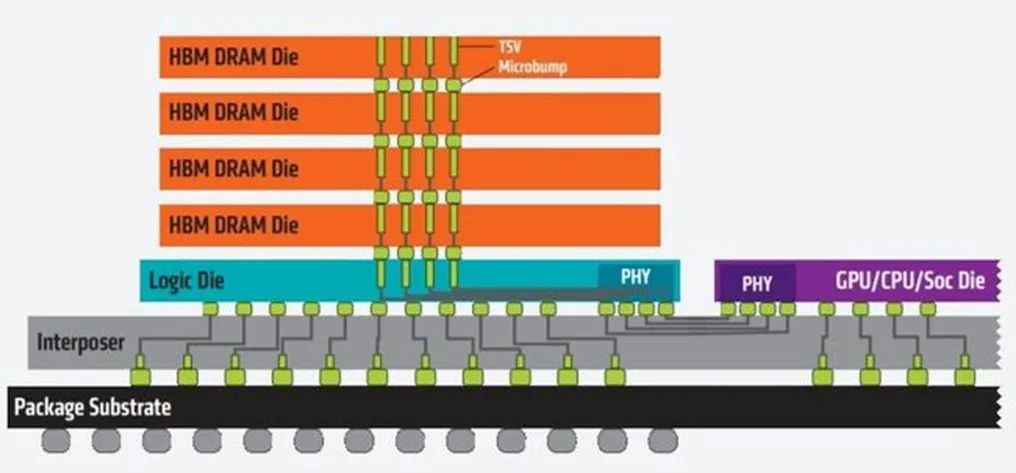

隨著芯片工藝尺寸的縮小趨于飽和或停滯,設(shè)計(jì)師們現(xiàn)在專(zhuān)注于通過(guò) 3D-IC 異構(gòu)封裝,在芯片所在平面之外的三維空間中構(gòu)建系統(tǒng)。3D-IC 異構(gòu)封裝結(jié)構(gòu)可能包括多個(gè)芯片,它們被放置在一個(gè)通用的中介層上,或者通過(guò)芯片內(nèi)部的高級(jí)互連來(lái)集成內(nèi)存單元、處理器和其他功能模塊。

2022-12-09 11:02:18 5747

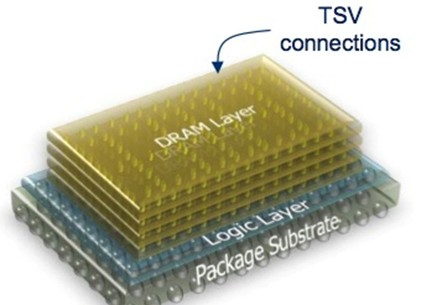

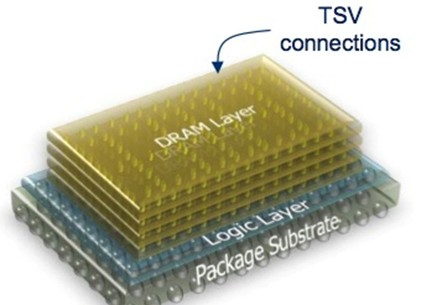

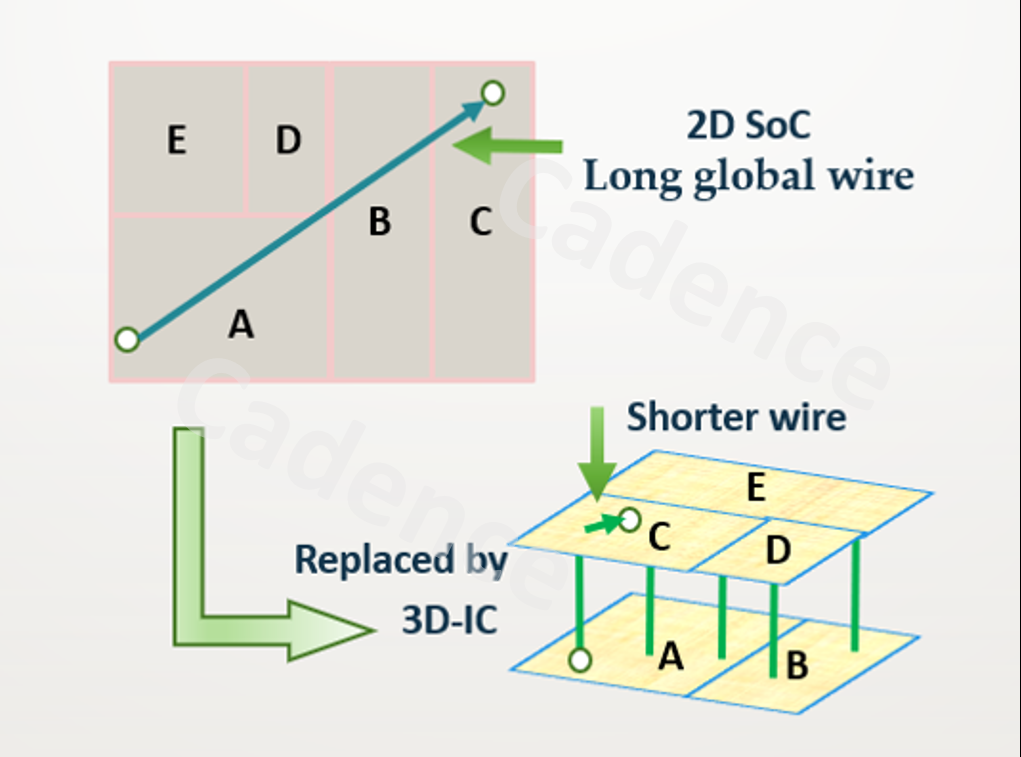

5747 3D-IC通過(guò)采用TSV(Through-Silicon Via,硅通孔)技術(shù),實(shí)現(xiàn)了不同層芯片之間的垂直互連。這種設(shè)計(jì)顯著提升了系統(tǒng)集成度,同時(shí)有效地縮短了互連線的長(zhǎng)度。這樣的改進(jìn)不僅降低了信號(hào)傳輸?shù)难訒r(shí),還減少了功耗,從而全面提升了系統(tǒng)的整體性能。

2025-02-21 15:57:02 2460

2460

楷登電子今日發(fā)布Cadence? Clarity? 3D Solver場(chǎng)求解器,正式進(jìn)軍快速增長(zhǎng)的系統(tǒng)級(jí)分析和設(shè)計(jì)市場(chǎng)。與傳統(tǒng)的三維場(chǎng)求解器相比,Cadence? Clarity? 3D Solver場(chǎng)求解器在精度達(dá)到黃金標(biāo)準(zhǔn)的同時(shí),擁有高達(dá)10倍的仿真性能和近乎無(wú)限的處理能力。

2019-04-13 09:23:21 11911

11911 半導(dǎo)體和 3D-IC 設(shè)計(jì)方面取得新突破; 依托 30 年來(lái)在全線工藝技術(shù)方面取得的行業(yè)領(lǐng)先地位,將大型設(shè)計(jì)的生產(chǎn)力提升 3 倍,助力塑造未來(lái)格局。 ? 中國(guó)上海, 2023 年 4 月 20 日

2023-04-20 15:52:13 1036

1036

3nm 時(shí)代來(lái)臨了!Cadence 在 2023 年 TSMC 北美技術(shù)研討會(huì)期間發(fā)布了面向臺(tái)積電 3nm 工藝(N3E)的 112G 超長(zhǎng)距離(112G-ELR)SerDes IP 展示,這是

2023-05-19 16:25:12 1405

1405

電子發(fā)燒友網(wǎng)報(bào)道(文/吳子鵬)當(dāng)摩爾定律逼近物理極限,3D-IC成為延續(xù)算力指數(shù)級(jí)增長(zhǎng)的新選擇;當(dāng)大模型發(fā)展一日千里,AI開(kāi)始反向定義芯片設(shè)計(jì)與需求。兩條技術(shù)曲線在同一時(shí)空交匯,EDA工具鏈的智能化

2025-11-27 08:51:00 7168

7168 3D顯示技術(shù)的原理是什么?3D顯示技術(shù)有哪些應(yīng)用?3D拍好了到底怎么樣傳輸?

2021-05-31 06:53:03

設(shè)計(jì),并與封裝設(shè)計(jì)團(tuán)隊(duì)和使用Cadence Allegro? 封裝技術(shù)的外包半導(dǎo)體組裝和測(cè)試 (OSAT) 公司進(jìn)行無(wú)縫協(xié)同設(shè)計(jì)。 使用 Integrity 3D-IC 平臺(tái)的客戶(hù)可以獲得以下功能和優(yōu)勢(shì)

2021-10-14 11:19:57

的錯(cuò)誤日志 1. iMX8QM安卓平臺(tái)支持3D游戲嗎?2. 如果是,是否需要額外添加一些東西才能啟用 3D 游戲?

2023-04-04 07:42:57

本帖最后由 gk320830 于 2015-3-4 19:06 編輯

在cadence ic版圖設(shè)計(jì)中tsmc.18,寬長(zhǎng)比4/0.18的mosfet怎么畫(huà)?有多少層?每一層什么意義?

2014-10-06 08:07:57

新思科技 (Synopsys)今日宣布利用3D-IC整合技術(shù)加速多晶片堆疊系統(tǒng) (stackedmultiple-die silicon system)的設(shè)計(jì)

2012-03-28 08:57:44 892

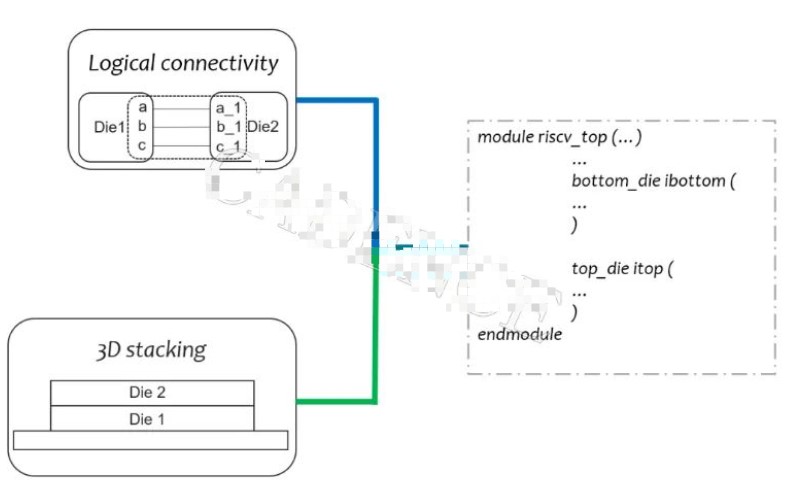

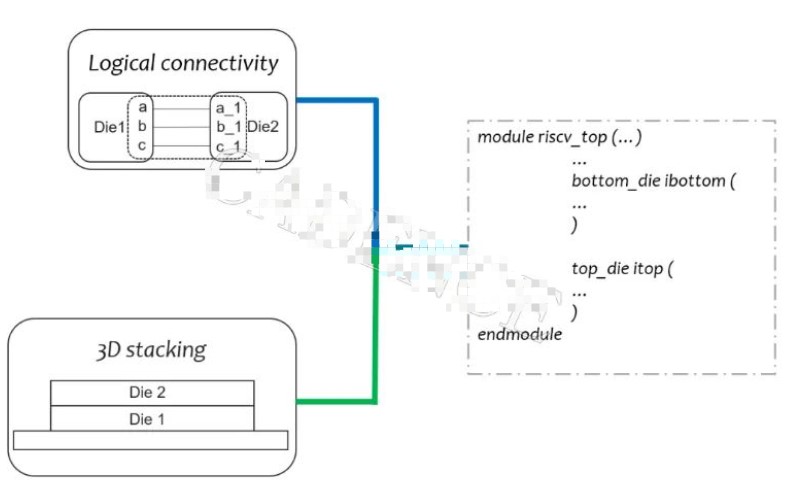

892 新思科技(Synopsys)宣布利用3D-IC整合技術(shù)加速多晶片堆疊系統(tǒng)(stacked multiple-die silicon system)的設(shè)計(jì),以滿(mǎn)足當(dāng)今電子產(chǎn)品在運(yùn)算速度提升、結(jié)構(gòu)尺寸縮小及功耗降低等面向上的需求。

2012-03-29 13:43:07 2542

2542 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設(shè)計(jì)架構(gòu)。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺(tái)。

2012-10-22 16:48:03 1286

1286 電子發(fā)燒友網(wǎng)訊: TSMC授予Cadence兩項(xiàng)年度合作伙伴獎(jiǎng)項(xiàng),兩項(xiàng)大獎(jiǎng)表彰Cadence在幫助客戶(hù)加快設(shè)計(jì)的3D-IC CoWoS技術(shù)與20納米參考流程方面的重要貢獻(xiàn)。 TSMC授予全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)

2012-11-07 11:48:07 1214

1214 Cadence致力于完善EDA工具,為業(yè)界提供從系統(tǒng)設(shè)計(jì)驗(yàn)證、芯片實(shí)現(xiàn)到三維封裝以及PCB板級(jí)的一整套方案。Cadence分別與TSMC及IBM合作生產(chǎn)出第一顆3D IC實(shí)驗(yàn)芯片和第一顆ARM Cortex-M0處理器。

2012-12-11 09:14:10 1459

1459 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲(chǔ)器設(shè)計(jì)上進(jìn)行了驗(yàn)證 ,可實(shí)現(xiàn)多塊模的整合。它將臺(tái)積電的3D堆疊技術(shù)和Cadence?3D-IC解決方案相結(jié)合,包括了集成的設(shè)計(jì)工具、靈活的實(shí)現(xiàn)平臺(tái),以及最終的時(shí)序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1717

1717 WILSONVILLE, Ore., 2016年3月15日— Mentor Graphics公司(納斯達(dá)克代碼:MENT)今天發(fā)布了一款結(jié)合設(shè)計(jì)、版圖布局和驗(yàn)證的解決方案,為TSMC集成扇出型 (InFO) 晶圓級(jí)封裝技術(shù)的設(shè)計(jì)應(yīng)用提供支持。

2016-03-15 14:06:02 1298

1298 模型,并且更容易控制如何實(shí)際打印該模型。其次,我們將介紹我們自己的3D打印機(jī),它將作為SCAP的參考實(shí)現(xiàn)。它將展示火花平臺(tái)的力量,并為3D打印用戶(hù)體驗(yàn)設(shè)定新的基準(zhǔn)。總之,這些將提供產(chǎn)品設(shè)計(jì)師、硬件制造商、軟件開(kāi)發(fā)者和材料科學(xué)家可以用來(lái)繼續(xù)探索3D打印技術(shù)的限制的構(gòu)建塊。

2018-05-08 06:03:00 3812

3812 Platform支持與3D IC參考流程相結(jié)合,幫助用戶(hù)在移動(dòng)計(jì)算、網(wǎng)絡(luò)通信、消費(fèi)和汽車(chē)電子等應(yīng)用中部署高性能、高連接性的多裸晶芯片技術(shù)。 新思科技Design Platform解決方案包括多裸晶芯片和中介

2018-10-27 22:14:01 828

828 EV集團(tuán)將在SEMICON CHINA展出用于3D-IC封裝的突破性晶圓鍵合技術(shù) 較之上一代對(duì)準(zhǔn)系統(tǒng),GEMINI FB XT 熔融鍵合機(jī)上的全新 SmartView NT3 對(duì)準(zhǔn)系統(tǒng)可提升2-3

2019-03-05 14:21:36 2554

2554 根據(jù)臺(tái)積電在第二十四屆年度技術(shù)研討會(huì)中的說(shuō)明,SoIC是一種創(chuàng)新的多芯片堆疊技術(shù),是一種晶圓對(duì)晶圓(Wafer-on-wafer)的鍵合(Bonding)技術(shù),這是一種3D IC制程技術(shù),可以讓臺(tái)積電具備直接為客戶(hù)生產(chǎn)3D IC的能力。

2019-08-14 11:21:06 4993

4993

(功耗、性能和面積)優(yōu)勢(shì),同時(shí)加快產(chǎn)品上市時(shí)間 ● 新思科技進(jìn)一步強(qiáng)化關(guān)鍵產(chǎn)品,以支持TSMC N3制造的進(jìn)階要求 新思科技(Synopsys)近日宣布,其數(shù)字和定制設(shè)計(jì)平臺(tái)已獲得TSMC 3nm制造技術(shù)驗(yàn)證。此次驗(yàn)證基于TSMC的最新設(shè)計(jì)參考手冊(cè)(DRM)和工藝設(shè)計(jì)工具包(

2020-10-14 10:47:57 2542

2542 Direct3D 上運(yùn)行。 而伴隨著跨平臺(tái)代碼的合并,對(duì) Gallium D3D12 代碼的開(kāi)發(fā)工作得到不斷推進(jìn)。 盡管這個(gè) Gallium Direct3D 12 代碼提供了跨平臺(tái)支持,但是用例是在

2020-12-03 11:45:44 1911

1911 近日,芯原股份在接受機(jī)構(gòu)調(diào)研時(shí)表示,Chiplet 帶來(lái)很多新的市場(chǎng)機(jī)遇,公司作為具有平臺(tái)化芯片設(shè)計(jì)能力的 IP 供應(yīng)商,已經(jīng)開(kāi)始推進(jìn)對(duì)Chiplet的布局,開(kāi)始與全球領(lǐng)先的晶圓廠展開(kāi)基于5nm

2021-01-08 12:57:56 3351

3351 兩個(gè)芯片。這種方案很便宜,但沒(méi)有太大的帶寬。在這個(gè)簡(jiǎn)單的實(shí)現(xiàn)之上,還有多種方法可以將多個(gè)小芯片連接在一起,而臺(tái)積電擁有許多這樣的技術(shù)。為了統(tǒng)一其2.5D和3D封裝變體的所有不同名稱(chēng),TSMC在早前的技術(shù)大會(huì)上推出了其新的首要品牌:3DFabric。

2021-03-08 14:55:39 2512

2512 腳本創(chuàng)建和操作,使用JSON數(shù)據(jù)格式。下面詳細(xì)介紹IndexedDB本地緩存技術(shù),作為一種瀏覽器數(shù)據(jù)存儲(chǔ)方案,對(duì)場(chǎng)景項(xiàng)目開(kāi)發(fā)有極大的意義。 ① ?本地緩存技術(shù)提升用戶(hù)訪問(wèn)體驗(yàn) ThingJS平臺(tái)支持在線開(kāi)發(fā)面向物聯(lián)網(wǎng)的3D可視化項(xiàng)目,當(dāng)用戶(hù)初次訪問(wèn)項(xiàng)目文件時(shí),需先將3D模型數(shù)據(jù)

2021-03-13 11:19:20 2128

2128 )宣布,其數(shù)字和定制/模擬流程已獲得 TSMC N3 和 N4 工藝技術(shù)認(rèn)證,支持最新的設(shè)計(jì)規(guī)則手冊(cè)(DRM)。通過(guò)持續(xù)合作,Cadence 和 TSMC 發(fā)布了 TSMC N3 和 N

2021-10-26 15:10:58 3128

3128 新思科技3DIC Compiler是統(tǒng)一的多裸晶芯片設(shè)計(jì)實(shí)現(xiàn)平臺(tái),無(wú)縫集成了基于臺(tái)積公司3DFabric技術(shù)的設(shè)計(jì)方法,提供完整的“探索到簽核”的設(shè)計(jì)平臺(tái)

2021-11-01 16:29:14 704

704 雙方拓展戰(zhàn)略合作,提供全面的3D系統(tǒng)集成功能,支持在單一封裝中集成數(shù)千億個(gè)晶體管 新思科技3DIC Compiler是統(tǒng)一的多裸晶芯片設(shè)計(jì)實(shí)現(xiàn)平臺(tái),無(wú)縫集成了基于臺(tái)積公司3DFabric技術(shù)

2021-11-05 15:17:19 6382

6382 創(chuàng)建邏輯內(nèi)存器件的 3D 堆疊配置,優(yōu)化 3D 堆疊設(shè)計(jì)的 PPA 結(jié)果。 客戶(hù)可以放心采用 Cadence Integrity 3D-IC 平臺(tái)和 Samsung Foundry 的多 Die 實(shí)現(xiàn)

2021-11-19 11:02:24 4231

4231 研討會(huì)”。作為 2022 年第一場(chǎng)線下研討會(huì),Cadence將集聚相關(guān)軟件開(kāi)發(fā)者與資深技術(shù)專(zhuān)家,與各位客戶(hù)朋友們分享關(guān)于 Cadence 3D-IC Integrity 平臺(tái)在統(tǒng)一環(huán)境中提供 3D

2022-01-04 08:56:51 2109

2109 電子設(shè)計(jì)自動(dòng)化領(lǐng)域領(lǐng)先的供應(yīng)商 Cadence,誠(chéng)邀您參加將于2022 年 1 月 20 日于上海浦東嘉里酒店舉辦的“2022 CadenceCONNECT: 3D-IC 設(shè)計(jì)與全系統(tǒng)解決方案-上海研討會(huì)”。

2022-01-20 11:11:42 2078

2078 Cadence Clarity 3D Solver 2022版本發(fā)布 電磁設(shè)計(jì)同步分析功能提高效率 最新的電磁設(shè)計(jì)同步分析功能有助于提高 IC、IC 封裝和高性能 PCB 設(shè)計(jì)的速度。 美國(guó)加州

2022-04-29 14:42:29 6216

6216 (Signal Integrity, SI)、電源完整性 (Power

Integrity, PI) 及可靠性?xún)?yōu)化。總結(jié)了目前 2.5D/3D 芯片仿真進(jìn)展與挑戰(zhàn),介紹了基于芯片模型的

Ansys 芯片-封裝-系統(tǒng) (CPS) 多物理場(chǎng)協(xié)同仿真方法,闡述了如何模擬芯片在真實(shí)工況下達(dá)到優(yōu)化

芯片信

2022-05-06 15:20:42 19

19 Cadence Integrity 3D-IC 平臺(tái)是業(yè)界首個(gè)全面的整體 3D-IC 設(shè)計(jì)規(guī)劃、實(shí)現(xiàn)和分析平臺(tái),以全系統(tǒng)的視角,對(duì)芯片的性能、功耗和面積 (PPA) 進(jìn)行系統(tǒng)驅(qū)動(dòng)的優(yōu)化,并對(duì) 3D-IC 應(yīng)用的中介層、封裝和印刷電路板進(jìn)行協(xié)同設(shè)計(jì)。

2022-05-23 16:52:50 2846

2846

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論