Chiplet主流封裝技術(shù)都有哪些?

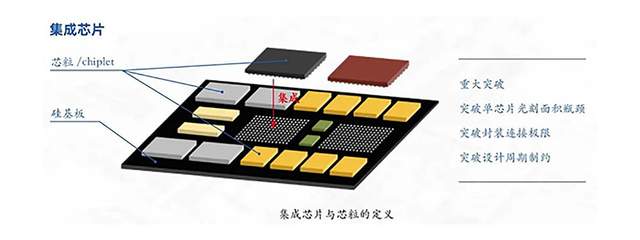

隨著處理器和芯片設(shè)計(jì)的發(fā)展,芯片的封裝技術(shù)也在不斷地更新和改進(jìn)。Chiplet是一種新型的封裝技術(shù),它可以將不同的芯片功能模塊制造在不同的芯片中,并通過不同的連接技術(shù)把它們拼裝在一起,以實(shí)現(xiàn)更高效和更高性能的芯片設(shè)計(jì)。本文將會詳盡、詳實(shí)、細(xì)致地介紹Chiplet主流的封裝技術(shù)。

1. 面向異構(gòu)集成的2.5D/3D技術(shù)

2.5D/3D技術(shù)是Chiplet主流封裝技術(shù)中最為流行和成熟的一種,通過把不同的芯片堆疊在一起,可以將它們的性能整合到一個極小的空間中。在2.5D技術(shù)中,至少兩個芯片被組合在一起,通過高速芯片間互連(like microbumps)進(jìn)行通訊,在3D技術(shù)中,這些芯片的高度可以多達(dá)幾個mm。這種技術(shù)的主要有點(diǎn)是它可以提供比傳統(tǒng)集成電路更高的性能和功能集成度。

2. 基于許多小型芯片互連的Chiplet技術(shù)

這種封裝技術(shù)是Chiplet封裝技術(shù)中相對較新的一種,也被稱為“芯片驅(qū)動器芯片”(CDM)技術(shù)。這種技術(shù)的核心想法是將一個大型芯片拆分成許多小型芯片,并將不同芯片通過小型連接器連接在一起。這些小型芯片的缺點(diǎn)是它們單獨(dú)時性能不如大型芯片,但組合在一起后可以提供更高的性能和更高的靈活性。這種方法可在需要更高性能和更高靈活性的云環(huán)境下得到采用。

3. 多晶片半導(dǎo)體封裝技術(shù)

多晶片半導(dǎo)體封裝技術(shù)是在半導(dǎo)體領(lǐng)域最廣為人知的封裝技術(shù)之一。這種技術(shù)通過將多個芯片連接在一起,以形成一個更大的半導(dǎo)體晶片來增強(qiáng)性能。多晶片封裝同樣可以通過互連技術(shù)來提高不同芯片之間的通訊速度,例如通過微針來連接芯片。

4. 光互連和光學(xué)封裝技術(shù)

光互連技術(shù)可以大幅提高芯片之間的通訊速度,并在時鐘頻率和數(shù)據(jù)傳輸速度方面提供更高的性能。通過使用光學(xué)技術(shù),可以將多個芯片連接在一起,從而實(shí)現(xiàn)更高的通訊帶寬和更低的能耗,其實(shí)主要靠的就是光通訊芯片的加持。

5. 雪片式封裝技術(shù)

雪片式封裝技術(shù)就是讓多個芯片獨(dú)立工作,互相交換數(shù)據(jù),依賴于軟件的實(shí)現(xiàn),即使用多芯片系統(tǒng)對單一芯片進(jìn)行擴(kuò)展,在架構(gòu)上,有多個CPU核心、多個GPU和多種加速器等很多芯片,可以被用來協(xié)同完成大規(guī)模任務(wù)。

總結(jié)

Chiplet技術(shù)是一種新型封裝技術(shù),以不同的方式組合、堆疊芯片以實(shí)現(xiàn)更高集成度和更高性能。它有幾種主要的實(shí)現(xiàn)方法,包括2.5D/3D技術(shù)、CDM技術(shù)、多芯片封裝技術(shù)、光互連和光學(xué)封裝技術(shù)以及雪花式封裝技術(shù)。每種方法都有其優(yōu)點(diǎn)和劣勢,因此選用哪種技術(shù)將取決于所需的應(yīng)用和實(shí)際環(huán)境。

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252208 -

驅(qū)動器

+關(guān)注

關(guān)注

54文章

9082瀏覽量

155491 -

芯片封裝

+關(guān)注

關(guān)注

13文章

614瀏覽量

32261 -

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13601

發(fā)布評論請先 登錄

多Chiplet異構(gòu)集成的先進(jìn)互連技術(shù)

如何突破AI存儲墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構(gòu)

西門子EDA如何推動Chiplet技術(shù)商業(yè)化落地

Chiplet核心挑戰(zhàn)破解之道:瑞沃微先進(jìn)封裝技術(shù)新思路

Chiplet封裝設(shè)計(jì)中的信號與電源完整性挑戰(zhàn)

解構(gòu)Chiplet,區(qū)分炒作與現(xiàn)實(shí)

Chiplet與先進(jìn)封裝全生態(tài)首秀即將登場!匯聚產(chǎn)業(yè)鏈核心力量共探生態(tài)協(xié)同新路徑!

CMOS 2.0與Chiplet兩種創(chuàng)新技術(shù)的區(qū)別

Chiplet與3D封裝技術(shù):后摩爾時代的芯片革命與屹立芯創(chuàng)的良率保障

突破!華為先進(jìn)封裝技術(shù)揭開神秘面紗

從技術(shù)封鎖到自主創(chuàng)新:Chiplet封裝的破局之路

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進(jìn)封裝

Chiplet技術(shù)在消費(fèi)電子領(lǐng)域的應(yīng)用前景

Chiplet:芯片良率與可靠性的新保障!

Chiplet主流封裝技術(shù)都有哪些?

Chiplet主流封裝技術(shù)都有哪些?

評論