來源:芝能芯芯

半導體行業的不斷進步和技術的發展,3D-IC(三維集成電路)和異構芯片設計已成為提高性能的關鍵途徑。然而,這種技術進步伴隨著一系列新的挑戰,尤其是在熱管理和布局規劃方面。

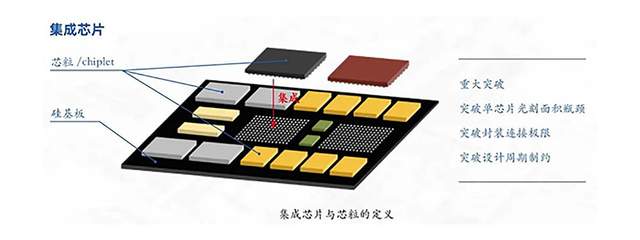

我們探討3D-IC和Chiplet設計所帶來的挑戰及其對物理布局工具的影響,并討論EDA(電子設計自動化)供應商如何應對這些挑戰。

Part 1

3D-IC 和異構芯片出現對設計帶來的影響

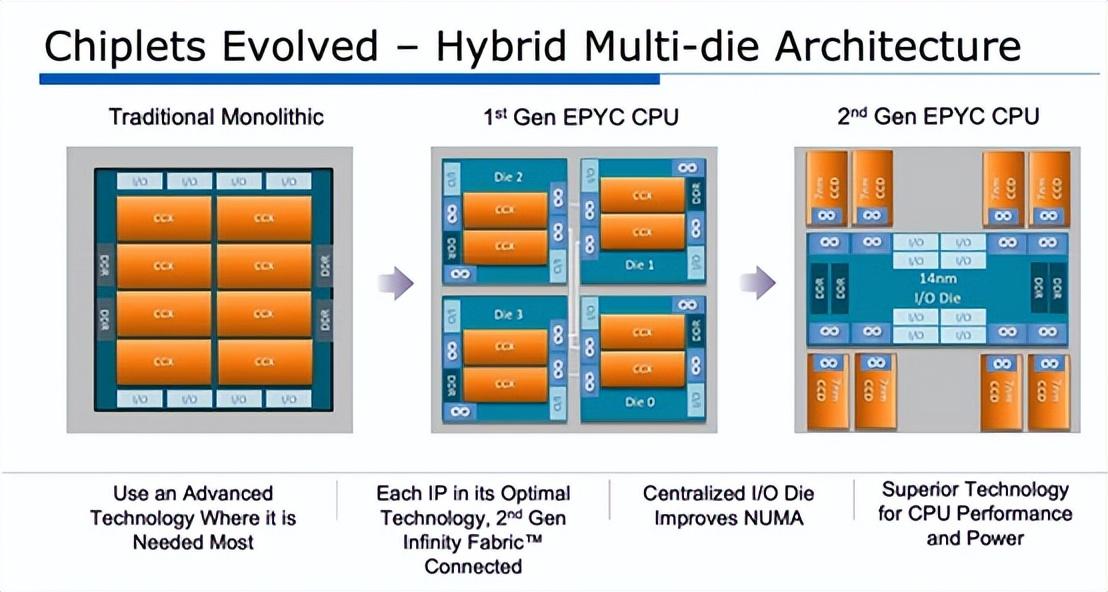

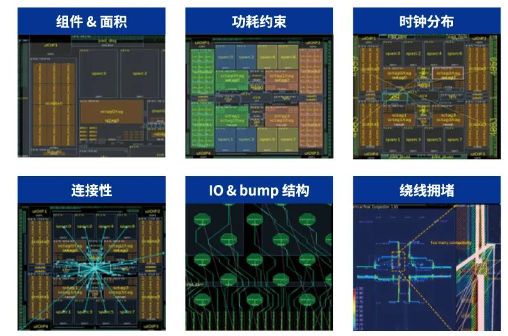

3D-IC 和異構芯片的出現要求對物理布局工具進行重大變革。芯片的放置和信號布線對整體系統性能和可靠性有著至關重要的影響。散熱成為 3D-IC 面臨的首要難題,邏輯芯片的堆疊導致熱量產生增加,而減薄基板雖縮短了信號傳輸距離,卻降低了傳熱能力,散熱器也不再適用。

解決方法在于精心配置芯片層,使熱量分散或限制在可有效散熱的區域,這需要內置到自動化工具中。例如,在實際應用中,若將高性能計算芯片進行 3D 堆疊,由于其高功率運行產生的大量熱量,若布局規劃不合理,可能導致局部過熱,影響芯片性能和穩定性。

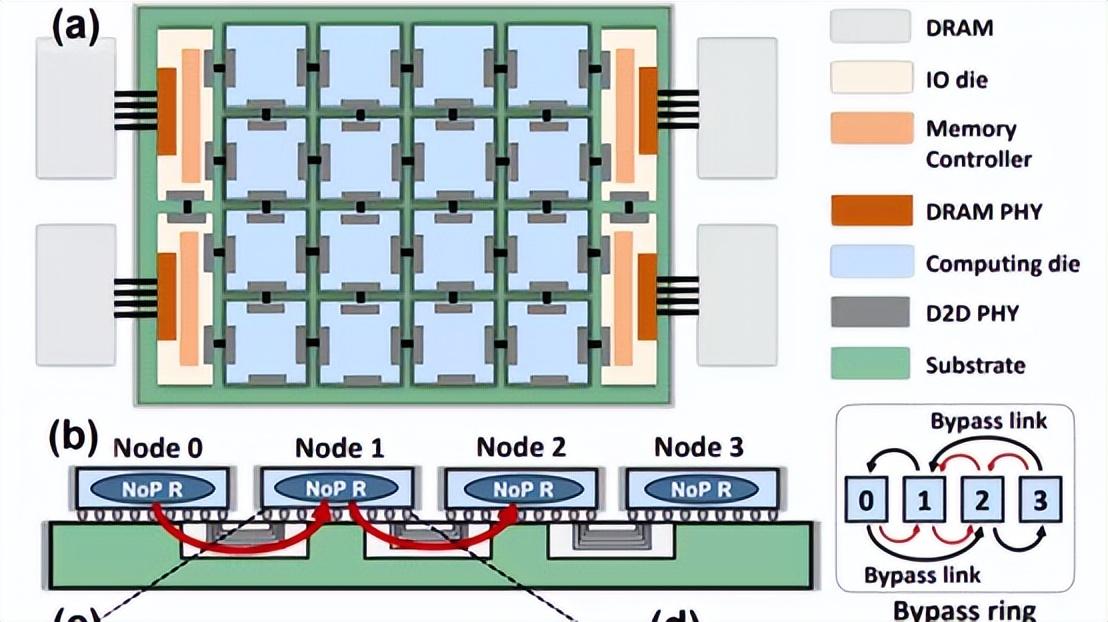

布局規劃、布局、時鐘和布線是布局布線流程的主要階段。布局規劃探索在流程早期進行,確定功能模塊的位置和連接性。隨著技術發展,從傳統的平面設計轉變為 3D 設計,設計變得更為復雜,需要考慮更多維度的因素,如芯片間的耦合效應、電阻率和時序路徑等。

在智能手機芯片設計中,不僅要考慮 CPU 和 GPU 的布局,還要考慮它們與內存芯片、通信芯片等在 3D 空間中的交互,以確保性能最優且散熱良好。

Part 2

Chiplet設計的影響

Chiplet設計改變了傳統的布局布線流程,需要對邏輯分區進行優化,并且在設計流程中必須考慮多芯片集成、異構技術以及高密度芯片間互連的復雜性。這要求EDA工具具備更強的多物理場模擬能力和智能化水平,以便更好地支持設計決策。

熱效應在3D結構中尤為重要,因為熱串擾可能影響設計的可靠性。為了管理這些效應,設計團隊需要打破傳統學科間的壁壘,將熱模擬等多物理效應更早地引入設計過程。

此外,由于電壓/頻率的動態變化會影響性能和計算吞吐量,因此需要進行瞬態熱功率斜坡建模。

EDA供應商正在積極開發新一代工具,這些工具不僅能夠處理傳統信號完整性和電源完整性分析,還能支持熱管理、信號完整性感知布線等高級功能。

此外,隨著AI技術的進步,EDA工具正在整合更多的人工智能功能,以實現更高效的設計和優化。

隨著Chiplet設計和3D-IC技術的進一步發展,EDA工具將繼續進化以滿足更高層次的設計要求。未來的設計流程將更加自動化,并利用機器學習和人工智能技術來預測和優化設計結果。

同時,跨領域合作將成為關鍵,以確保設計符合所有必要的約束條件。

3D-IC和Chiplet設計為半導體行業帶來了前所未有的機遇和挑戰。為了克服這些挑戰,設計工具和流程必須不斷發展以支持更先進的技術。EDA供應商正通過創新的方法來應對這些挑戰,而隨著技術的進步,我們可以期待在未來幾年內看到更加高效和自動化的設計流程。

小結

隨著行業逐步過渡到Chiplet時代,我們正處于一個轉折點,這將對未來的電子產品產生深遠影響。EDA工具和設計流程的持續創新將是確保這一轉型成功的關鍵。

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54016瀏覽量

466292 -

chiplet

+關注

關注

6文章

495瀏覽量

13604

發布評論請先 登錄

TCP/IP(Socket)協議深度剖析

串口協議的深度剖析

如何突破AI存儲墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構

躍昉科技受邀出席第四屆HiPi Chiplet論壇

得一微電子受邀出席第四屆HiPi Chiplet論壇

Chiplet封裝設計中的信號與電源完整性挑戰

解構Chiplet,區分炒作與現實

Chiplet與先進封裝全生態首秀即將登場!匯聚產業鏈核心力量共探生態協同新路徑!

動態IP技術演進:從網絡基石到智能連接時代的創新引擎

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet:芯片良率與可靠性的新保障!

剖析 Chiplet 時代的布局規劃演進

剖析 Chiplet 時代的布局規劃演進

評論