鍵合玻璃載板(Glass Carrier/Substrate)是一種用于半導體封裝工藝的臨時性硬質支撐材料,通過鍵合技術與硅晶圓或芯片臨時固定在一起,在特定工序(如減薄、RDL布線)完成后通過紫外光

2026-01-05 09:23:37 536

536 扇出型晶圓級封裝(FOWLP)的概念最早由德國英飛凌提出,自2016 年以來,業界一直致力于FOWLP 技術的發展。

2026-01-04 14:40:30 174

174

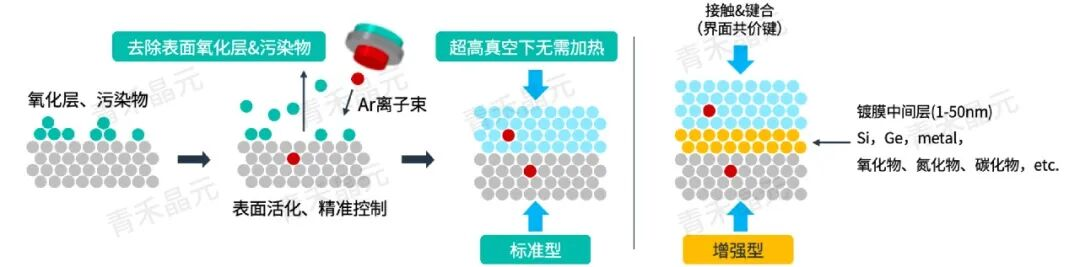

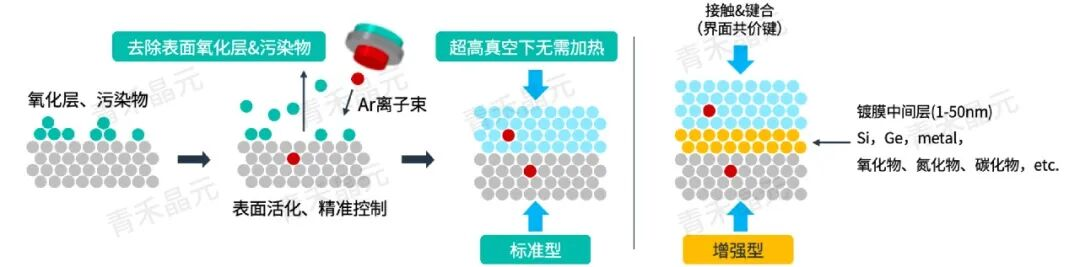

關鍵詞: 常溫鍵合;第三代半導體;異質集成;半導體設備;青禾晶元;半導體技術突破;碳化硅(SiC);氮化鎵(GaN);超高真空鍵合;先進封裝;摩爾定律 隨著5G/6G通信、新能源汽車與人工智能對芯片

2025-12-29 11:24:17 133

133

(SiGe BiCMOS)工藝領域,正式推出支持光電共封裝(CPO)的新型代工技術。 ? 這項技術依托多年堆疊式背照式(BSI)圖像傳感器量產經驗,實現異構 3D-IC 集成,并獲得 Cadence

2025-11-21 08:46:00 4242

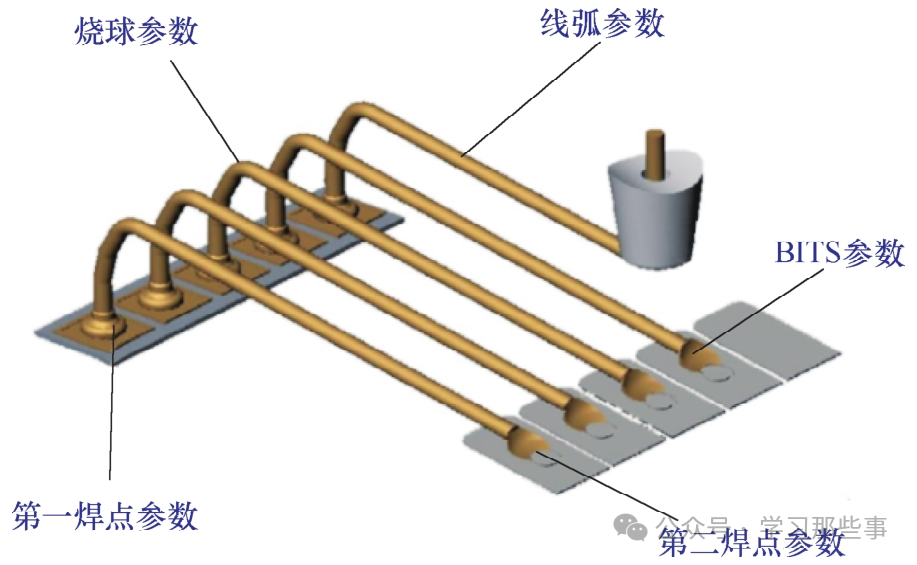

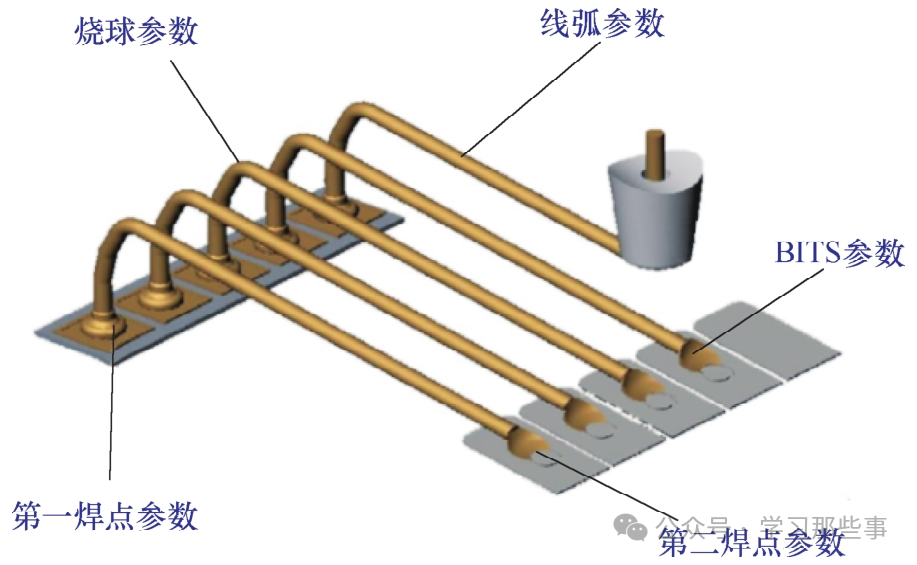

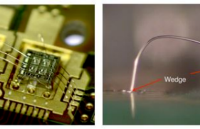

4242 在現代微電子封裝領域,集成電路(IC)的可靠性與穩定性是決定產品品質的關鍵。其中,鍵合點的機械強度直接影響到芯片在后續加工、運輸及使用過程中的性能表現。IC鋁帶作為一種重要的內引線材料,其與芯片焊盤

2025-11-09 17:41:45 1162

1162

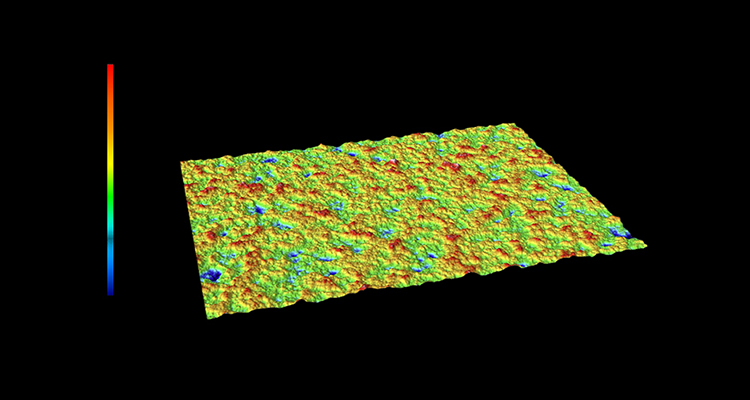

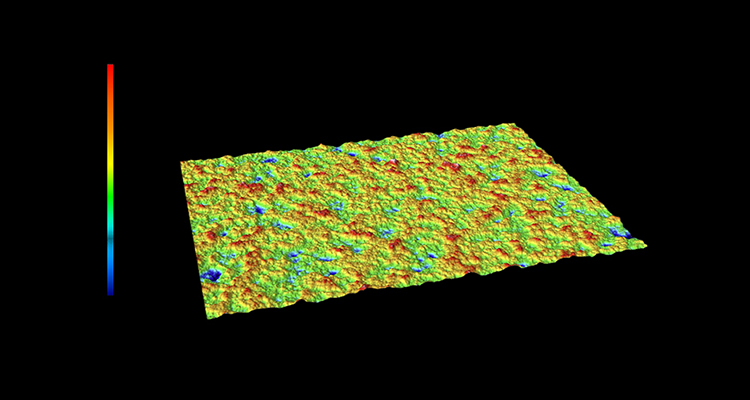

摘要:本文研究白光干涉儀在晶圓深腐蝕溝槽 3D 輪廓測量中的應用,分析其工作原理及適配深腐蝕溝槽特征的技術優勢,通過實際案例驗證測量精度,為晶圓深腐蝕工藝的質量控制與器件性能優化提供技術

2025-10-30 14:22:51 225

225

電子元器件封裝中的引線鍵合工藝,是實現芯片與外部世界連接的關鍵技術。其中,金鋁鍵合因其應用廣泛、工藝簡單和成本低廉等優勢,成為集成電路產品中常見的鍵合形式。金鋁鍵合失效這種現象雖不為人所熟知,卻是

2025-10-24 12:20:57 444

444

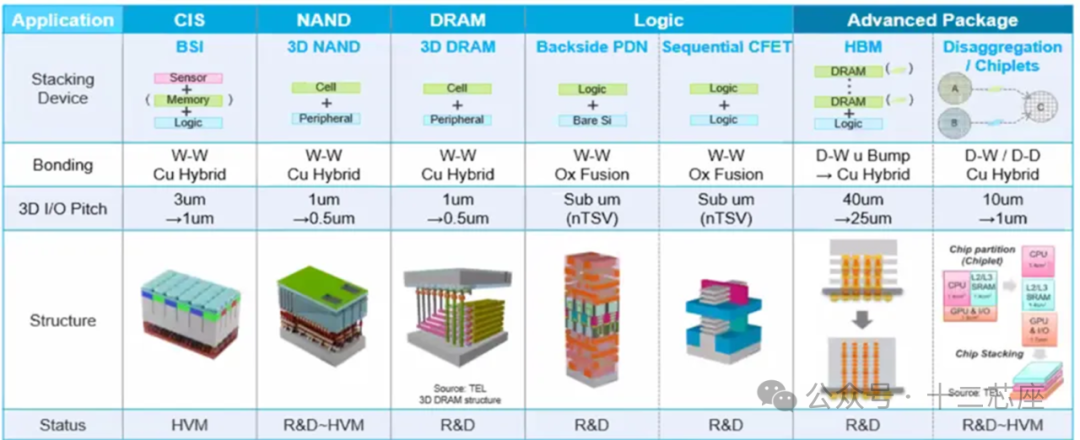

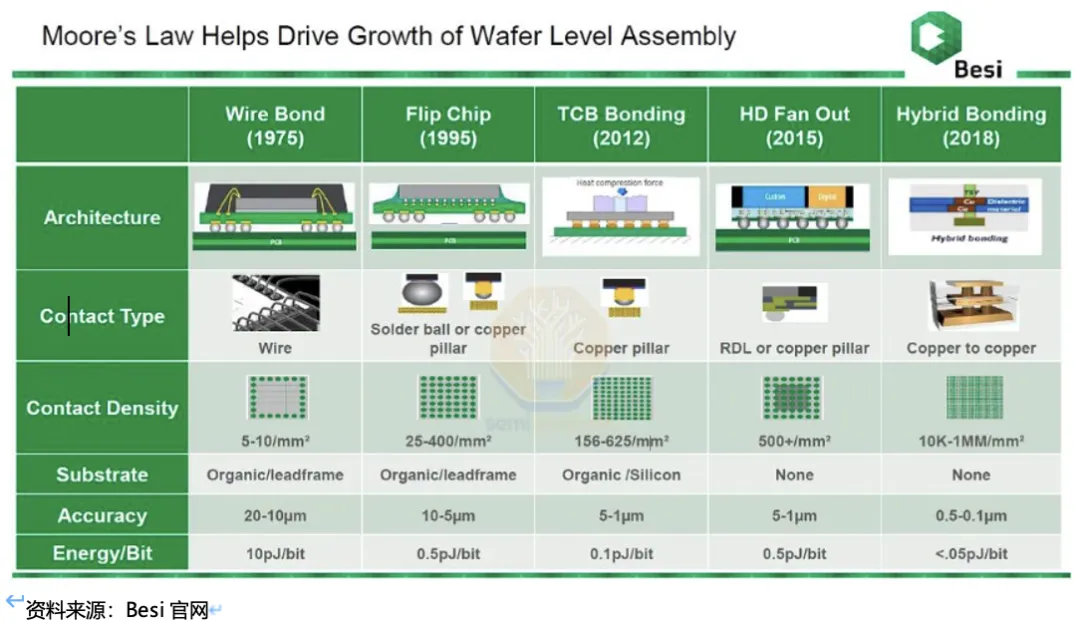

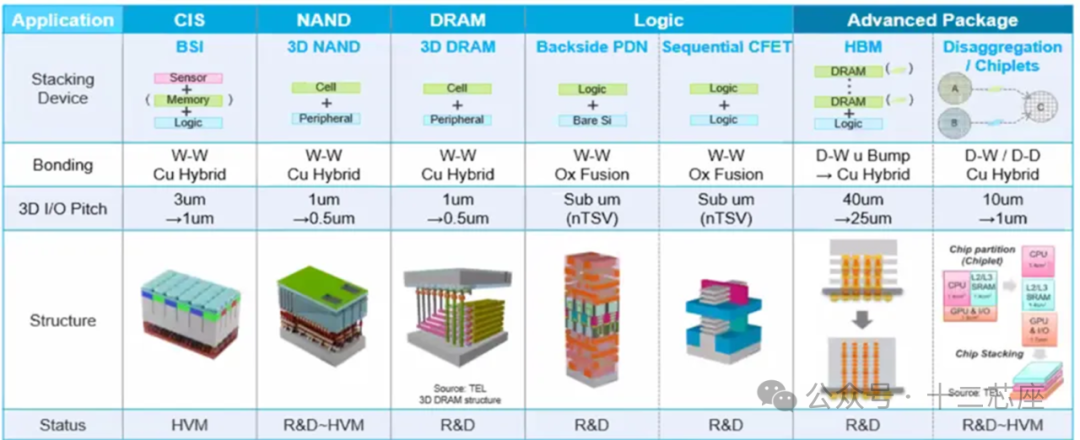

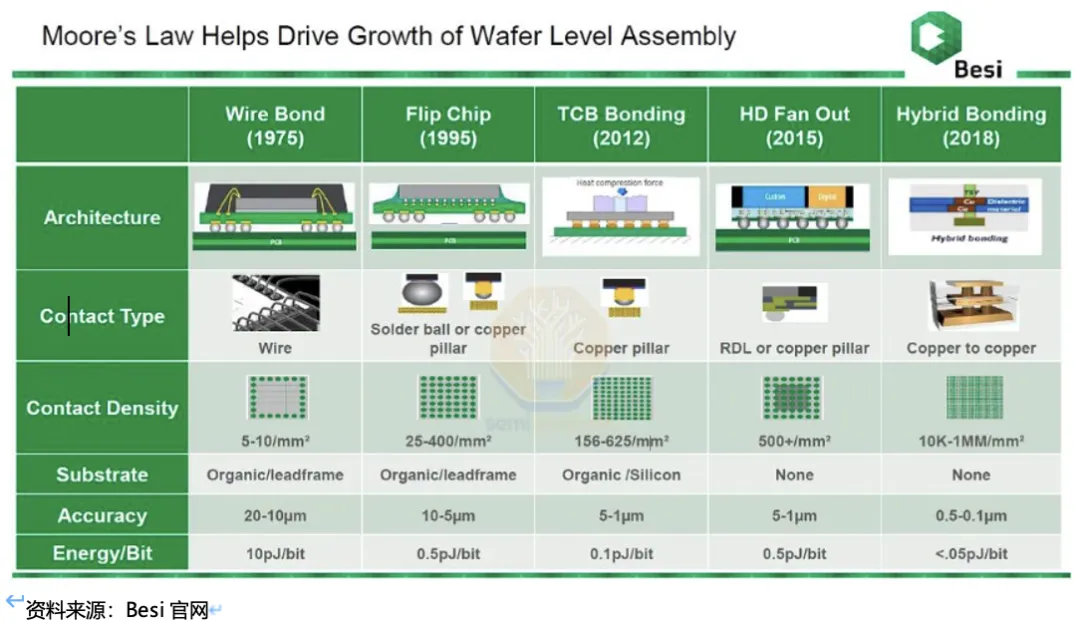

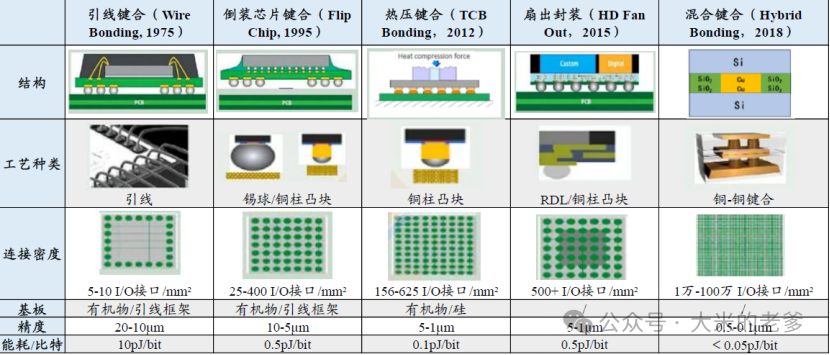

微電子技術的演進始終圍繞微型化、高效性、集成度與低成本四大核心驅動力展開,封裝技術亦隨之從傳統TSOP、CSP、WLP逐步邁向系統級集成的PoP、SiP及3D IC方向,最終目標是在最小面積內實現系統功能的最大化。

2025-10-21 17:38:28 1749

1749

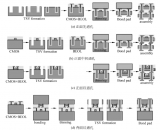

在半導體封裝工藝中,芯片鍵合(Die Bonding)是指將晶圓芯片固定到封裝基板上的關鍵步驟。鍵合工藝可分為傳統方法和先進方法:傳統方法包括芯片鍵合(Die Bonding)和引線鍵合(Wire

2025-10-21 17:36:16 2052

2052

在功率半導體封裝領域,晶圓級芯片規模封裝技術正引領著分立功率器件向更高集成度、更低損耗及更優熱性能方向演進。

2025-10-21 17:24:13 3873

3873

摘要:本文研究白光干涉儀在肖特基二極管晶圓深溝槽 3D 輪廓測量中的應用,分析其工作原理及適配深溝槽結構的技術優勢,通過實際案例驗證其測量精度,為肖特基二極管晶圓深溝槽制造的質量控制與性能優化提供

2025-10-20 11:13:27 279

279

一、引言

12 英寸及以上的大尺寸玻璃晶圓在半導體制造、顯示面板、微機電系統等領域扮演著關鍵角色 。總厚度偏差(TTV)的均勻性直接影響晶圓后續光刻、鍵合、封裝等工藝的精度與良率 。然而,隨著晶圓

2025-10-17 13:40:01 399

399

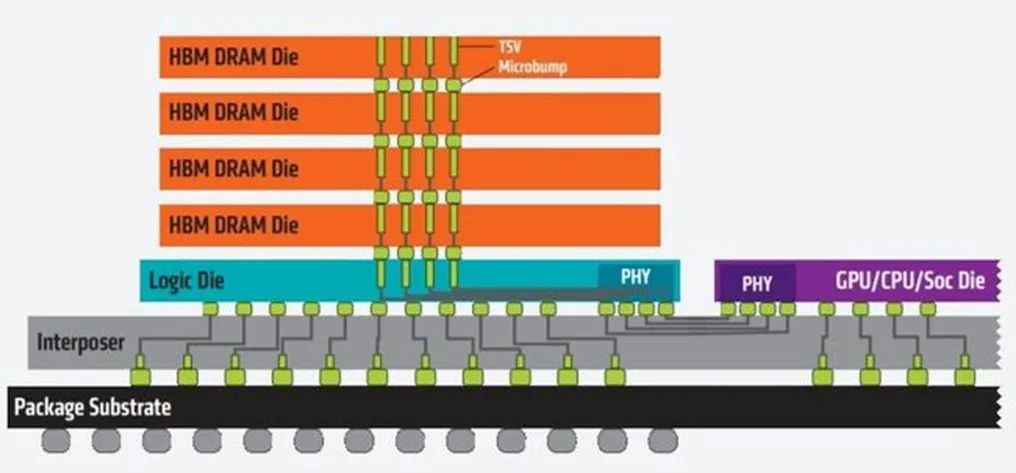

3D封裝架構主要分為芯片對芯片集成、封裝對封裝集成和異構集成三大類,分別采用TSV、TCB和混合鍵合等先進工藝實現高密度互連。

2025-10-16 16:23:32 1548

1548

一、引言

隨著半導體技術向小型化、高性能化發展,3D 集成封裝技術憑借其能有效提高芯片集成度、縮短信號傳輸距離等優勢,成為行業發展的重要方向 。玻璃晶圓因其良好的光學透明性、化學穩定性及機械強度

2025-10-14 15:24:56 316

316

硅通孔(TSV)技術借助硅晶圓內部的垂直金屬通孔,達成芯片間的直接電互連。相較于傳統引線鍵合等互連方案,TSV 技術的核心優勢在于顯著縮短互連路徑(較引線鍵合縮短 60%~90%)與提升互連密度

2025-10-14 08:30:00 6439

6439

上市周期,以滿足 AI 和 HPC 客戶的應用需求。Cadence 與臺積公司在 AI 驅動的 EDA、3D-IC、IP 及光子學等領域展開了緊密合作,推出全球領先的半導體產品。

2025-10-13 13:37:59 2087

2087 我將從超薄玻璃晶圓 TTV 厚度測量面臨的問題出發,結合其自身特性與測量要求,分析材料、設備和環境等方面的技術瓶頸,并針對性提出突破方向和措施。

超薄玻璃晶圓(

2025-09-28 14:33:22 337

337

隨著半導體產品高性能、輕薄化發展,封裝技術作為連接芯片與外界環境的橋梁,其重要性日益凸顯。在眾多封裝技術中,熱壓鍵合(Thermal Compression Bonding)工藝技術以其獨特的優勢

2025-09-25 17:33:09 908

908

在先進封裝中, Hybrid bonding( 混合鍵合)不僅可以增加I/O密度,提高信號完整性,還可以實現低功耗、高帶寬的異構集成。它是主要3D封裝平臺(如臺積電的SoIC、三星的X-Cube

2025-09-17 16:05:36 1467

1467

全新EVG?40 D2W套刻精度計量系統實現每顆芯片100%測量,吞吐量達行業基準15倍 2025年9月8日,奧地利圣弗洛里安 ——全球領先的先進半導體工藝解決方案與技術提供商EV 集團(EVG

2025-09-11 15:22:57 708

708 。然而,當系統級集成需求把 3D 封裝/3D IC 技術推向 WLCSP 時,傳統方案——引線鍵合堆疊、PoP、TSV 硅通孔——因工藝窗口、CTE 失配及成本敏感性而顯著受限。

2025-08-28 13:46:34 2892

2892

在晶圓加工流程中,早期檢測宏觀缺陷是提升良率與推動工藝改進的核心環節,這一需求正驅動檢測技術與晶圓測試圖分析領域的創新。宏觀缺陷早期檢測的重要性與挑戰在晶圓層面,一個宏觀缺陷可能影響多個芯片,甚至在

2025-08-19 13:48:23 1116

1116

隨著半導體器件向更精密的封裝方案持續演進,傳統光學檢測技術正逐漸觸及物理與計算的雙重邊界。對2.5D/3D集成、混合鍵合及晶圓級工藝的依賴日益加深,使得缺陷檢測的一致性與時效性面臨嚴峻挑戰——若無

2025-08-19 13:47:10 816

816

2.5D/3D封裝技術作為當前前沿的先進封裝工藝,實現方案豐富多樣,會根據不同應用需求和技術發展動態調整,涵蓋芯片減薄、芯片鍵合、引線鍵合、倒裝鍵合、TSV、塑封、基板、引線框架、載帶、晶圓級薄膜

2025-08-05 15:03:08 2805

2805

摘要

本文圍繞半導體晶圓研磨工藝,深入剖析聚氨酯研磨墊磨損狀態與晶圓 TTV 均勻性的退化關系,探究其退化機理,并提出相應的預警方法,為保障晶圓研磨質量、優化研磨工藝提供理論與技術支持。

引言

在

2025-08-05 10:16:02 685

685

?融合)與中間層鍵合(如高分子、金屬)兩類,其溫度控制、對準精度等參數直接影響芯片堆疊、光電集成等應用的性能與可靠性,本質是通過突破納米級原子間距實現微觀到宏觀的穩固連接。

2025-08-01 09:25:59 1760

1760

我將圍繞超薄晶圓切割液性能優化與 TTV 均勻性保障技術展開,從切割液對 TTV 影響、現有問題及優化技術等方面撰寫論文。

超薄晶圓(

2025-07-30 10:29:56 326

326

一萬億晶體管”目標的關鍵跳板。當前先進封裝雖提高了I/O密度,但愈發復雜的異構設計與Chiplet架構對I/O數量、延遲提出了更高要求,以滿足AI、5G和高性能計算等應用。混合鍵合互連技術正成為關鍵突破口,它可顯著降低能耗、擴大帶寬、優化熱管理,從而助力摩爾定律繼續前行。 Cou

2025-07-28 16:32:54 381

381 晶圓清洗機中的晶圓夾持是確保晶圓在清洗過程中保持穩定、避免污染或損傷的關鍵環節。以下是晶圓夾持的設計原理、技術要點及實現方式: 1. 夾持方式分類 根據晶圓尺寸(如2英寸到12英寸)和工藝需求,夾持

2025-07-23 14:25:43 928

928 厚度不均勻 。切割深度動態補償技術通過實時調整切割深度,為提升晶圓 TTV 厚度均勻性提供了有效手段,深入研究其提升機制與參數優化方法具有重要的現實意義。

二、

2025-07-17 09:28:18 404

404

超薄晶圓厚度極薄,切割時 TTV 均勻性控制難度大。我將從闡述研究背景入手,分析淺切多道切割在超薄晶圓 TTV 均勻性控制中的優勢,再深入探討具體控制技術,完成文章創作。

超薄晶圓(

2025-07-16 09:31:02 469

469

我將從超薄晶圓淺切多道切割技術的原理、TTV 均勻性控制的重要性出發,結合相關研究案例,闡述該技術的關鍵要點與應用前景。

超薄晶圓(

2025-07-15 09:36:03 486

486

電子發燒友網為你提供()Silicon PIN 二極管、封裝和可鍵合芯片相關產品參數、數據手冊,更有Silicon PIN 二極管、封裝和可鍵合芯片的引腳圖、接線圖、封裝手冊、中文資料、英文資料

2025-07-14 18:32:06

一、引言

在半導體制造中,晶圓總厚度變化(TTV)均勻性是決定芯片性能與良品率的關鍵因素,而切割過程產生的應力會導致晶圓變形,進一步惡化 TTV 均勻性。淺切多道工藝作為一種先進的晶圓切割技術,在

2025-07-14 13:57:45 465

465

所謂混合鍵合(hybrid bonding),指的是將兩片以上不相同的Wafer或Die通過金屬互連的混合鍵合工藝,來實現三維集成,在Hybrid Bonding前,2D,2.5D及3D封裝都是采用

2025-07-10 11:12:17 2714

2714

電子發燒友網為你提供()硅限幅器二極管、封裝和可鍵合芯片相關產品參數、數據手冊,更有硅限幅器二極管、封裝和可鍵合芯片的引腳圖、接線圖、封裝手冊、中文資料、英文資料,硅限幅器二極管、封裝和可鍵合芯片真值表,硅限幅器二極管、封裝和可鍵合芯片管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-07-09 18:32:29

超薄晶圓因其厚度極薄,在切割時對振動更為敏感,易影響厚度均勻性。我將從分析振動對超薄晶圓切割的影響出發,探討針對性的振動控制技術和厚度均勻性保障策略。

超薄晶圓(

2025-07-09 09:52:03 580

580

晶圓級封裝中,錫膏是實現電氣連接與機械固定的核心材料,廣泛應用于凸點制作、植球工藝及芯片 - 基板互連等關鍵環節。主流采用 SAC 系、Sn-Cu 系、Sn-Bi 系等無鉛錫膏,需滿足高精度印刷、優異潤濕性、高可靠性及低殘留等嚴苛要求。

2025-07-02 11:16:52 1059

1059

電子發燒友網綜合報道 半導體封裝技術正經歷從傳統平面架構向三維立體集成的革命性躍遷,其中銅 - 銅混合鍵合技術以其在互連密度、能效優化與異構集成方面的突破,成為推動 3D 封裝發展的核心

2025-06-29 22:05:13 1519

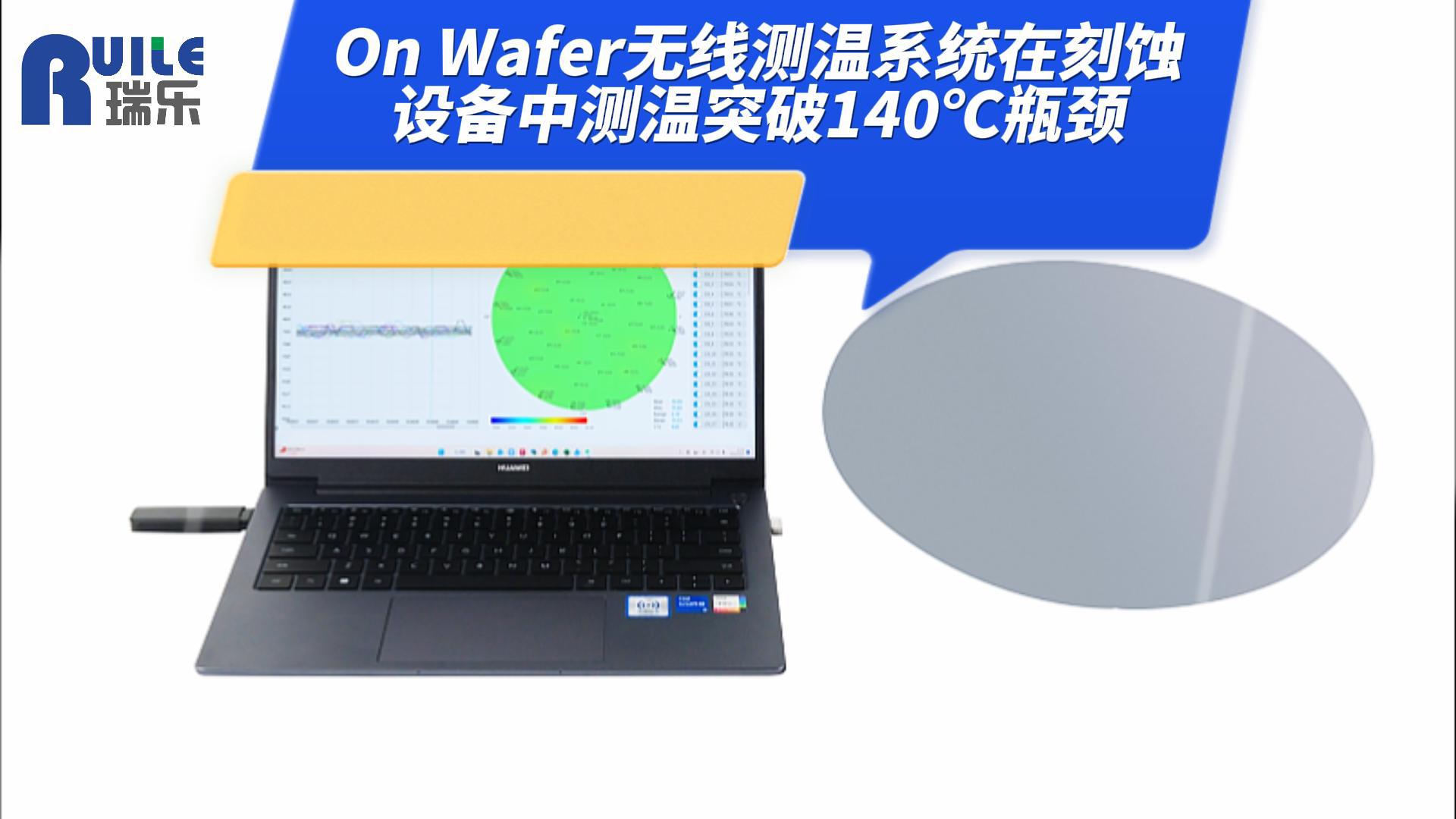

1519 的工藝參數。【應用范圍】物理氣相沉積 (PVD)、原子層沉積 (ALD)、化學氣相沉積 (CVD)、退火爐、去膠設備、晶圓臨時鍵合、涂膠

2025-06-27 10:16:41

晶圓級扇出封裝(FO-WLP)通過環氧樹脂模塑料(EMC)擴展芯片有效面積,突破了扇入型封裝的I/O密度限制,但其技術復雜度呈指數級增長。

2025-06-05 16:25:57 2143

2143

在微電子行業飛速發展的背景下,封裝技術已成為連接芯片創新與系統應用的核心紐帶。其核心價值不僅體現于物理防護與電氣/光學互聯等基礎功能,更在于應對多元化市場需求的適應性突破,本文著力介紹晶圓級扇入封裝,分述如下。

2025-06-03 18:22:20 1054

1054

所謂混合鍵合(hybrid bonding),指的是將兩片以上不相同的Wafer或Die通過金屬互連的混合鍵合工藝,來實現三維集成,在Hybrid Bonding前,2D,2.5D及3D封裝都是采用

2025-06-03 11:35:24 2031

2031

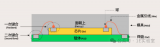

屬直接鍵合的先進封裝技術,其核心目標是實現芯片間高密度、低電阻的垂直互聯。 ? 在工藝過程中,需要經過對準和鍵合、后鍵合處理等幾個流程。在對晶圓表面進行化學機械拋光(CMP)和清洗之后,通過光學或電子束對準系統實現亞微米級(通常 ?

2025-06-03 09:02:18 2691

2691 通過退火優化和應力平衡技術控制。

3、彎曲度(Bow) 源于材料與工藝的對稱性缺陷,對多層堆疊和封裝尤為敏感,需在晶體生長和鍍膜工藝中嚴格調控。

在先進制程中,三者共同決定了晶圓的幾何完整性,是良率提升

2025-05-28 16:12:46

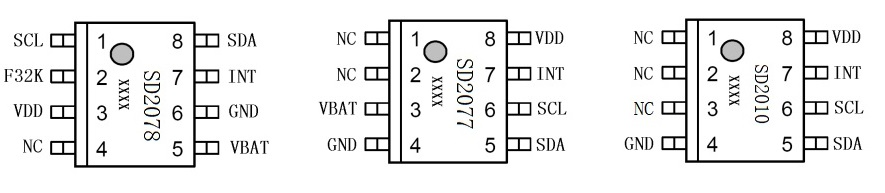

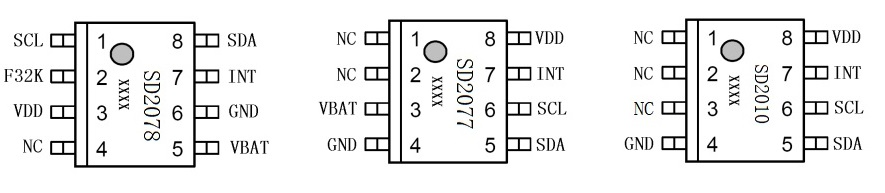

鴻合智遠|興威帆電子:內置晶振、小封裝的實時時鐘IC-SD

2025-05-28 10:01:36 670

670

WD4000系列Wafer晶圓厚度量測系統采用白光光譜共焦多傳感器和白光干涉顯微測量雙向掃描技術,完成非接觸式掃描并建立表面3D層析圖像,實現Wafer厚度、翹曲度、平面度、線粗糙度、總體厚度變化

2025-05-27 13:54:33

關鍵詞:鍵合晶圓;TTV 質量;晶圓預處理;鍵合工藝;檢測機制 一、引言 在半導體制造領域,鍵合晶圓技術廣泛應用于三維集成、傳感器制造等領域。然而,鍵合過程中諸多因素會導致晶圓總厚度偏差(TTV

2025-05-26 09:24:36 850

850

電池的集成。這一里程碑為封裝內儲能解決方案鋪平了道路,助力實現更高效、緊湊且可靠的系統級封裝(SiP)設計。 革新儲能與先進封裝 這一突破性創新標志著SiP技術的重大飛躍。通過在晶圓層面嵌入ITEN的高性能固態電池,ITEN與A*STAR IME成功展示了利用先進封裝直接集成非易失

2025-05-22 13:08:59 560

560 使用直接晶圓到晶圓鍵合來垂直堆疊芯片,可以將信號延遲降到可忽略的水平,從而實現更小、更薄的封裝,同時有助于提高內存/處理器的速度并降低功耗。目前,晶圓堆疊和芯片到晶圓混合鍵合的實施競爭異常激烈,這被

2025-05-22 11:24:18 1405

1405

常規IC封裝需經過將晶圓與IC封裝基板焊接,再將IC基板焊接至普通PCB的復雜過程。與之不同,WLP基于IC晶圓,借助PCB制造技術,在晶圓上構建類似IC封裝基板的結構,塑封后可直接安裝在普通PCB

2025-05-14 11:08:16 2420

2420

多芯片封裝在現代半導體領域至關重要,主要分為平面多芯片封裝和多芯片堆疊封裝。多芯片堆疊封裝又細分為多芯片3D堆疊引線鍵合封裝、3D堆疊引線鍵合和倒裝異質封裝、3DTSV堆疊倒裝封裝等。

2025-05-14 10:39:54 1846

1846

我們看下一個先進封裝的關鍵概念——晶圓級封裝(Wafer Level Package,WLP)。

2025-05-14 10:32:30 1532

1532

英寸晶圓厚度約為670微米,8英寸晶圓厚度約為725微米,12英寸晶圓厚度約為775微米。盡管芯片功能層的制備僅涉及晶圓表面幾微米范圍,但完整厚度的晶圓更有利于保障復雜工藝的順利進行。直至芯片前制程完成后,晶圓才會進入封裝環節進行減薄處理。

2025-05-09 13:55:51 1975

1975 圓片級封裝(WLP),也稱為晶圓級封裝,是一種直接在晶圓上完成大部分或全部封裝測試程序,再進行切割制成單顆組件的先進封裝技術 。WLP自2000年左右問世以來,已逐漸成為半導體封裝領域的主流技術,深刻改變了傳統封裝的流程與模式。

2025-05-08 15:09:36 2067

2067

隨著半導體工藝復雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術通過直接在未封裝晶圓上施加加速應力,實現快速

2025-05-07 20:34:21

Entegris 先進技術應用資深處長陳柏嘉在SEMICON China 2025期間舉辦的先進材料論壇,發表了題為《整合式微污染控制在半導體制程中的關鍵角色》的主題演講。

2025-04-30 16:35:54 847

847 在微組裝工藝中,化學鍍鎳鈀金(ENEPIG)工藝因其優異的抗“金脆”和“黑焊盤”性能,成為高可靠性電子封裝的關鍵技術。然而,其鍵合強度的長期可靠性仍需系統驗證。本文科準測控小編將基于Alpha

2025-04-29 10:40:25 945

945

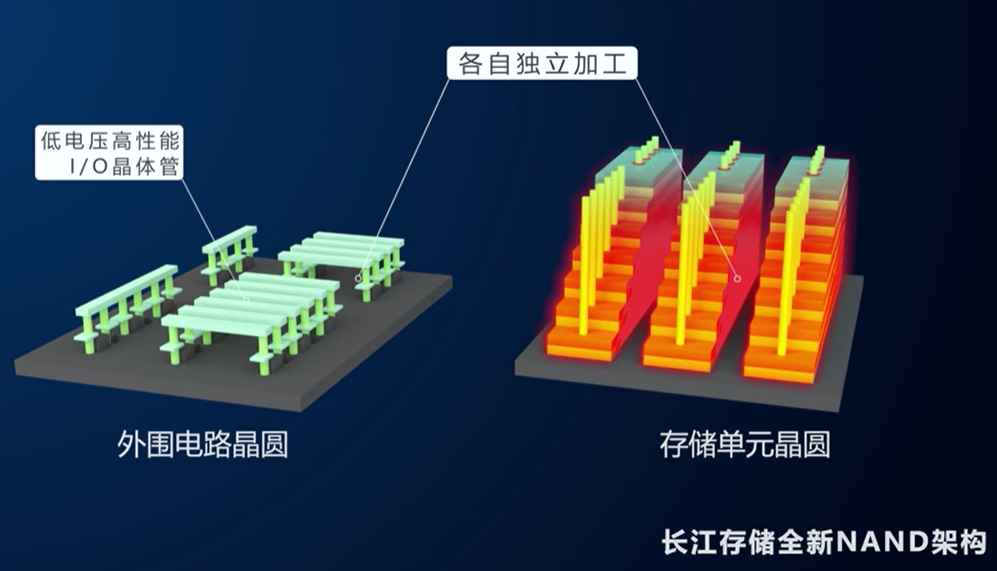

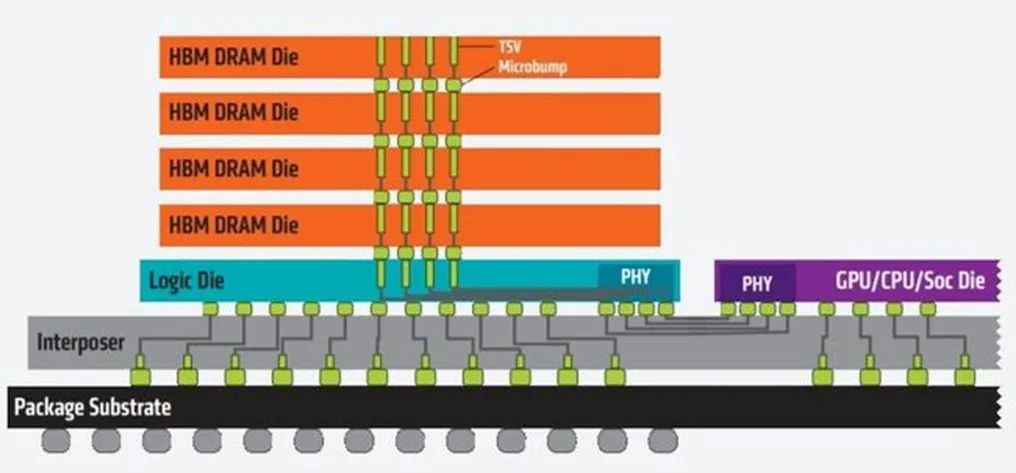

客戶對HBM的要求為增加帶寬、提高功率效率、提高集成度。混合鍵合就是可以滿足此類需求的技術。 ? 混合鍵合技術預計不僅可應用于HBM,還可應用于3D DRAM和NAND Flash。SK海力士副總裁姜志浩(音譯)表示,“目前的做法是分別創建DRAM單元區域和外圍區域,

2025-04-17 00:05:00 1060

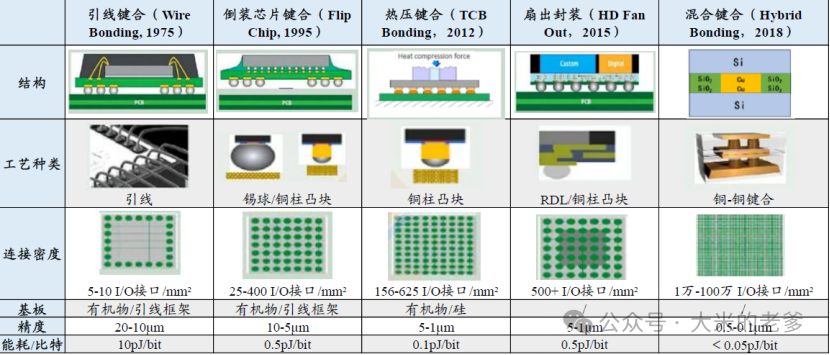

1060 芯片封裝作為半導體制造的核心環節,承擔著物理保護、電氣互連和散熱等關鍵功能。其中,鍵合技術作為連接裸芯片與外部材料的橋梁,直接影響芯片的性能與可靠性。當前,芯片封裝領域存在引線鍵合、倒裝芯片、載帶

2025-04-11 14:02:25 2627

2627

在摩爾定律逼近物理極限的當下,先進封裝技術正成為半導體行業突破性能瓶頸的關鍵路徑。以系統級封裝(SiP)、晶圓級封裝(WLP)、3D堆疊、Chiplet異構集成為代表的顛覆性方案,正重新定義芯片性能

2025-04-10 14:36:31 1188

1188

芯片封裝是半導體制造的關鍵環節,承擔著為芯片提供物理保護、電氣互連和散熱的功能,這其中的鍵合技術(Bonding)就是將晶圓芯片固定于基板上。

2025-04-10 10:15:38 2838

2838

近日,NVIDIA 宣布了 NVIDIA RTX 神經網絡渲染技術的突破性增強功能。NVIDIA 與微軟合作,將在 4 月的 Microsoft DirectX 預覽版中增加神經網絡著色技術,讓開

2025-04-07 11:33:36 971

971 在芯片裸片制造完成后,芯片制造廠需要把其上不滿了裸片的晶圓送到芯片封測廠進行切割和封裝,并對芯片進行功能、性能和可靠性測試,最后在芯片封裝殼上打印公司商標、芯片型號等。至此,芯片的生產過程才算全部

2025-04-04 16:01:02

此前,2025年3月26日至28日,作為中國半導體產業鏈的重要參與者,太極半導體(蘇州)有限公司(以下簡稱:太極半導體)攜最新封測技術亮相SEMICON China 2025,以“聚勢啟新章、共鑄芯紀元”為主題,與全球伙伴共探行業新機遇。

2025-04-02 17:16:50 1343

1343 此前,3月26日至28日,全球半導體行業盛會SEMICON/FPD China 2025在上海隆重舉辦。開幕式上,長電科技董事、首席執行長,SEMI全球董事鄭力發表主題演講《開放協同,共建半導體產業新生態》。

2025-04-02 10:16:42 1183

1183 近日,為期三天的半導體盛會——SEMICON China 2025在上海新國際博覽中心圓滿落幕。廣立微全面展示了其在EDA軟件、測試設備及良率提升的綜合創新能力,贏得了業內的高度關注與贊譽。

2025-04-01 10:46:18 1302

1302

集成與電能管理四大技術板塊精彩亮相。通過全系列封裝設備矩陣及行業首發解決方案,奧芯明向全球展示了在封裝領域的突破性進展和本土化成果,彰顯了公司以創新提質、助力中國半導體產業高質量發展的堅定承諾與信心。 四大技術矩陣驚艷亮相 本屆展

2025-03-31 15:34:53 889

889

全球規模最大、規格最高、最具影響力及最新技術熱點全覆蓋的半導體“嘉年華”—SEMICON China 2025于近日在上海正式拉開帷幕,同期舉辦20多場會議和活動,匯聚全球芯片設計、制造、封測、設備、材料、光伏、顯示等全產業鏈芯力量。

2025-03-31 11:30:09 953

953 近日,全球矚目的半導體“嘉年華”——SEMICON/FPD China 2025在上海開幕。長電科技董事、首席執行長,SEMI全球董事鄭力出席開幕式并發表主題演講“開放協同,共建半導體產業新生態”。

2025-03-31 10:25:37 1016

1016 隨著輕型可穿戴設備和先進數字終端設備的需求不斷增長,傳統晶圓逐漸無法滿足多層先進封裝(2.5D/3D堆疊)的需求。它們體積較大、重量重、且在高溫和大功率環境下表現欠佳,難以適應行業的快速發展。如今

2025-03-28 20:13:59 790

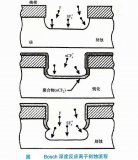

790 在SEMICON China 2025展會期間,中微半導體設備(上海)股份有限公司(以下簡稱“中微公司”,股票代碼“688012.SH”)宣布其自主研發的12英寸晶圓邊緣刻蝕設備Primo

2025-03-28 09:21:19 1192

1192 隨著半導體工藝復雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術通過直接在未封裝晶圓上施加加速應力,實現快速、低成本的可靠性評估,成為工藝開發的關鍵工具。

2025-03-26 09:50:16 1548

1548

每年一度的SEMICON China將于2025年3月26-28日在上海新國際博覽中心舉辦。同時,中國規模最大、最全面的年度半導體技術盛會——集成電路科學技術大會(CSTIC)2025也將于3月24-25日在上海國際會議中心召開。

2025-03-24 09:35:11 1340

1340 芯片封裝是半導體制造的關鍵環節,承擔著為芯片提供物理保護、電氣互連和散熱的功能,這其中的鍵合技術就是將裸芯片與外部材料連接起來的方法。鍵合可以通俗的理解為接合,對應的英語表達是Bonding,音譯

2025-03-22 09:45:31 5448

5448

環球儀器與母公司臺達電子將在3月26-28日于上海舉行的SEMICON China 2025展會上,展示五大半導體自動化解決方案,提高生產效率。

2025-03-21 10:06:13 941

941 全新強力鍵合腔室設計,賦能更大尺寸晶圓高均勻性鍵合與量產良率提升 2025年3月18日,奧地利圣弗洛里安 —全球領先的半導體創新工藝解決方案和專業知識提供商,為前沿和未來的半導體設計和芯片集成

2025-03-20 09:07:58 889

889

SEMICON China 2025 將于3月26-28日在 上海新國際博覽中心隆重登場。作為全球半導體行業的頂尖盛會,展會匯聚超過1000家全球知名企業,覆蓋芯片設計、制造、封裝測試、設備、材料等全產業鏈,展覽面積達90000平方米,同期舉辦20多場高質量論壇和活動。

2025-03-13 11:37:45 1099

1099 金絲鍵合主要依靠熱超聲鍵合技術來達成。熱超聲鍵合融合了熱壓鍵合與超聲鍵合兩者的長處。通常情況下,熱壓鍵合所需溫度在300℃以上,而在引入超聲作用后,熱超聲鍵合所需溫度可降至200℃以下。如此一來

2025-03-12 15:28:38 3656

3656

2025年3月11日,香港——中國半導體鍵合集成技術領域的領先企業青禾晶元半導體科技(集團)有限責任公司(簡稱“青禾晶元”)宣布,正式推出全球首臺C2WW2W雙模式混合鍵合設備SAB8210CWW上

2025-03-12 13:43:56 1036

1036

3月26-28日,2025 SEMICON China即將在上海新國際博覽中心隆重開幕。屆時,概倫電子將攜應用驅動的半導體參數測試平臺和解決方案亮相,現場還將全新發布先進寬帶噪聲分析儀9812HF,刷新半導體測試標準。誠邀您蒞臨概倫展臺,共同見證半導體量測技術的突破創新。

2025-03-11 15:58:28 821

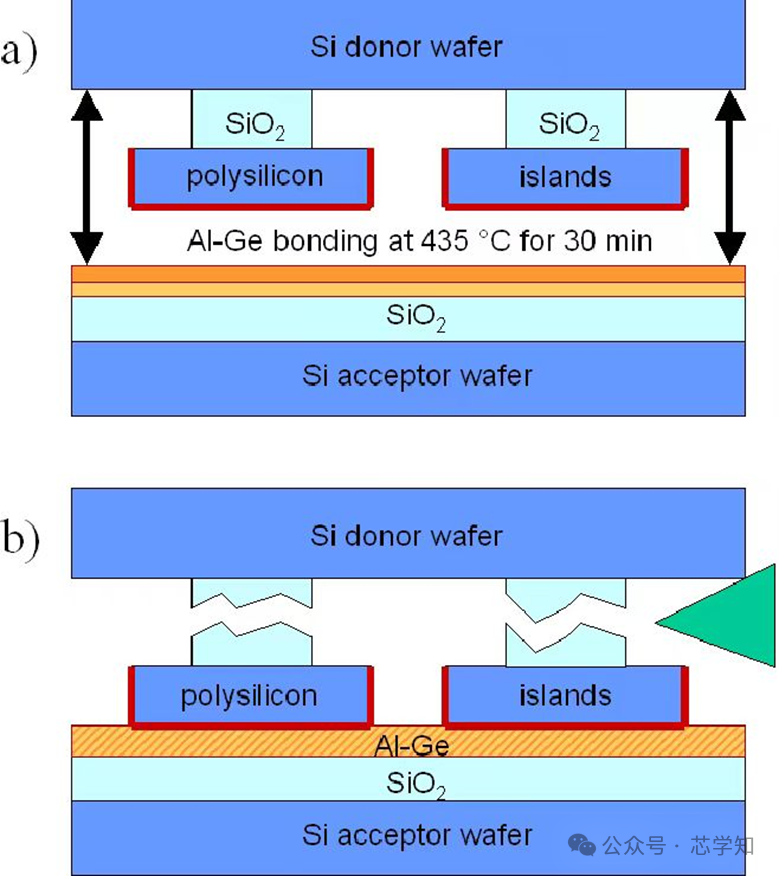

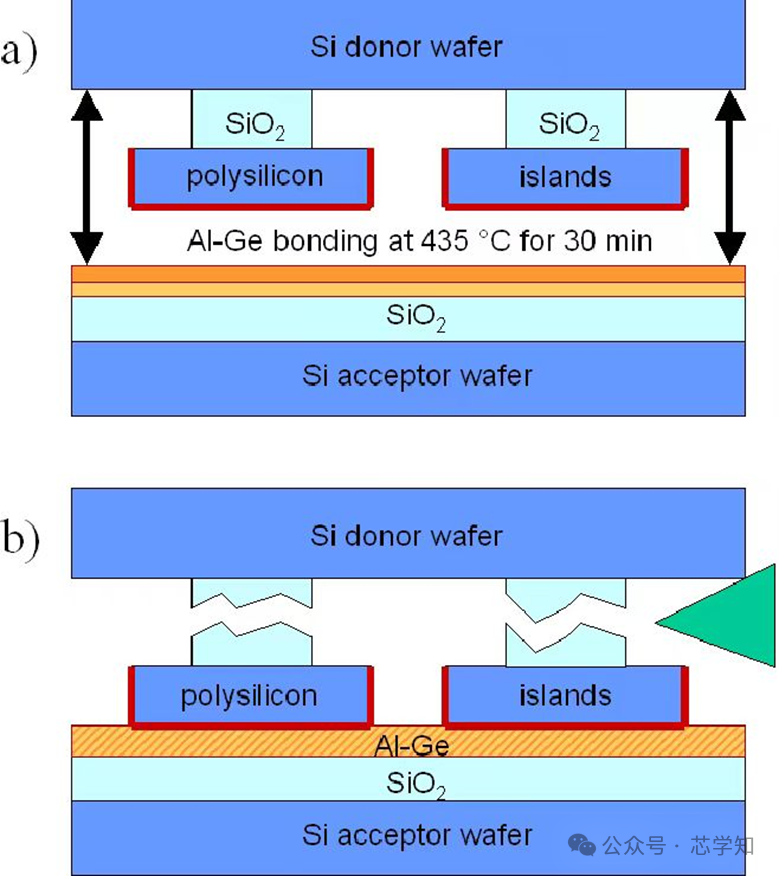

821 鍵合技術主要分為直接鍵合和帶有中間層的鍵合。直接鍵合如硅硅鍵合,陽極鍵合等鍵合條件高,如高溫、高壓等。而帶有中間層的鍵合,所需的溫度更低,壓力也更小。帶金屬的中間層鍵合技術主要包括共晶鍵合、焊料鍵合、熱壓鍵合和反應鍵合等。本文主要對共晶鍵合進行介紹。

2025-03-04 17:10:52 2627

2627

金屬共晶鍵合是利用金屬間的化學反應,在較低溫度下通過低溫相變而實現的鍵合,鍵合后的金屬化合物熔點高于鍵合溫度。該定義更側重于從材料科學的角度定義。

2025-03-04 14:14:41 1921

1921

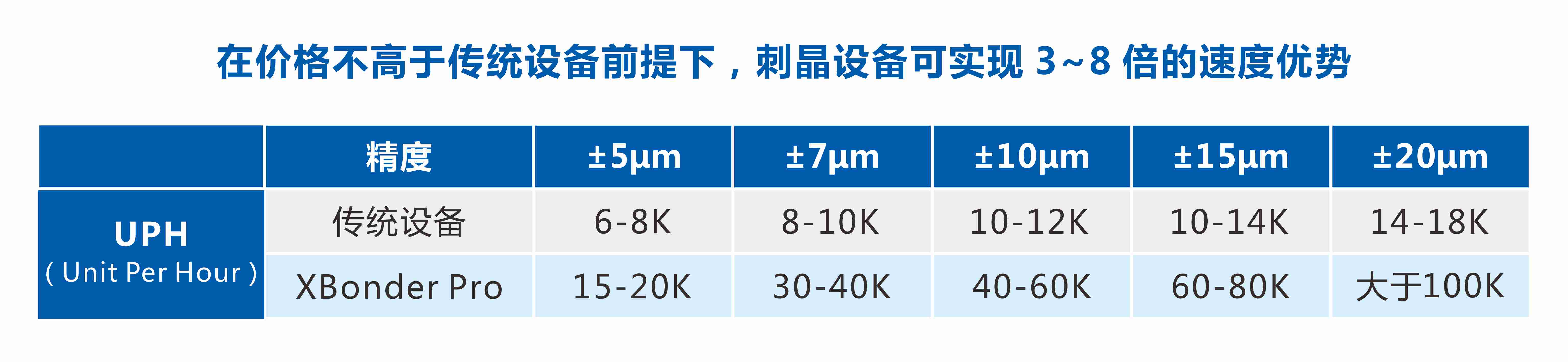

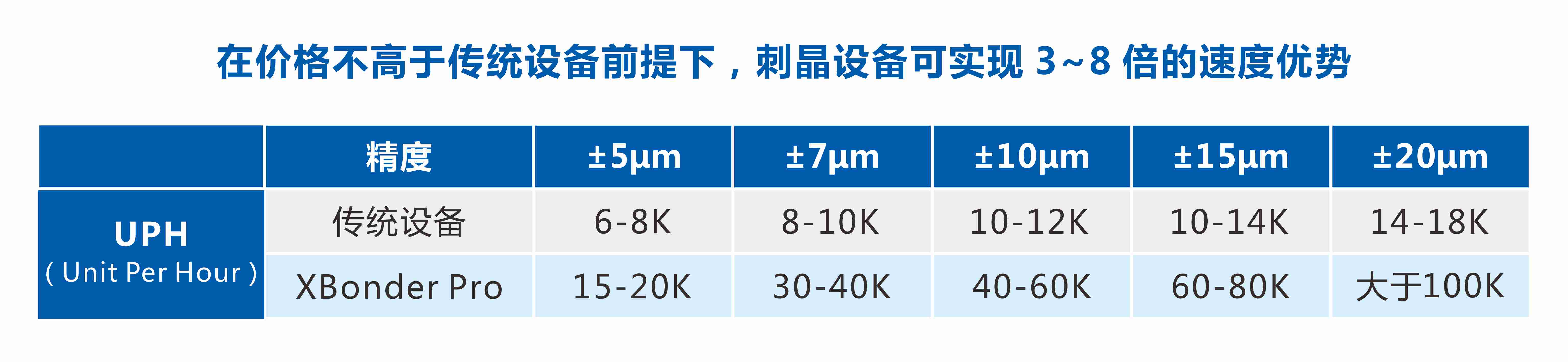

經過半年的測試,普萊信智能和某頂級封裝廠就其巨量轉移式板級封裝設備(FOPLP)設備XBonder Pro達成戰略合作協議,這將是巨量轉移技術在IC封裝領域第一次規模化的應用,將掀起晶圓級封裝和板級

2025-03-04 11:28:05 1186

1186

隨著半導體技術的飛速發展,晶圓級封裝(WLP)作為先進封裝技術的重要組成部分,正逐漸成為集成電路封裝的主流趨勢。在晶圓級封裝過程中,Bump工藝扮演著至關重要的角色。Bump,即凸塊,是晶圓級封裝中

2025-03-04 10:52:57 4978

4978

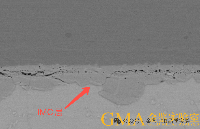

銅引線鍵合由于在價格、電導率和熱導率等方面的優勢有望取代傳統的金引線鍵合, 然而 Cu/Al 引線鍵合界面的金屬間化合物 (intermetallic compounds, IMC) 的過量生長將增大接觸電阻和降低鍵合強度, 從而影響器件的性能和可靠性。

2025-03-01 15:00:09 2398

2398

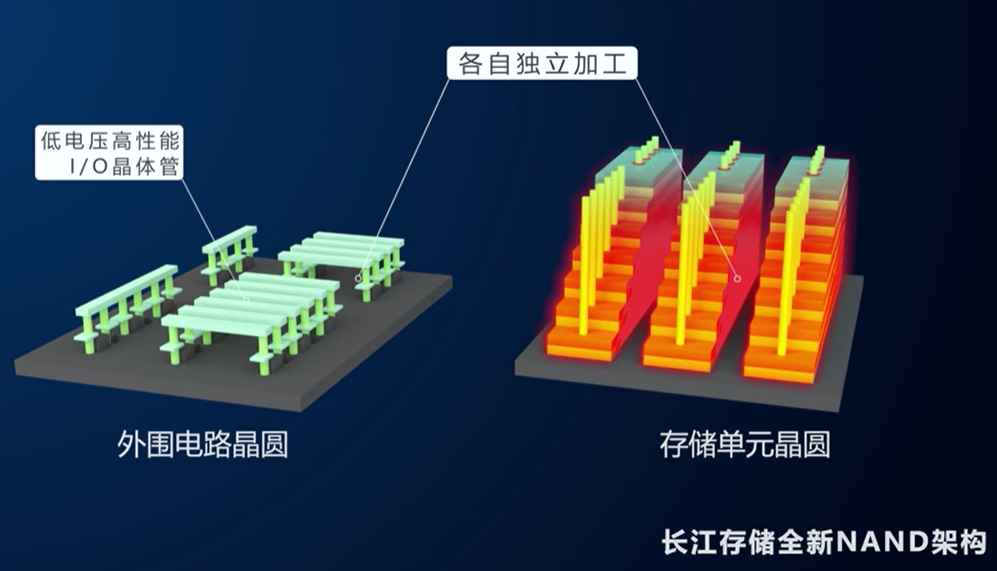

電子發燒友網綜合報道,據韓媒報道,三星近日與長江存儲簽署了3D NAND混合鍵合專利許可協議,從第10代V-NAND開始,將使用長江存儲的專利技術,特別是在“混合鍵合”技術方面。 ? W2W技術是指

2025-02-27 01:56:00 1037

1037

3D-IC通過采用TSV(Through-Silicon Via,硅通孔)技術,實現了不同層芯片之間的垂直互連。這種設計顯著提升了系統集成度,同時有效地縮短了互連線的長度。這樣的改進不僅降低了信號傳輸的延時,還減少了功耗,從而全面提升了系統的整體性能。

2025-02-21 15:57:02 2460

2460

(InFO) 封裝這樣的 3D 扇出封裝方法,則更側重于手機等大規模消費應用。此外,所有主流設計公司、晶圓代工廠和封測代工廠 (OSAT) 都在投資新一代技術——使用硅通孔 (TSV) 和混合鍵合的真正裸片堆疊。

2025-02-20 11:36:56 1271

1271

的關鍵技術之一,它不僅能夠保護MEMS器件免受外部環境的影響,還能提高器件的性能和可靠性。Au-Sn共晶鍵合技術作為一種先進的封裝技術,在MEMS氣密性封裝中展現出

2025-01-23 10:30:52 2886

2886

扇出型晶圓級中介層封裝( FOWLP)以及封裝堆疊(Package-on-Package, PoP)設計在移動應用中具有許多優勢,例如低功耗、短信號路徑、小外形尺寸以及多功能的異構集成。此外,它還

2025-01-22 14:57:52 4507

4507

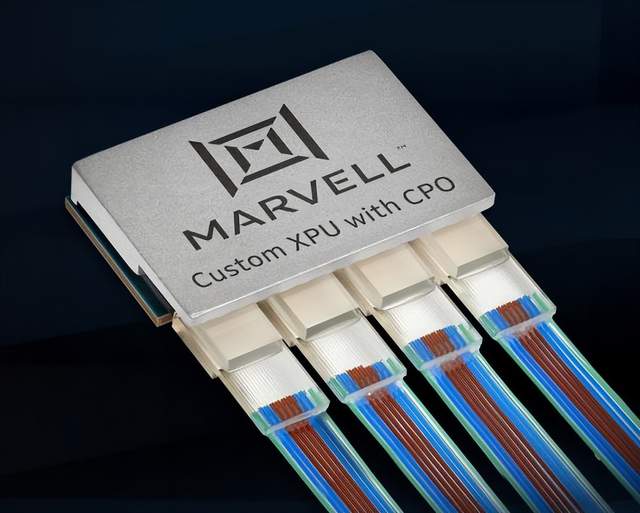

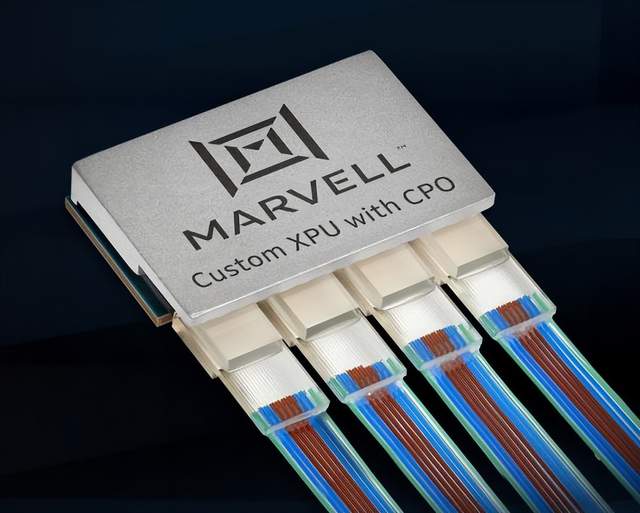

突破性CPO架構為人工智能領域的發展注入新的活力,也促使我們深入探究CPO技術給互連產品究竟會帶來怎樣的影響。 1 月 6 日,美國芯片大廠Marvell宣布重大突破,將共封裝光學架構(CPO

2025-01-17 15:00:12 1348

1348

。 2.5D封裝將die拉近,并通過硅中介連接。3D封裝實際上采用2.5D封裝,進一步垂直堆疊die,使die之間的連接更短。通過這種方式直接集成IC,IC間通信接口通常可以減少或完全消除。這既可以提高性能,又可以減輕重量和功耗。 這種封裝的復雜性需要新穎的封裝和測試技術。 了解2.5D封裝與3

2025-01-14 10:41:33 2902

2902

???? 本文主要介紹功率器件晶圓測試及封裝成品測試。?????? ? 晶圓測試(CP)???? 如圖所示為典型的碳化硅晶圓和分立器件電學測試的系統,主要由三部分組成,左邊為電學檢測探針臺阿波羅

2025-01-14 09:29:13 2358

2358

混合鍵合技術(下) 先進封裝技術(Semiconductor Advanced Packaging) - 3 Chiplet 異構集成(上) 先進封裝技術(Semiconductor

2025-01-08 11:17:01 3031

3031

隨著半導體技術的飛速發展,晶圓級封裝(Wafer Level Packaging, WLP)作為一種先進的封裝技術,正逐漸在集成電路封裝領域占據主導地位。晶圓級封裝技術以其高密度、高可靠性、小尺寸

2025-01-07 11:21:59 3190

3190

生電子共享或原子的相互擴散,從而使兩種金屬間實現原子量級上的鍵合。圖1在IC封裝中,芯片和引線框架(基板)的連接為電源和信號的分配提供了電路連接。有三種方式實現內部連

2025-01-06 12:24:10 1964

1964

電子發燒友App

電子發燒友App

評論