亮點

Cadence 的 AI 設計流程支持臺積公司的 N2 和 A16技術

Cadence 3D-IC 解決方案全面兼容最新的 TSMC 3DFabric裸片堆疊配置和先進封裝能力

基于臺積公司 N3P 的設計就緒 IP(包括 HBM4 和 LPDDR6/5x)賦能下一代 AI 基礎設施

中國上海,2025 年 10 月 10 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布在芯片設計自動化和 IP 領域取得重大進展,這一成果得益于其與臺積公司的長期合作關系,雙方共同開發先進的設計基礎設施,縮短產品上市周期,以滿足 AI 和 HPC 客戶的應用需求。Cadence 與臺積公司在 AI 驅動的 EDA、3D-IC、IP 及光子學等領域展開了緊密合作,推出全球領先的半導體產品。

Cadence 攜手臺積公司,采用CadenceInnovusImplementation System、QuantusExtraction Solution 和 Quantus Field Solver、TempusTiming Solution 和 ECO Option、PegasusVerification System、LiberateCharacterization Portfolio、VoltusIC Power Integrity Solution、GenusSynthesis Solution、VirtuosoStudio 以及 SpectreSimulation Platform開發先進工藝技術的設計基礎設施,涵蓋臺積公司的 N3、N2 和 A16工藝。Cadence 的 AI 芯片與 3D-IC 設計流程現已支持臺積公司的先進 N3、N2 和 A16工藝技術,同時兼容臺積公司 3DFabric 的新技術。此外,Cadence 正與臺積公司合作開發 A14 工藝的 EDA 流程,其首個 PDK 將于今年晚些時候推出。還有幾個新的 Cadence IP 已經過硅驗證,適用于臺積公司 N3P。

Cadence 高級副總裁兼數字與簽核事業部總經理 Chin-Chi Teng 說道:“Cadence 與臺積公司始終致力于為客戶加快和優化先進芯片的設計流程。我們利用 AI 功能、IP 等解決方案為臺積公司的領先技術提供支持,幫助設計人員開發下一代 AI 和 HPC 產品。”

臺積公司生態系統與聯盟管理總監 Aveek Sarkar 表示:“臺積公司攜手 Cadence 等開放創新平臺(OIP) 合作伙伴,共同應對半導體開發中的復雜挑戰,提升 AI 系統的性能和能效。這一持久合作不僅幫助我們的共同客戶加快芯片設計,也推動了 AI 技術的廣泛應用。”

面向臺積公司先進工藝技術的 AI 驅動芯片設計解決方案

Cadence 與臺積公司合作,為共同客戶提供 AI 驅動的設計解決方案,助其在基于臺積公司 N2 的芯片研發中實現最佳功耗、性能和面積(PPA)。臺積公司在 Cadence 數字全流程中啟用了 Cadence JedAI Solution、Cadence CerebrusIntelligent Chip Explorer 的 AI 驅動實現技術以及 Innovus + AI Assistant 的生產力功能。此外,臺積公司已驗證新的 AI 驅動功能,如自動設計規則檢查 (DRC) 違規修復協助,在 AI 芯片開發過程中使用臺積公司 N2 技術縮短設計周期,提高工作效率。

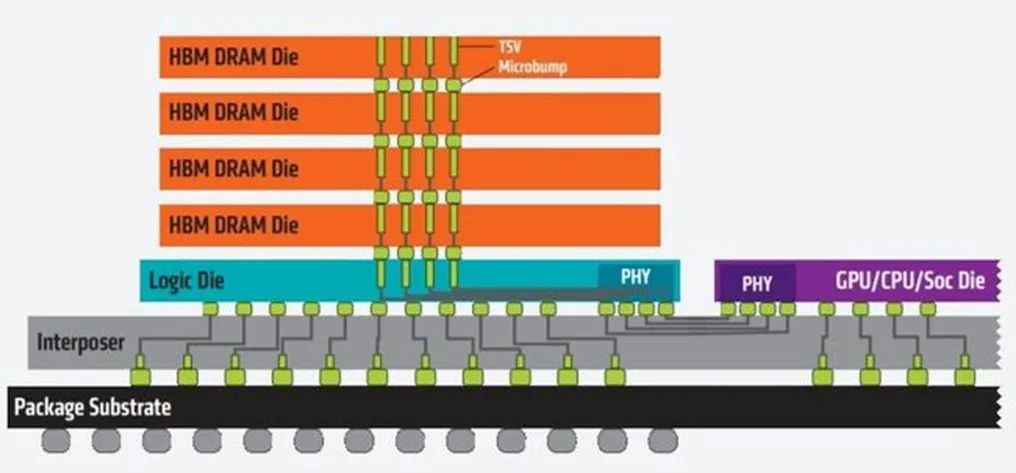

提高 3D-IC 設計生產力

Cadence 3D-IC 解決方案全面支持臺積公司 3DFabric 提供的先進封裝和裸片堆疊配置。最新創新包括凸塊連接自動化功能、多個芯片物理實現與分析以及智能對準標記插入技術。得益于 Cadence Clarity3D Solver、SigrityX 平臺以及 OptimalityIntelligent System Explorer 的 AI 驅動應用,基于 3Dblox 的系統級 SI/PI 分析與優化實現了自動化。采用臺積公司緊湊型通用光子引擎 (TSMC-COUPE) 多波長參考流程的客戶,還可借助 Virtuoso Studio 和 CelsiusThermal Solver,結合臺積公司與 Cadence 共同制定的效率提升方案,包括高效熱仿真技術,降低電性能與光性能下降的風險。

面向臺積公司 N3P 的領先 IP

Cadence 持續推動 AI 與 HPC 技術創新,提供基于臺積公司先進工藝(包括 N3P 工藝技術)、經過硅驗證的前沿 IP 解決方案,助力客戶構建更快速、更高效且可擴展的系統。Cadence IP 滿足下一代 AI LLM、代理式 AI 及其他計算密集型工作負載對內存與互連帶寬容量的需求,為 AI 基礎設施提供支持。基于臺積公司 N3P 工藝的全新 Cadence IP 包括:首款 N3P HBM4 IP、LPDDR6/5X-14.4G 等高速內存接口以及通用型 DDR5 12.8G MRDIMM Gen2 IP,為客戶提供豐富選擇,助力突破限制 AI 計算系統的內存瓶頸。此外,Cadence 在連通領域也處于領先地位,提供傳輸速率達 128Gt/s 的 PCI Express(PCIe) 7.0 IP、面向 AI 基礎設施的 224G SerDes 以及首款支持新興的 AI PC 和小芯片生態系統 eUSB2V2 和 Universal Chiplet Interconnect(UCIe) 32G IP 等產品,彰顯公司致力于為未來工作負載打造節能、可擴展解決方案的承諾。

Cadence 與臺積公司通過 OIP 生態系統賦能 AI 超級周期,縮短從設計到量產的客戶流程,助力提升設計性能與能效表現。

關于 Cadence

Cadence 是 AI 和數字孿生領域的市場領導者,率先使用計算軟件加速從硅片到系統的工程設計創新。我們的設計解決方案基于 Cadence 的 Intelligent System Design戰略,可幫助全球領先的半導體和系統公司構建下一代產品(從芯片到全機電系統),服務超大規模計算、移動通信、汽車、航空航天、工業、生命科學和機器人等領域。2024 年,Cadence 榮登《華爾街日報》評選的“全球最佳管理成效公司 100 強”榜單。Cadence 解決方案提供無限機會。

-

芯片

+關注

關注

462文章

53623瀏覽量

460267 -

Cadence

+關注

關注

68文章

1000瀏覽量

146301 -

AI

+關注

關注

90文章

38414瀏覽量

297701

原文標題:Cadence 攜手臺積公司,推出面向其先進工藝與 3DFabric 的 AI 流程和 IP,推動下一代創新

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AI重塑EDA,3D-IC成關鍵戰場:Cadence的洞察與應變

新思科技旗下Ansys仿真和分析解決方案產品組合已通過臺積公司認證

看點:臺積電2納米N2制程吸引超15家客戶 英偉達擬向OpenAI投資1000億美元

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

Cadence基于臺積電N4工藝交付16GT/s UCIe Gen1 IP

看點:臺積電在美建兩座先進封裝廠 博通十億美元半導體工廠談判破裂

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

西門子與臺積電合作推動半導體設計與集成創新 包括臺積電N3P N3C A14技術

基于TSV的3D-IC關鍵集成技術

Cadence AI芯片與3D-IC設計流程支持臺積公司N2和A16工藝技術

Cadence AI芯片與3D-IC設計流程支持臺積公司N2和A16工藝技術

評論