本文翻譯轉載于:Cadence blog

作者:Vinod Khera

3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產品的新成員。

在后摩爾時代的趨勢下,FinFET 晶體管的體積在 TSMC 3nm 工藝下進一步縮小,進一步采用系統級封裝設計(SiP)。通過結合工藝技術的優勢與Cadence業界領先的數字信號處理(DSP)SerDes 架構,全新的 112G-ELR SerDes IP 可以支持 45dB 插入損耗,擁有卓越的功耗、性能、面積(PPA)指標,是超大規模 ASICs,人工智能/機器學習(AI/ML)加速器,交換矩陣片上系統(SoCs)和 5G 基礎設施應用的理想選擇。

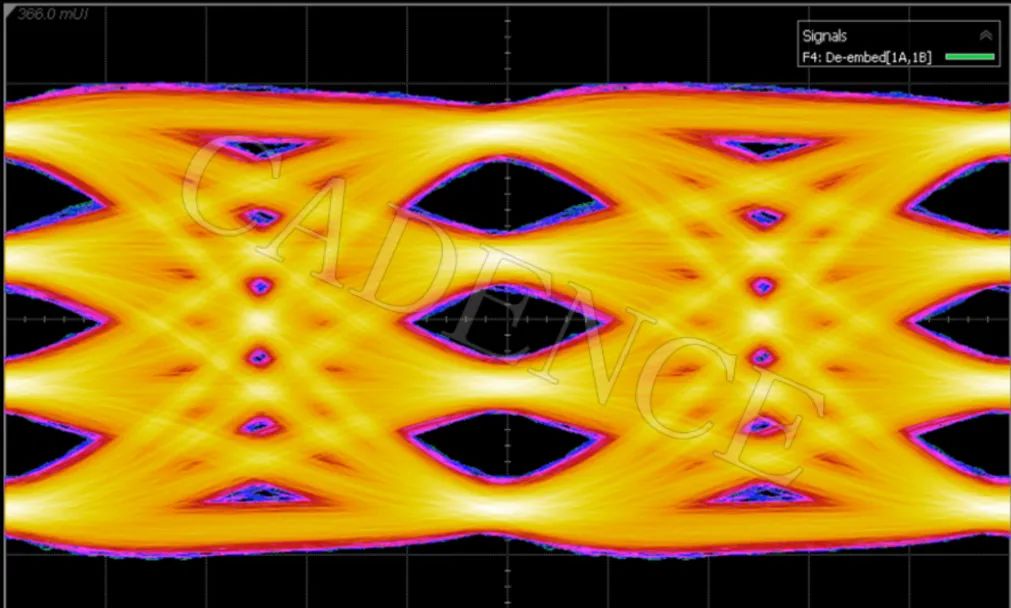

Cadence112G-ELRSerDes

在 TSMC3nm 工藝環境下的眼圖

(106.25 GbpsPAM4)

ELR SerDes PHY 符合 IEEE 和 OIF 長距離(LR)標準,在基礎規格之外提供了額外的性能裕度。上方圖片展示了三個張大的眼圖,它們在 PAM4 模式下具有良好的對稱性,將四個信號電平分開。3nm 演示展示了 E-10 級的卓越誤碼率 (BER)性能以及 39dB bump 間通道,與 28dB Ball 間插損誤碼率小于 1E-4 的標準規格相比提供了充足的性能余量。

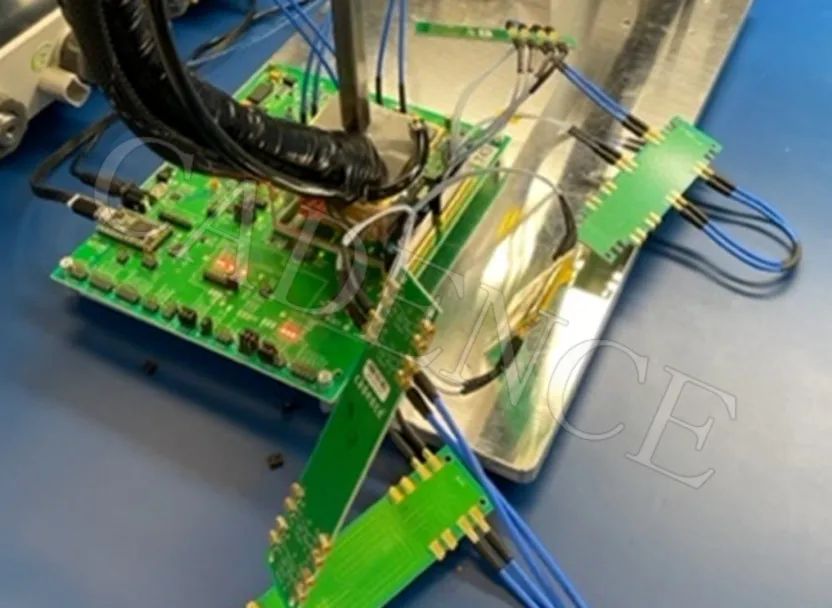

TSMC3nm 工藝環境下

Cadence112G-ELRSerDes 測試板

112G-ELR SerDes IP 同時支持中距離(MR)和超短距離(VSR)應用,實現不同信道更靈活的功耗節省。NRZ 和 PAM4 信號下的數據傳輸速率從 1G到 112G,實現背板,直連線纜(DAC),芯片間以及芯片到模塊的可靠高速數據傳輸。

SerDes IP 采用領先的基于 DSP 的架構,通過最大可能性序列檢測(MLSD)和反射抵消技術實現損耗及反射信道的系統穩定。MLSD 技術可以優化 BER,提供更強大的突發性錯誤處理能力。通過專有的實現技術,Cadence 能確保 MLSD 的功耗開銷最小。反射消除技術消除了具有實際走線和連接器的產品環境中的雜散、遠距離反射,從而提供穩健的 BER 結果。

3nm 工藝下的 Cadence 112G-ELR SerDes 解決方案進一步強化了我們在高性能互聯 IP 領域的領導力,是大規模數據中心的理想選擇,客戶也可以從 TSMC 的 3nm 工藝中獲得更顯著的功耗和性能優化,是目前在 PPA 和晶體管領域最先進的技術。

審核編輯:湯梓紅

-

臺積電

+關注

關注

44文章

5806瀏覽量

176972 -

工藝

+關注

關注

4文章

718瀏覽量

30379 -

Cadence

+關注

關注

68文章

1022瀏覽量

147249 -

3nm

+關注

關注

3文章

237瀏覽量

15060

原文標題:Cadence 發布面向 TSMC 3nm 工藝的 112G-ELR SerDes IP 展示

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

小米自研3nm旗艦SoC、4G基帶亮相!雷軍回顧11年造芯路

3nm大規模導入光模塊:Credo推出二代1.6T光DSP

臺積電擬投資170億,在日本建設3nm芯片工廠

華為發布面向移動網絡的多智能體系統創新成果

創飛芯40nm HV工藝OTP IP完成上架

奧比中光發布面向機器人領域的全新感知產品矩陣

448G的路徑 | Samtec與Cadence合作的224G測試平臺具備可擴展性、成本優勢

智原推出最新SerDes IP持續布局聯電22納米IP解決方案

智原科技推出最新SerDes IP持續布局聯電22納米IP解決方案

Cadence推出HBM4 12.8Gbps IP內存系統解決方案

雷軍:小米自研芯片采用二代3nm工藝 雷軍分享小米芯片之路感慨

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

Cadence發布面向TSMC 3nm工藝的112G-ELR SerDes IP展示

Cadence發布面向TSMC 3nm工藝的112G-ELR SerDes IP展示

評論