來源:Cadence楷登

近日,Cadence宣布其首款基于 Arm 的系統(tǒng)級小芯片(Chiplet)開發(fā)成功并流片,這是一項(xiàng)突破性成就。這項(xiàng)創(chuàng)新標(biāo)志著芯片技術(shù)的關(guān)鍵進(jìn)步,展現(xiàn)了 Cadence 致力于通過其芯片架構(gòu)和框架推動(dòng)行業(yè)領(lǐng)先解決方案的承諾。

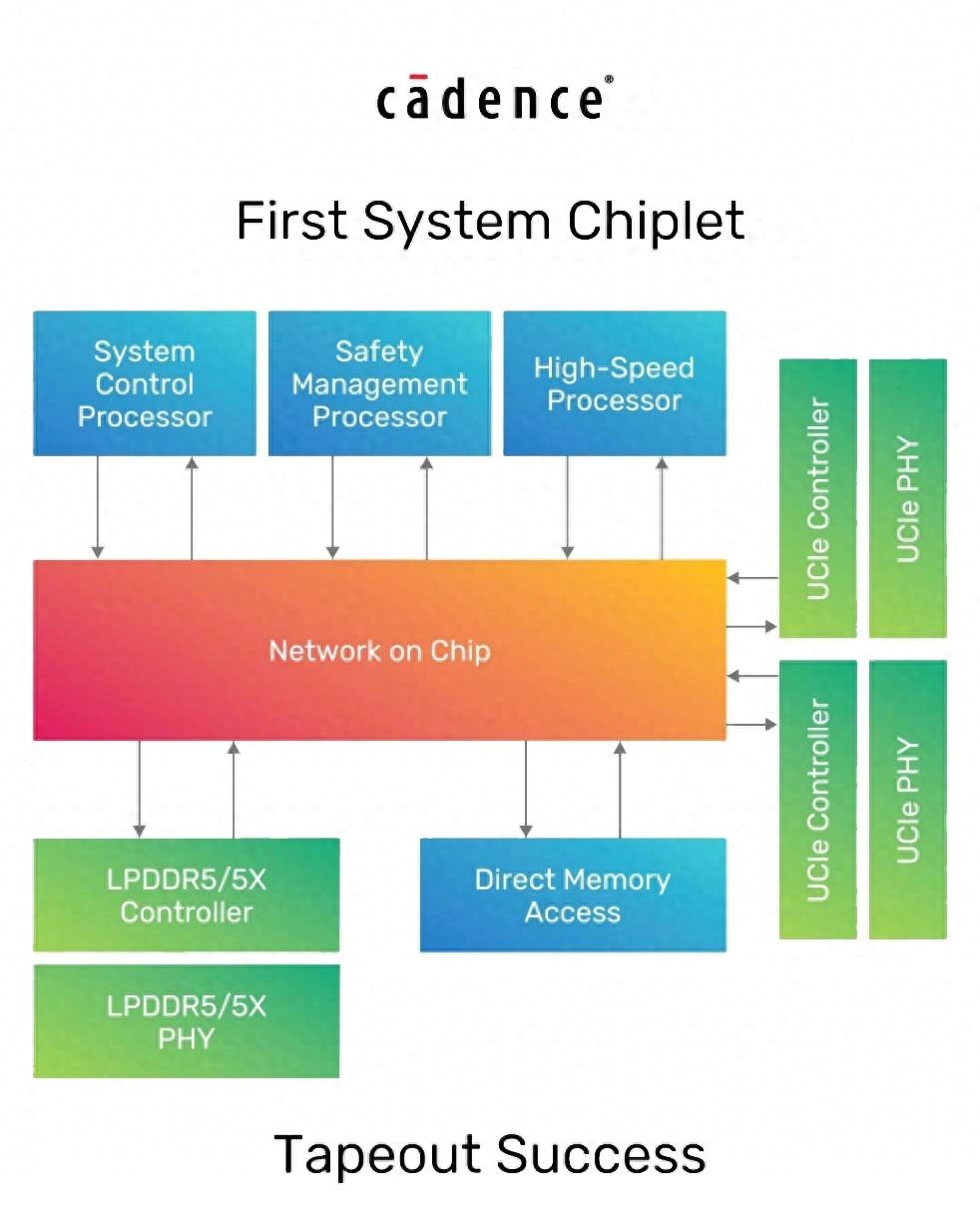

第一個(gè)系統(tǒng)級 Chiplet

Cadence 成功制作了業(yè)界首款系統(tǒng)級小芯片的原型、設(shè)計(jì)并流片。該芯片將處理器、系統(tǒng) IP 和內(nèi)存 IP 集成在一個(gè)封裝中,通過通用芯片互連標(biāo)準(zhǔn) (UCIe?)接口進(jìn)行互連。該芯片與 Arm 共同開發(fā),符合 Arm 的芯片系統(tǒng)架構(gòu)(CSA),該標(biāo)準(zhǔn)可確保互操作性并加快芯片的上市時(shí)間。

系統(tǒng)小芯片包括管理整個(gè)多芯片組 SoC 的資源和功能的功能。該芯片組具有系統(tǒng)處理器、安全管理處理器、Cadence 控制器以及用于 LPDDR5 和 UCIe 的 Cadence PHY IP 等組件,是 Cadence 創(chuàng)新的體現(xiàn)。該芯片組采用 Cadence Janus NoC 技術(shù),可為 UCIe IP 提供高達(dá) 64GB/s 的峰值帶寬,為 LPDDR5 IP 提供高達(dá) 32GB/s 的峰值內(nèi)存帶寬。

與 Arm 攜手,共同推進(jìn) Chiplet 生態(tài)系統(tǒng)

2024 年 3 月,Cadence 和 Arm 正式建立長期合作關(guān)系,以提供基于芯片的參考設(shè)計(jì)和尖端軟件開發(fā)平臺(tái)。此次合作將 Cadence 強(qiáng)大的 IP 和 EDA 解決方案與 Arm 先進(jìn)的 IP 技術(shù)相結(jié)合,大大降低了設(shè)計(jì)復(fù)雜性并加快了客戶的產(chǎn)品上市時(shí)間。為進(jìn)一步的發(fā)展奠定了基礎(chǔ),為客戶提供了一個(gè)全面的開發(fā)平臺(tái),以實(shí)現(xiàn)極佳的性能和效率。

此次合作的核心戰(zhàn)略是投資 Arm CSA,從而實(shí)現(xiàn)供應(yīng)商之間更大的組件重用。Cadence 是 CSA 的積極貢獻(xiàn)者,正在開發(fā)符合此標(biāo)準(zhǔn)的芯片。這些標(biāo)準(zhǔn)允許小芯片(包括 Arm計(jì)算子系統(tǒng)(CSS)和 Cadence 系統(tǒng)芯片)實(shí)現(xiàn)規(guī)模化并加快上市時(shí)間。

先進(jìn)的 IP 技術(shù)創(chuàng)新

憑借數(shù)十年的 IP 和子系統(tǒng)設(shè)計(jì)專業(yè)知識(shí),硅解決方案事業(yè)部可提供高價(jià)值解決方案來解決客戶挑戰(zhàn)。將功能抽象為小芯片 IP 可幫助客戶更快地將創(chuàng)新推向市場。Cadence 掌握的先進(jìn)封裝和互連技術(shù)可實(shí)現(xiàn)可擴(kuò)展的高性能解決方案,從而提高效率并推動(dòng)技術(shù)進(jìn)步。

利用 Chiplet 技術(shù)改變行業(yè)

從單片 SoC 轉(zhuǎn)向基于小芯片的設(shè)計(jì),其驅(qū)動(dòng)力在于提高設(shè)計(jì)效率、縮短平臺(tái)更新周期以及優(yōu)化功率、性能和面積(PPA)指標(biāo)。小芯片支持多代工廠業(yè)務(wù)模式,在同一封裝內(nèi)集成跨代工廠工藝技術(shù)。隨著技術(shù)密度擴(kuò)展放緩,芯片對于克服摩爾定律限制和工藝掩模版限制至關(guān)重要。新的封裝和互連解決方案(包括 2.5D 和 3D 封裝以及 UCIe 等芯片到芯片接口)支持這種變革性方法,為客戶提供了加速創(chuàng)新和市場準(zhǔn)備的途徑。

結(jié)語

Cadence 在小芯片技術(shù)方面的開創(chuàng)性工作代表了半導(dǎo)體行業(yè)的重大進(jìn)步。Cadence 通過創(chuàng)新的架構(gòu)、強(qiáng)大的 IP 和戰(zhàn)略合作伙伴關(guān)系,為效率、可擴(kuò)展性和性能樹立了新的標(biāo)桿。這些發(fā)展?jié)M足了高性能計(jì)算、汽車和數(shù)據(jù)中心行業(yè)不斷變化的需求,并幫助客戶克服設(shè)計(jì)挑戰(zhàn)并加快產(chǎn)品上市時(shí)間。Cadence 始終致力于突破技術(shù)界限,塑造小芯片生態(tài)系統(tǒng)的未來。

-

芯片

+關(guān)注

關(guān)注

463文章

54305瀏覽量

468418 -

ARM

+關(guān)注

關(guān)注

135文章

9580瀏覽量

393246 -

Cadence

+關(guān)注

關(guān)注

68文章

1022瀏覽量

147221 -

chiplet

+關(guān)注

關(guān)注

6文章

499瀏覽量

13638

發(fā)布評論請先 登錄

Cadence收購Arm基礎(chǔ)IP業(yè)務(wù),誰是贏家?

Cadence推出專為新一代語音AI與音頻應(yīng)用打造的 Tensilica HiFi iQ DSP

Cadence在Arm Neoverse上擴(kuò)展其EDA產(chǎn)品組合

Cadence推出高可靠性LPDDR5X 9600Mbps內(nèi)存IP系統(tǒng)解決方案

Cadence推出全新完整小芯片生態(tài)系統(tǒng)

解構(gòu)Chiplet,區(qū)分炒作與現(xiàn)實(shí)

2025 Cadence 中國技術(shù)巡回研討會(huì)即將開啟 ——系統(tǒng)設(shè)計(jì)與分析專場研討會(huì)(上海站)

Cadence攜手NVIDIA革新功耗分析技術(shù)

Cadence推出LPDDR6/5X 14.4Gbps內(nèi)存IP系統(tǒng)解決方案

Cadence推出Cerebrus AI Studio

Cadence Conformal AI Studio助力前端驗(yàn)證設(shè)計(jì)

Cadence推出HBM4 12.8Gbps IP內(nèi)存系統(tǒng)解決方案

Cadence推出Tensilica NeuroEdge 130 AI協(xié)處理器

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內(nèi)存IP系統(tǒng)解決方案

淺談Chiplet與先進(jìn)封裝

Cadence推出基于Arm的系統(tǒng)Chiplet

Cadence推出基于Arm的系統(tǒng)Chiplet

評論