同時宣布針對臺積公司 N3C 工藝的工具認證完成,并基于臺積公司最新 A14 技術展開初步合作

中國上海,2025 年 5 月 23 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布進一步深化與臺積公司的長期合作,利用經過認證的設計流程、經過硅驗證的 IP 和持續的技術協作,加速 3D-IC 和先進節點技術的芯片開發進程。作為臺積公司 N2P、N5 和 N3 工藝節點 IP 的領先供應商,Cadence 持續為臺積公司生態系統提供卓越的 AI 驅動設計解決方案,應用涵蓋從小芯片(chiplet)、SoC 到先進封裝及 3D-IC 等廣泛領域。這種深度合作涵蓋臺積公司 N2P 和 A16技術的認證工具和流程,為基于臺積公司 A14 技術的相關合作奠定了基礎,并通過擴展對臺積公司 3DFabric設計和封裝的支持,進一步釋放 3D-IC 的潛力。此外,基于現有 N3P 設計解決方案,Cadence 和臺積公司正擴展面向最近推出的臺積公司 N3C 技術的工具認證支持。

N2P 和 A16 AI 硅設計

Cadence 正憑借面向臺積公司先進N2P和A16工藝技術的認證工具和優化 IP,推動 AI 芯片設計領域的創新。為鞏固其在內存 IP 領域的領先地位,Cadence 推出面向 N2P、通過 TSMC9000 硅前認證的 DDR5 12.8G IP。Cadence數字、定制/模擬設計和熱分析解決方案已通過臺積公司 N2P 和 A16 技術認證。結合雙方在 N2P 工藝 AI 驅動數字設計解決方案方面的持續合作,包括對大語言模型(LLM)的運用,這些技術進展將有助于改善未來工藝節點的數字設計流程。

領先的汽車解決方案

高級駕駛輔助系統(ADAS)、自動駕駛和軟件定義汽車的快速發展正推動新一代應用對先進芯片的需求。Cadence 憑借其面向臺積公司N5A和N3A工藝的認證 IP,正在加速這一技術發展過程。Cadence 的高性能設計 IP 產品組合,包括 LPDDR5X-9600、PCI Express(PCIe)5.0、CXL 2.0、25G-KR 和 10G 多協議 SerDes,已針對汽車應用進行專門優化。

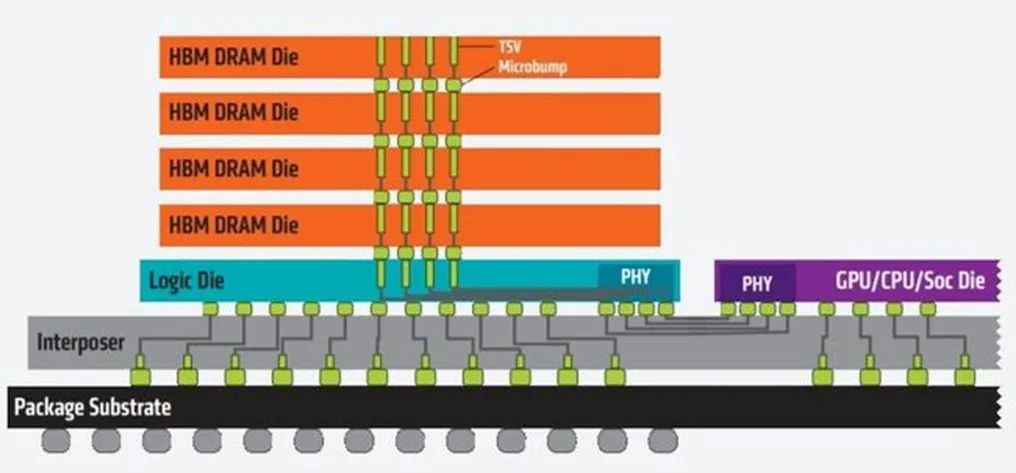

擴展和升級 3DFabric 解決方案

Cadence 為臺積公司 3DFabric提供唯一完整的小芯片(chiplet)設計、封裝與系統分析解決方案。為滿足 AI 訓練市場的需求,Cadence 正在擴展其設計 IP 產品組合,推出面向 3D-IC 設計、通過 TSMC9000 認證的 IP,包括基于 N5/N4P 的HBM3E 9.6G、基于 N3P 的硅前 HBM3E 10.4G,以及 Universal Chiplet Express(UCIe)16G N3P 解決方案。此外,Cadence 的 HBM4 測試芯片已完成預流片準備,為 CoWoS-L 鋪平了道路。

Cadence Integrity3D-IC Platform現推出增強功能,通過 3Dblox 參考流程顯著提升結果質量 (QoR)與 3DIC 全流程質量控制(QC),同時實現全局資源優化、芯片封裝協同設計以及先進多物理場收斂分析,包括靜態時序、電源壓降和熱分析。新增功能包括支持多小芯片(chiplet)設計的貫通結構生成,以及用于端到端 3D-IC 規劃、分區和優化的 AI 驅動工具。

Cadence 的SigrityX技術和Clarity3D Solver還可通過與Cadence Integrity3D-IC Platform集成,實現基于 3Dblox 標準的信號與電源完整性(SIPI)分析的合規性自動化檢查。這種集成流程可使 UCIe 和 HBM 通道的高速 S 參數提取和瞬態時域分析完全實現自動化。此外,Cadence EMXPlanar 3D Solver通過了 N3 認證,并且正在進行 N2P 認證,其仿真精度顯著提升,可滿足先進節點 IC 設計的嚴苛要求。

超越摩爾定律技術創新

利用持續的超越摩爾定律技術創新,Cadence 在不斷推動技術擴展的邊界。Cadence 的VirtuosoStudio現已支持模擬和射頻設計遷移,能夠以可持續的方式縮短先進節點和射頻節點的設計周轉時間。而且,Cadence 正在推進針對臺積公司緊湊型通用光電引擎(COUPE)的設計解決方案,并通過 GPU 加速計算、性能增強的臺積公司云端設計,實現新一代效率提升。

“我們與臺積公司的合作突顯了 Cadence 的承諾,即推動創新,助力客戶加快芯片設計”,Cadence 高級副總裁兼數字與簽核事業部總經理 Chin-Chi Teng說道,“通過提供經過認證的設計流程、經過硅驗證的 IP 以及對臺積公司 N2P、N3 和 N5 等先進節點技術的支持,我們能支持設計人員開發跨越基礎架構 AI 和物理 AI 應用(包括汽車)的領先解決方案。我們正攜手臺積公司推動技術擴展的邊界,實現新一代芯片設計和封裝的進步。”

“我們與 Cadence 等開放創新平臺(OIP)合作伙伴的持久合作對于解決半導體設計中一些最復雜的挑戰來說至關重要”,臺積公司先進技術業務開發處資深處長袁立本表示,“通過將臺積公司的先進工藝和 3D 堆疊及封裝技術與 Cadence 的領先設計解決方案相結合,雙方的共同客戶能夠加快芯片設計,同時實現卓越的性能、功耗和面積優化。我們將繼續共同推動技術變革和創新的突破。”

關于 Cadence

Cadence 是 AI 和數字孿生領域的市場領導者,率先使用計算軟件加速從硅片到系統的工程設計創新。我們的設計解決方案基于 Cadence 的 Intelligent System Design戰略,可幫助全球領先的半導體和系統公司構建下一代產品(從芯片到全機電系統),服務超大規模計算、移動通信、汽車、航空航天、工業、生命科學和機器人等領域。2024 年,Cadence 榮登《華爾街日報》評選的“全球最佳管理成效公司 100 強”榜單。Cadence 解決方案提供無限機會。

-

臺積電

+關注

關注

44文章

5788瀏覽量

174962 -

Cadence

+關注

關注

68文章

1000瀏覽量

146301 -

芯片設計

+關注

關注

15文章

1134瀏覽量

56526 -

3DIC

+關注

關注

3文章

89瀏覽量

20072 -

chiplet

+關注

關注

6文章

485瀏覽量

13528

原文標題:Cadence攜手臺積公司,推出經過其 A16 和 N2P 工藝技術認證的設計解決方案,推動 AI 和 3D-IC 芯片設計發展

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AI重塑EDA,3D-IC成關鍵戰場:Cadence的洞察與應變

新思科技旗下Ansys仿真和分析解決方案產品組合已通過臺積公司認證

Cadence AI芯片與3D-IC設計流程支持臺積公司N2和A16工藝技術

力旺NeoFuse于臺積電N3P制程完成可靠度驗證

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內存IP系統解決方案

西門子與臺積電合作推動半導體設計與集成創新 包括臺積電N3P N3C A14技術

Banana Pi 與瑞薩電子攜手共同推動開源創新:BPI-AI2N

基于TSV的3D-IC關鍵集成技術

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

評論