半導體設計公司新思科技 (Synopsys) 17 日宣布,將與晶圓代工龍頭臺積電合作推出針對高效能運算 (High Performance Compute) 平臺的創新技術,而這些新技術是由新思科技與臺積電合作的 7 納米制程 Galaxy 設計平臺的工具所提供。

2016-10-18 10:55:37 1097

1097 新思科技接口和基礎 IP 組合已獲多家全球領先企業采用,可為 ADAS 系統級芯片提供高可靠性保障 摘要: 面向臺積公司N5A工藝的新思科技IP產品在汽車溫度等級2級下符合 AEC-Q100 認證

2023-10-23 15:54:07 1964

1964 智融的估值尚未最終確定。 ? 芯原股份目前持有芯來智融2.99%股權,通過本次交易擬取得芯來智融全部股權或控股權。本次交易的具體交易方式、交易方案等內容以后續披露的重組預案及公告信息為準。 ? 消息稱臺積電加速 1.4nm 先進工藝

2025-08-29 11:28:48 1921

1921 臺積電0.18工藝電源電壓分別是多少?是1.8v跟3.3v嗎?

2021-06-25 06:32:37

采用0.13um的混合工藝 模擬設計中用到的MOS的柵長選擇就是0.13um嗎? / C5 @, o6 U8 I% q! X而如果采用0.18um的混合工藝 模擬設計中用到的MOS的柵長選擇就是0.18um嗎?

2012-01-12 16:33:54

量;某知名社交電商平臺使用后減少了50%以上跨語言調用接口代碼量;某圖像處理軟件所有C++代碼復用通過AKI來實現。使用AKI后這些項目不僅減少了項目代碼量,還顯著優化了代碼復用與遷移流程。

目前

2025-01-02 17:08:58

各類常用工藝庫臺積電,中芯國際,華潤上華

2015-12-17 19:52:34

Kochpatcharin表示:“臺積公司與新思科技等開放創新平臺(OIP)合作伙伴緊密合作,助力我們的客戶在執行定制及模擬模塊的工藝制程設計遷移時,提高生產效率并加快設計收斂。現在,通過全新的新思科技AI驅動型模擬設

2023-04-03 16:03:26

的必經前提步驟,而先進的制成工藝可以更好的提高中央處理器的性能,并降低處理器的功耗,另外還可以節省處理器的生產成本。 “芯片門”讓臺積電備受矚目 2015年12月份由臺積電舉辦的第十五屆供應鏈管理論

2016-01-25 09:38:11

DevEco Studio支持打開兩個遠程模擬器,演示跨設備遷移嗎?

2022-06-07 10:02:55

ADRV9375-W/PCBZ:模擬設備公司寬帶2600MHz匹配板詳解在現代無線通信中,寬帶信號處理和高性能射頻前端是實現高效數據傳輸的關鍵。ADRV9375-W/PCBZ 是由 模擬設備公司

2024-10-06 16:44:02

臺積電率先量產40納米工藝

臺積電公司日前表示,40納米泛用型(40G)及40納米低耗電(40LP)工藝正式進入量產,成為專業集成電路制造服務領域唯一量產40納米工藝的公司

2008-11-22 18:27:07 1112

1112 Exar選擇微捷碼Titan ADX來加速模擬設計

芯片設計解決方案供應商微捷碼(Magma(r))設計自動化有限公司(納斯達克代碼:LAVA)日前宣布,Exar公司已

2009-12-10 09:48:02 1028

1028 臺積電又跳過22nm工藝 改而直上20nm

為了在競爭激烈的半導體代工行業中提供最先進的制造技術,臺積電已經決定跳過22nm工藝的研

2010-04-15 09:52:16 1210

1210 知名芯片設計廠商ARM公司日前與臺積電公司簽訂了一份為期多年的新協議,根據該協議,雙方將就使用臺積電的FinFET工藝制造下一代64bit ARM處理器產品方面進行合作。

2012-07-24 13:52:57 1172

1172 ,采用臺積公司先進的16納米FinFET (16FinFET)工藝打造擁有最快上市、最高性能優勢的FPGA器件。

2013-05-29 18:21:14 1246

1246 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

2013-07-10 13:07:23 1201

1201 臺積公司透過遍及全球的營運據點服務全世界半導體市場。臺積公司立基臺灣,目前擁有三座最先進的十二吋晶圓廠、五座八吋晶圓廠以及一座六吋晶圓廠。本文介紹了臺積電股票代碼、臺積電是一家怎樣的公司以及臺積電核心價值。

2018-01-08 09:23:25 78181

78181 不過,臺積電帶動的半導體產業群聚效益相當顯著,今年已有來自全球各地的多家重量級半導體設備廠加速在臺布局,包括美商應材、科林研發、德商默克、日商艾爾斯(RS Technologies)及荷商艾司摩爾(ASML)等,凸顯這些大廠都看好臺積電技術優勢,全力助攻臺積電發展先進制程。

2018-07-25 15:56:00 4141

4141

本手冊描述如何使用VieloSo模擬設計環境來模擬模擬設計。VieloSo模擬設計環境被記錄在一系列在線手冊中。下面的文件給你更多的信息。 FieloSo高級分析工具用戶指南提供有關蒙特卡洛、優化和統計分析的信息。

2018-09-20 08:00:00 0

0 在此聯盟之中,臺積電將提供晶圓共乘(CyberShuttle)服務給東京大學工程學院的系統設計實驗室(Systems Design Lab, d.lab),該實驗室亦將采用臺積公司的開放創新平臺虛擬設計環境(VDE)進行晶片設計。

2019-11-29 09:54:54 3111

3111 臺積電從原來的晶圓制造代工角色,逐步跨界至封測代工領域(InFO、CoWoS及SoIC等封裝技術),試圖完整實體半導體的制作流程。

2020-02-25 17:18:14 4256

4256

“臺積電5nm產品已投入批量生產,明年量產4nm產品,計劃2022年實現3nm量產,所有的IC都需要半導體先進的封裝技術,而綠色制造、打造綠色企業是我們的永久使命,” 臺積電(南京)有限公司總經理羅鎮球在2020世界半導體大會上介紹了臺積電先進工藝的演進之路,并表達了企業愿景。

2020-09-10 13:48:44 2294

2294 重點 ● TSMC認證基于新思科技3DIC Compiler統一平臺的CoWoS和InFO設計流程 ● 3DIC Compiler可提高先進封裝設計生產率 ● 集成Ansys芯片封裝協同分析解決方案

2020-10-14 11:11:21 2813

2813 12 月 29 日消息,據國外媒體報道,臺積電近幾年在芯片制程工藝方面走在行業前列,7nm 及 5nm 工藝都是率先量產,良品率也相當可觀,先進的工藝也使他們獲得了蘋果、AMD 等公司的芯片代工訂單

2020-12-29 15:03:19 2056

2056 很顯然,這一波兒的競爭Intel是要落后AMD的,而后者起來的其中一個原因是臺積電先進的工藝制程,而Intel正在醞釀新的調整,并以此追上。

2021-01-10 11:20:20 3336

3336 新思科技與三星基于Fusion Design Platform開展合作,充分釋放三星在最先進節點工藝的優勢 經過認證的流程為開發者提供了一整套針對時序和提取的業界領先數字實現和簽核解決方案 新思科

2021-01-13 16:01:18 2414

2414 在臺積電昨日最新舉辦的法人說明會上,多位臺積電高管分享臺積電2021年資本支出計劃,透露臺積電N3、3D封裝等先進工藝研發情況,并公布臺積電2020年第四季度營收情況。

2021-01-15 10:33:39 2814

2814 1 月 15 日消息,據國外媒體報道,在蘋果轉向 5nm,華為無法繼續采用臺積電的先進工藝代工芯片之后,臺積電 7nm 的產能,也就有了給予其他廠商更多的可能,去年下半年 AMD 獲得的產能

2021-01-15 11:27:28 3373

3373 領先的移動和汽車SoC半導體IP提供商Arasan Chip Systems今天宣布,用于臺積公司22nm工藝技術的eMMC PHY IP立即可用 加利福尼亞州圣何塞2021年1月21日 /美通社

2021-01-21 10:18:23 3344

3344 臺積電的2020年財報令人矚目,總營收創歷史新高。作為全球芯片代工的龍頭,臺積電把持著全球最先進的處理器制造工藝,其中包括代生產了蘋果的A系列芯片,華為海思麒麟高端系列的芯片等等,對于整個芯片制作流程也都是十分熟悉的。那么,與其把蛋糕分幾杯羹,為什么臺積電不自己獨享一份呢?

2021-04-02 14:55:27 9142

9142 什么是HarmonyOS“跨設備遷移”? HarmonyOS“跨設備遷移”是指將承載業務的Page在同一用戶的不同設備間遷移,以便支持用戶業務無縫切換的訴求。“跨設備遷移”實現了業務跨設備流轉功能

2021-06-25 17:32:14 6531

6531 新思科技3DIC Compiler是統一的多裸晶芯片設計實現平臺,無縫集成了基于臺積公司3DFabric技術的設計方法,提供完整的“探索到簽核”的設計平臺

2021-11-01 16:29:14 703

703 通過與臺積公司在早期的持續合作,我們為采用臺積公司先進的N3制程技術的設計提供了高度差異化的解決方案,讓客戶更有信心成功設計出復雜的SoC。

2021-11-02 09:24:25 687

687 的設計方法, 為客戶提供完整的“初步規劃到簽核”的設計平臺 此次合作將臺積公司的技術進展與3DIC Compiler的融合架構、先進設計內分析架構和簽核工具相結合,滿足了開發者對性能、功耗和晶體管數量密度的要求 新思科技(Synopsys)近日宣布擴大與臺積公司的戰略技術合作

2021-11-05 15:17:19 6382

6382 新思科技平臺提供強化功能,以支持臺積公司N3和N4制程的新要求 新思科技Fusion設計平臺能夠提供更快的時序收斂,并確保從綜合到時序和物理簽核的全流程相關性 ,可顯著提高生產力 新思科

2021-11-16 11:06:32 2326

2326 雙方共同推出的工藝設計套件和經認證參考流程可加速高性能汽車、邊緣人工智能和5G SoC的開發 全球半導體制造領先企業GlobalFoundries(GF)聯合新思科技(Synopsys)近日宣布

2021-11-17 14:38:41 2386

2386 根據外媒的消息報道稱,臺積電公司目前正在加大先進封裝投資力度,目前已將旗下CoWoS 封裝業務的部分流程外包分給了OSAT,此前臺積電還公布了最新強化版的CoWoS封裝工藝。

2021-11-25 17:38:58 2472

2472 解決方案能夠實現全面的數據可視化和AI自動優化設計,助力提高先進節點的芯片設計生產力。該解決方案將為所有開發者提供實時、統一、360度視圖,以加快決策過程,通過更深入地了解運行、設計、項目之間的趨勢來加強芯片的開發協作。

2022-06-02 16:09:44 3237

3237 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其數字和定制 / 模擬設計流程已獲得 TSMC N3E 和 N4P 工藝認證,支持最新的設計規則手冊(DRM)。

2022-06-17 17:33:05 6035

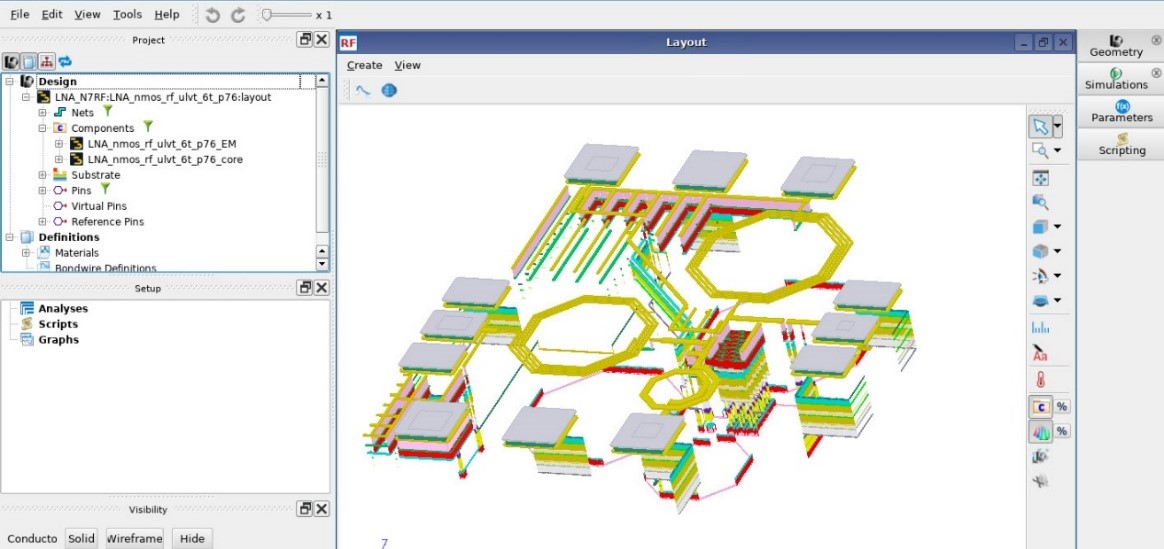

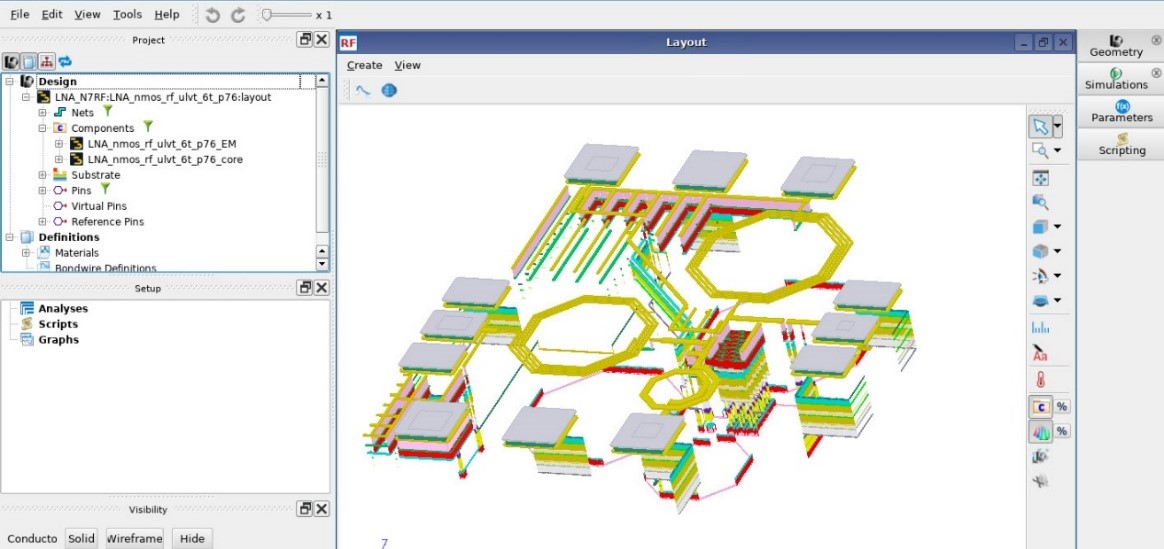

6035 新思科技(Synopsys)近日推出面向臺積公司N6RF工藝的全新射頻設計流程,以滿足日益復雜的射頻集成電路設計需求。

2022-06-24 14:30:13 1700

1700 來源:是德科技 PathWave RFPro 與新思科技定制化編譯器相輔相成,可提供無線晶片設計工作流程所需的整合式電磁模擬工具 是德科技(Keysight Technologies Inc.

2022-06-27 14:41:38 1276

1276

新思科技數字和定制設計流程獲得臺積公司的N3E和N4P工藝認證,并已推出面向該工藝的廣泛IP核組合。

2022-07-12 11:10:51 1780

1780 此前,有媒體報道稱臺積電將于2023年提高先進工藝技術的價格。據報道,根據不同的工藝,價格上漲幅度一般在6%-9%左右。據報道,臺積電將在與客戶協商后將上調幅度修改為3%,成熟流程將上調6%。

2022-09-29 11:11:39 1242

1242 中國上海,2022 年 10 月 27 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence 數字和定制/模擬設計流程已獲得臺積電最新 N4P 和 N3E

2022-10-27 11:01:37 2274

2274 ,納斯達克股票代碼:SNPS )近日宣布,得益于與臺積公司的長期合作,新思科技針對臺積公司N3E工藝技術取得了多項關鍵成就,共同推動先進工藝節點的持續創新。新思科技經產品驗證的數字和定制設計流程已在臺積公司N3E工藝上獲得認證。此外,該流程和新思科技廣泛的

2022-11-08 13:37:19 1951

1951 工藝技術取得了多項關鍵成就,共同推動先進工藝節點的持續創新。新思科技經產品驗證的數字和定制設計流程已在臺積公司N3E工藝上獲得認證。此外,該流程和新思科技廣泛的基礎IP、接口IP組合已經在臺積公司N3E工藝上實現了多項成功流片,助力合

2022-11-10 11:15:22 1158

1158 為滿足5G/6G SoC對性能和功耗的嚴苛需求,新思科技(Synopsys,Inc.,納斯達克股票代碼:SNPS)、Ansys和是德科技近日宣布,推出針對臺積公司16納米精簡型工藝技術(16FFC

2022-11-16 16:24:19 1294

1294 工藝技術的2D/2.5D/3D多裸晶芯片系統。基于與臺積公司在3DFabric?技術和3Dblox?標準中的合作,新思科技提供了一系列全面的、系統級的、經過產品驗證的解決方案,助力共同客戶能夠滿足復雜的多裸晶芯片系統對于功耗和性能的嚴苛要求。

2022-11-16 16:25:43 1653

1653 ? ? ?新思科技(Synopsys, Inc.)近日宣布,推出全面EDA和IP解決方案,面向采用了臺積公司先進N7、N5和N3工藝技術的2D/2.5D/3D多裸晶芯片系統。基于與臺積公司在

2022-12-01 14:10:19 990

990 )設計流程是雙方合作中的亮點之一 新思科技(Synopsys)近日宣布,連續第12年被評選為“臺積公司OIP開放創新平臺年度合作伙伴”(OIP,Open Innovation Platform)并斬獲六個獎項,充分彰顯了雙方長期合作在 多裸晶芯片系統、 加速高質量接口IP、射頻設計、云解決方案

2022-12-14 18:45:02 1338

1338 摘要: 新思科技連續12年被評為“臺積公司OIP年度合作伙伴” 該合作推動了多裸晶芯片系統的發展和先進節點設計 獎項涵蓋數字和定制設計、IP、以及基于云的解決方案 推出毫米波(mmWave)射頻

2022-12-15 10:48:45 542

542

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的節點到節點設計遷移流程,能兼容所有的臺積電先進節點

2023-05-06 15:02:15 1934

1934 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發

2023-05-09 10:09:23 2046

2046 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布與臺積電攜手,針對臺積電 N16 工藝 79GHz 毫米波設計參考流程,優化 Cadence Virtuoso 平臺

2023-05-09 15:04:43 2317

2317 為了不斷滿足新一代系統單晶片(SoC) 的嚴格設計目標,新思科技在臺積電最先進的 N2 製程中提供數位與客製化設計 EDA 流程。相較於N3E 製程,臺積公司N2 製程採用奈米片(nanosheet

2023-05-11 19:02:35 3061

3061 針對臺積公司16FFC的79GHz毫米波射頻設計流程加速自動駕駛系統中射頻集成電路的開發。 新思科技、Ansys和是德科技近日宣布,推出針對臺積公司16納米精簡型工藝技術(16FFC)的全新

2023-05-17 05:45:01 878

878

股票代碼:SNPS)近日宣布,攜手臺積公司和Ansys持續加強多裸晶芯片系統設計與制造方面的合作,助力加速異構芯片集成以實現下一階段的系統可擴展性和功能。得益于與臺積公司在3DFabric?技術和3Dblox?標準中的合作,新思科技能夠為臺積公司先進的7納米、5納米和3納米工藝技

2023-05-17 15:43:06 450

450 3DFabric?技術和3Dblox?標準中的合作,新思科技能夠為臺積公司先進的7納米、5納米和3納米工藝技術上的多裸晶芯片系統設計,提供業界領先的全方位EDA和IP解決方案。臺積公司先進工藝技術集成

2023-05-18 16:04:08 1365

1365 三家全球領先公司緊密協作,以應對 基于臺積公司先進技術的設計在芯片、封裝和系統等方面的挑戰。 新思科技近日宣布,攜手臺積公司和Ansys持續加強多裸晶芯片系統設計與制造方面的合作,助力加速異構芯片

2023-05-22 22:25:02 874

874

新思科技一直與臺積公司保持合作,利用臺積公司先進的FinFET工藝提供高質量的IP。近日,新思科技宣布在臺積公司的N3E工藝上成功完成了Universal Chiplet Interconnect

2023-05-25 06:05:02 1446

1446 面向三星8LPU、SF5 (A)、SF4 (A)和SF3工藝的新思科技接口和基礎IP,加速先進SoC設計的成功之路 摘要: 新思科技接口IP適用于USB、PCI Express、112G以太網

2023-06-30 13:40:14 728

728 內容提要 1 輕松實現節點到節點的設計和 layout 遷移 2 將定制/模擬設計遷移速度提升 2 倍 3 Cadence Virtuoso Studio 針對所有 Samsung Foundry

2023-07-04 10:10:01 1516

1516 的“耳目”。 新思科技一直走在芯片監控解決方案的前沿,而這些解決方案是新思科技芯片生命周期管理(SLM)系列的一部分。最近, 新思科技在臺積公司N5和N3E工藝上完成了PVT監控IP測試芯片的流片 。這是一個里程碑式的成功。從此,那些準備在這些先進節點

2023-07-11 17:40:01 1827

1827 技的解決方案可在英特爾代工服務提供的制程工藝上實現安全且先進的微電子技術開發 新思科技(Synopsys)近日宣布,其搭載了Synopsys.ai全棧式AI驅動型EDA解決方案的數字和定制設計流程已經通過英特爾代工服務(IFS)的Intel 16制程工藝認證,以助力簡化功耗和空間受限型應用

2023-08-07 18:45:03 1186

1186 基于臺積公司N3E工藝技術的新思科技IP能夠為希望降低集成風險并加快首次流片成功的芯片制造商建立競爭優勢

2023-08-24 17:37:47 1737

1737 新思科技經認證的多裸晶芯片系統設計參考流程和安全的Die-to-Die IP解決方案,加速了三星SF 5/4/3工藝和I-Cube及X-Cube技術的設計和流片成功。 新思科技3DIC

2023-09-14 09:38:28 1995

1995 流程,能兼容所有的 TSMC(臺積電)先進節點,包括最新的 N3E 和 N2 工藝技術。 這款生成式設計遷移流程由 Cadence 和 TSMC 共同開發,旨在實現定制和模擬 IC 設計在 TSMC

2023-09-27 10:10:04 1633

1633 《半導體芯科技》編譯 來源:EENEWS EUROPE 新思科技(Synopsys)表示,其客戶已在臺積電2nm工藝上流片了多款芯片,同時對模擬和數字設計流程進行了認證。 新思科技表示,臺積電2nm

2023-10-08 16:49:24 930

930 的生產力 基于 AI 驅動的 Virtuoso Studio 的定制/模擬流程支持電路優化,功能經過增強,可將設計遷移吞吐量提升 3 倍 雙方的共同客戶正在積極使用 N2 PDK 來開發 AI、大規模計算

2023-10-10 16:05:04 1331

1331 。 Synopsys.ai? EDA解決方案中的模擬設計遷移流程可實現臺積公司跨工藝節點的快速設計遷移。 新思科技接口IP和基礎IP的廣泛產品組合正在開發中,將助力縮短設計周期并降低集成風險。 ? 加利福尼亞州桑尼維爾, 2023 年 10 月 18 日 – 新思科技(Synopsys, I

2023-10-19 11:44:22 918

918 新思科技近日宣布,其數字和定制/模擬設計流程已通過臺積公司N2工藝技術認證,能夠幫助采用先進工藝節點的SoC實現更快、更高質量的交付。新思科技這兩類芯片設計流程的發展勢頭強勁,其中數字設計流程已實現

2023-10-24 16:42:06 1394

1394 新思科技(Synopsys, Inc.)近日宣布,面向臺積公司N5A工藝推出業界領先的廣泛車規級接口IP和基礎IP產品組合,攜手臺積公司推動下一代“軟件定義汽車”發展,滿足汽車系統級芯片(SoC)的長期可靠性和高性能計算需求。

2023-10-24 17:24:56 1692

1692 摘要: 全新參考流程針對臺積公司 N4PRF 工藝打造,提供開放、高效的射頻設計解決方案。 業界領先的電磁仿真工具將提升WiFi-7系統的性能和功耗效率。 集成的設計流程提升了開發者的生產率,提高了

2023-10-30 16:13:05 902

902 計 新思科技攜手Ansys 和 Keysight 共同推出全新射頻設計參考流程,能夠為現代射頻集成電路設計提供完整解決方案 新思科技(Synopsys)近日宣布,其模擬設計遷移流程已應用于臺積公司N4P、N3E 和 N2 在內的多項先進工藝。作為新思科技定制設計系列產品

2023-11-09 10:59:40 1588

1588 (RF)設計和接口IP五項大獎。新思科技與臺積公司長期穩固合作,持續提供經過驗證的解決方案,包括由Synopsys.ai全棧式AI驅動型EDA解決方案支持的認證設計流程,幫助共同客戶加快創新型人工智能

2023-11-14 10:31:46 1202

1202 多個獎項高度認可新思科技在推動先進工藝硅片成功和技術創新領導方面所做出的卓越貢獻 摘要 : 新思科技全新數字與模擬設計流程認證針對臺積公司N2和N3P工藝可提供經驗證的功耗、性能和面積(PPA)結果

2023-11-14 14:18:45 743

743 全新參考流程針對臺積公司 N4PRF 工藝打造,提供開放、高效的射頻設計解決方案。

2023-11-27 16:54:02 1430

1430 臺積電近期宣布加速其先進封裝計劃,并上調了產能目標。這是因為英偉達和AMD等客戶訂單的持續增長。

2024-01-24 15:58:49 1061

1061 ?芯片制造商與EDA解決方案和廣泛的IP組合緊密合作, 能夠提升產品性能并加快上市時間 摘要: 新思科技數字和模擬EDA流程經過認證和優化,針對Intel 18A工藝實現功耗、性能和面積目標

2024-03-05 10:16:59 1014

1014 新思科技數字和模擬 EDA 流程經過認證和優化,針對Intel 18A工藝實現功耗、性能和面積目標

2024-03-05 17:23:44 1134

1134 近日,新思科技與英特爾宣布深化合作,共同加速先進芯片設計的步伐。據悉,新思科技的人工智能驅動的數字和模擬設計流程已經成功通過英特爾代工的Intel 18A工藝認證,這一突破性的進展標志著雙方在芯片設計領域的合作邁上了新臺階。

2024-03-06 10:33:59 1293

1293 近日,是德科技、新思科技和Ansys攜手,共同推出了一個革命性的集成射頻(RF)設計遷移流程。這一流程旨在助力臺積電從N16制程無縫升級到N6RF+技術,以滿足當前無線集成電路在功耗、性能和面積(PPA)上的嚴苛挑戰。

2024-05-11 10:42:17 788

788 套件賦能可投產的數字和模擬設計流程能夠針對臺積公司N3/N3P和N2工藝,助力實現芯片設計成功,并加速模擬設計遷移。 新思科技物理驗證解決方案已獲得臺積公司N3P和N2工藝技術認證,可加速全芯片物理簽核。 新思科技3DIC Compiler和光子集成電路(PIC)解決方案與臺

2024-05-11 11:03:49 695

695

新思科技EDA事業部戰略與產品管理副總裁Sanjay Bali表示:“新思科技在可投產的EDA流程和支持3Dblox標準的3DIC Compiler光子集成方面的先進成果,結合我們廣泛的IP產品組合,使得我們與臺積公司能夠助力開發者基于臺積公司先進工藝加速下一代芯片設計創新。

2024-05-11 16:25:42 1015

1015 新思科技近日與臺積公司宣布,在先進工藝節點設計領域開展了廣泛的EDA和IP合作。雙方的合作成果已經成功應用于一系列人工智能、高性能計算和移動設計領域,取得了顯著成效。

2024-05-13 11:04:48 931

931 由Synopsys.ai EDA套件賦能可投產的數字和模擬設計流程能夠針對臺積公司N3/N3P和N2工藝,助力實現芯片設計成功,并加速模擬設計遷移。

2024-05-14 10:36:48 1197

1197

臺積電作為晶圓代工領域的領頭羊,正加速其產能擴張步伐,以應對日益增長的人工智能市場需求。據摩根士丹利最新發布的投資報告“高資本支出與持續性的成長”顯示,臺積電在2nm及3nm先進制程以及CoWoS先進封裝技術上的產能正快速提升,這進一步鞏固了其在全球半導體市場的領先地位。

2024-09-27 16:45:25 1247

1247 半導體技術領域的發展速度十分驚人,新思科技與臺積公司(TSMC)始終處于行業領先地位,不斷突破技術邊界,推動芯片設計的創新與效率提升。我們與臺積公司的長期合作催生了眾多行業進步,從更精細的工藝節點到更高層次的系統集成,創造了無限可能。

2024-10-31 14:28:17 1022

1022 近日,據臺灣媒體報道,隨著AI領域對先進制程與封裝產能的需求日益旺盛,臺積電計劃從2025年1月起,針對其3nm、5nm以及先進的CoWoS封裝工藝進行價格調整。 具體而言,臺積電將對3nm和5nm

2024-12-31 14:40:59 1373

1373 為了滿足市場上對先進封裝技術的強勁需求,臺積電正在加速推進其CoWoS(Chip-on-Wafer-on-Substrate)等先進封裝技術的布局。近日,市場傳言臺積電將在南部科學工業園區(南科

2025-01-23 10:18:36 931

931 近日,臺積電在美國舉行了首季董事會,并對外透露了其在美國的擴產計劃。臺積電董事長魏哲家在會上表示,公司將正式啟動第三廠的建廠行動,這標志著臺積電在美國的布局將進一步加強。 據了解,臺積電在先進

2025-02-14 09:58:01 933

933 :CDNS)近日宣布進一步深化與臺積公司的長期合作,利用經過認證的設計流程、經過硅驗證的 IP 和持續的技術協作,加速 3D-IC 和先進節點技術的芯片開發進程。作為臺積公司 N2P、N5 和 N3 工藝節點

2025-05-23 16:40:04 1709

1709 新思科技近日宣布持續深化與臺積公司的合作,為臺積公司的先進工藝和先進封裝技術提供可靠的EDA和IP解決方案,加速AI芯片設計和多芯片設計創新。

2025-05-27 17:00:55 1038

1038 積公司的模擬設計遷移(ADM)方法學為基礎,集成了新思科技AI驅動的射頻遷移解決方案與是德科技的射頻解決方案,可簡化無源器件和設計組件的重新設計工作,使其符合臺積公司更先進的射頻工藝規則。

2025-06-27 17:36:15 1347

1347 還就面向TSMC-COUPE平臺的AI輔助設計流程開展了合作。新思科技與臺積公司共同賦能客戶有效開展芯片設計,涵蓋AI加速、高速通信和先進計算等一系列應用。

2025-10-21 10:11:05 434

434 新思科技作為重要的合作伙伴,再次獲臺積公司認可。在2025年臺積公司開放創新平臺(Open Innovation Platform,簡稱OIP)生態系統論壇上,我們榮膺六項年度合作伙伴大獎。這些獎項

2025-10-24 16:31:58 1124

1124 新思科技近期宣布,其LPDDR6 IP已在臺積公司 N2P 工藝成功流片,并完成初步功能驗證。這一成果不僅鞏固并強化了新思科技在先進工藝節點 IP 領域的領先地位,同時也為客戶提供可信賴的、經硅片驗證的IP選擇,可滿足移動通訊、邊緣 AI 及高性能計算等更高存儲帶寬需求的應用場景。

2025-10-30 14:33:48 1873

1873

電子發燒友App

電子發燒友App

評論