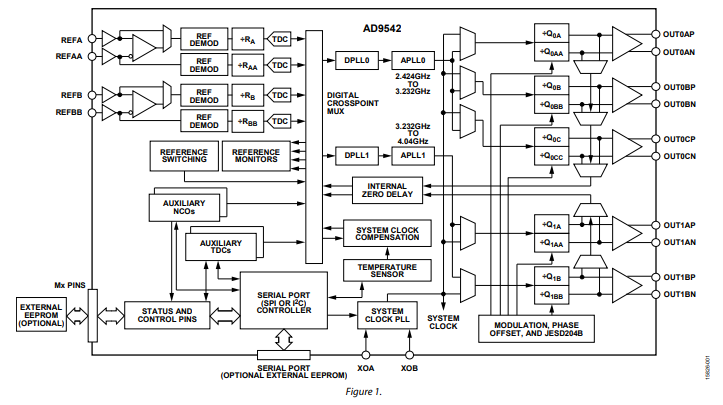

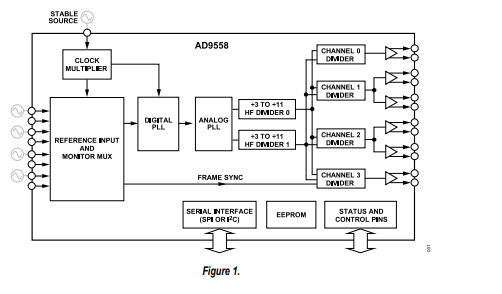

DS31408是一個靈活的,高性能的不同頻率轉換時間和頻率合成中的應用集成電路。在其八個輸入時鐘和14個輸出時鐘,每個設備可以接受或生成幾乎任何2kHz和750MHz的頻率之間。該器件提供兩個獨立的DPLLs,為兩個獨立的時鐘代路徑。

輸入時鐘分頻,分數比例根據需要,不斷為監測活動和頻率精度。輸入時鐘的最佳選擇,手動或自動,作為兩個靈活,高性能數字鎖相環每個參考時鐘。每個數字鎖相環鎖定到選定的參考,并提供可編程的帶寬,非常高的分辨率緩繳能力,真正無中斷輸入時鐘之間切換。數字鎖相環后跟一個時鐘合成子系統,已與自己的32位分頻器,相位調整七個完全可編程數字頻率合成塊,三高速低抖動APLLs,14輸出時鐘,每個。分數的APLLs提供縮放和輸出的RMS抖動低于1ps少。對于電信系統,DS31408的所有必需的特性和功能,作為中央計時功能或線路卡時鐘IC。

此外,DS31408具有嵌入時鐘的IEEE ? 1588可以通過系統軟件帶領遵循時間主系統中的其他地方或其他地方的網絡。這座時鐘的所有必要的功能是在1588年普通時鐘,邊界時鐘或透明時鐘中央時鐘

關鍵特性

八個輸入時鐘

差分或CMOS / TTL電格式

任何頻率從2kHz到750MHz的

分數縮放的64B/66B和FEC縮放(如64/66,二百五十五分之二百三十七,255分之238)或任何其他降尺度要求

連續輸入時鐘的質量監控

兩個高性能DPLLs

無中斷參考輸入丟失的開關

自動或手動相位生成輸出

緩繳的損失所有投入

可編程帶寬0.5MHz至400Hz的

七個數字頻率合成器

每個人都可以從要么全數字鎖相環

產生任何2kHz倍數高達77.76MHz

三個輸出APLLs

輸出頻率750MHz的

高分辨率的小數為FEC和64B/66B尺度(例如,237分之255,238分之255,六十四分之六十六)或任何其他尺度要求

小于1ps RMS輸出抖動

同時從同一個參考三低抖動率(例如,622.08MHz為SONET,237分之255為OTU2 * 622.08MHz和156.25MHz為萬兆)

七組14輸出時鐘

幾乎所有的頻率從<1Hz到750MHz的

每個組的奴隸一個DFS時鐘,任何APLL的時鐘,或任何輸入時鐘(分散和規模)

每個人都有一個差分輸出(3慢性粒細胞白血病,4個LVDS / LVPECL的)和獨立的CMOS / TTL輸出

32位每輸出分頻器

IEEE1588的時鐘功能

通過軟件可操縱與2為8ns的時間分辨率和2 - 32ns頻率分辨率

4ns的輸入和輸出時間戳精度邊緣布置精度

可編程時鐘和時間對準I / O來同步所有1588年在大型系統設備

支持1588年業主立案法團,BC和訓練班架構

一般特征

合適的線路卡IC卡IC或時間用于Stratum 2/3E/3/4E/4,校董會,美國證券交易委員會/歐洲經濟共同體,或SSU

幾乎所有接受,并產生高達750MHz的頻率從1Hz的

內補償本振頻率誤差

1.8V工作電壓與3.3V的I / O(5V耐壓)

電子發燒友App

電子發燒友App

評論