概述

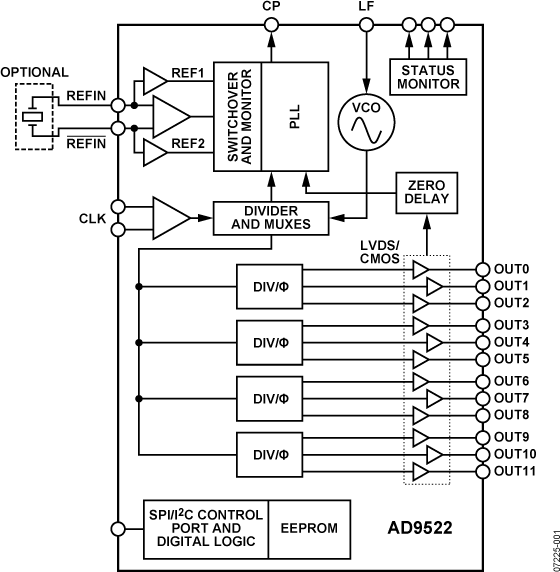

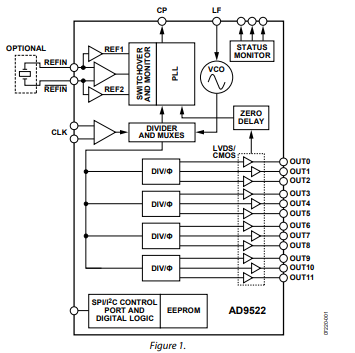

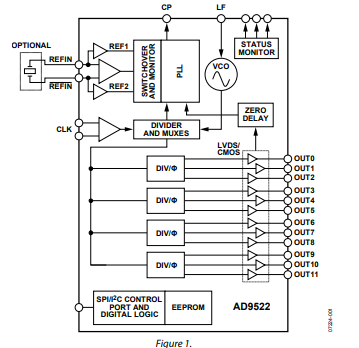

AD9522-4提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內(nèi)集成鎖相環(huán)(PLL)和電壓控制振蕩器(VCO)。片內(nèi)VCO的調(diào)諧頻率范圍為1.4 GHz至1.8 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

AD9522串行接口支持SPI和I^2^C?端口。封裝內(nèi)EEPROM可以通過串行接口進行編程,存儲用于上電和芯片復(fù)位的用戶定義寄存器設(shè)置。

數(shù)據(jù)表:*附件:AD9522-4 12路LVDS 24路CMOS輸出時鐘發(fā)生器,集成1.6 GHz VCO技術(shù)手冊.pdf

AD9522具有12路LVDS輸出(分為四組)。任一路800 MHz LVDS輸出均可重新配置為兩路250 MHz CMOS輸出。

每組輸出均具有一個分頻器,其分頻比(從1至32)和相位(粗調(diào)延遲)均可以設(shè)置。

AD9522提供64引腳LFCSP封裝,可以采用3.3 V單電源供電。外部VCO的工作電壓最高可達5.5 V。

AD9522的額定工作溫度范圍為?40°C至+85°C標準工業(yè)溫度范圍。

AD9520-4是AD9522-4的等效產(chǎn)品,采用LVPECL/CMOS驅(qū)動器而非LVDS/CMOS驅(qū)動器。

^1^AD9522在本數(shù)據(jù)手冊中泛指AD9522系列的所有器件。但是,使用AD9522-4時,它僅指AD9522系列的該特定器件。

應(yīng)用

- 低抖動、低相位噪聲時鐘分配

- SONET、10Ge、10G FC和其它10 Gbps協(xié)議的時鐘產(chǎn)生和轉(zhuǎn)換

- 前向糾錯(G.710)

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE提供時鐘

- 高性能無線收發(fā)器

- 自動測試設(shè)備(ATE)和高性能儀器儀表

- 寬帶基礎(chǔ)設(shè)施

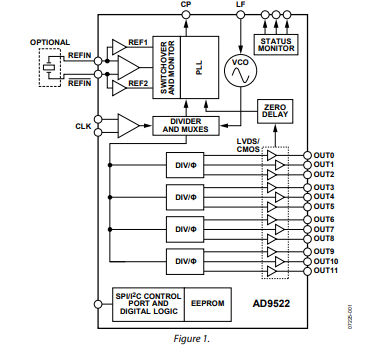

框圖

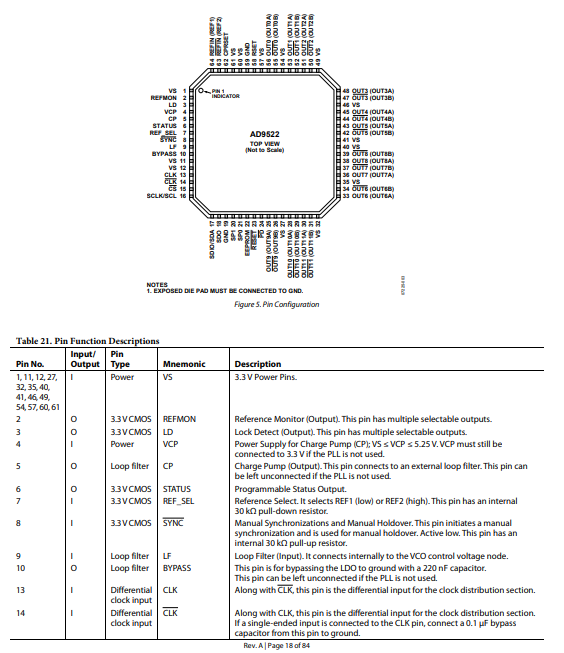

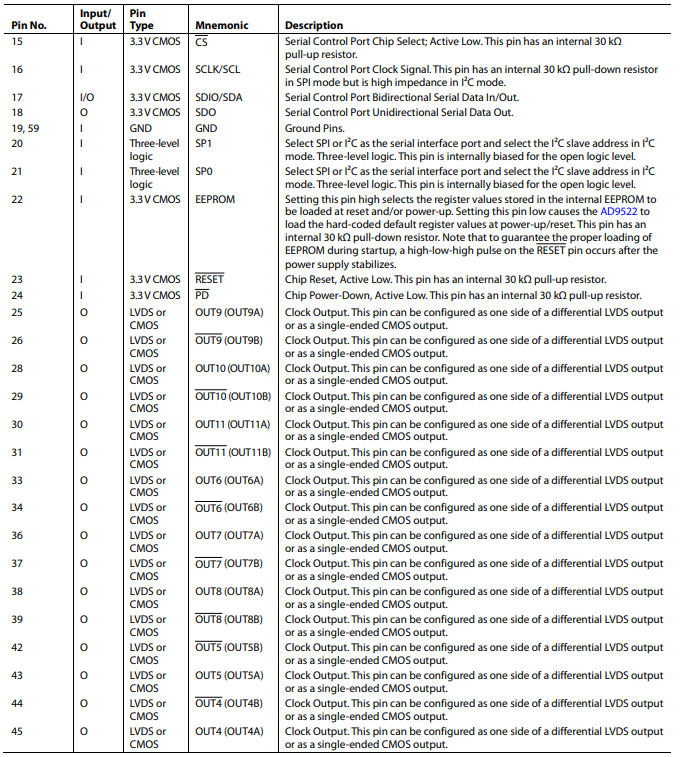

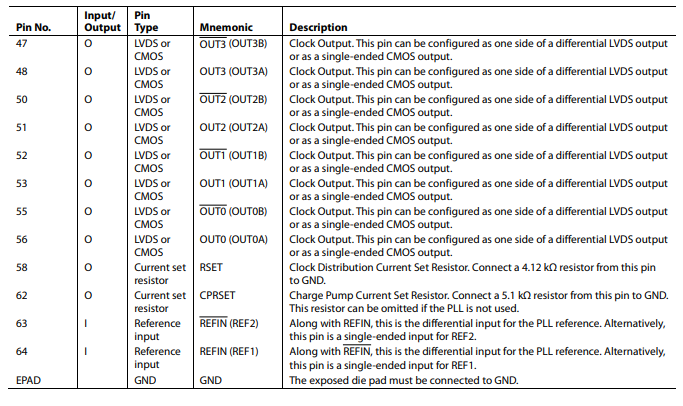

引腳配置描述

片上VCO

AD9522集成了一個片上VCO,其頻率范圍見表2。校準程序可確保VCO在所需頻率附近穩(wěn)定運行。必須先校準VCO,再設(shè)置PLL環(huán)路。此外,每次VCO頻率發(fā)生變化時,都要將其校準到標稱值。不過,一旦校準完成,VCO在很寬的溫度和電壓范圍內(nèi)都能穩(wěn)定運行,無需額外校準。有關(guān)更多信息,請參見“VCO校準”部分。

為了在這個VCO覆蓋的寬頻率范圍內(nèi)進行調(diào)諧,需要使用調(diào)諧范圍。校準程序會選擇相應(yīng)的范圍,以實現(xiàn)所需的VCO頻率。有關(guān)更多校準部分的信息,請參見“VCO校準”。

片上VCO由片上低壓差(LDO)線性穩(wěn)壓器供電。LDO可在一定程度上隔離VCO電壓的變化,使電源電壓電平相對穩(wěn)定。必須通過220 nF電容將BYPASS引腳連接到地,以確保穩(wěn)定性。這款LDO采用了亞德諾半導(dǎo)體(Analog Devices, Inc.)的anyCAP?系列穩(wěn)壓器技術(shù),對所用電容類型不敏感。不支持從BYPASS引腳驅(qū)動外部負載。

使用外部VCO/VCXO時,可將BYPASS和LF引腳懸空。圖41展示了這種配置。

PLL外部環(huán)路濾波器

使用外部VCO時,外部環(huán)路濾波器必須以BYPASS引腳為參考點,以實現(xiàn)最佳噪聲性能和穩(wěn)定性。圖40展示了使用內(nèi)部VCO的PLL的外部環(huán)路濾波器示例。必須根據(jù)VCO的KVCO、PFD的電荷依賴性、CP電流、期望的環(huán)路帶寬以及期望的相位裕度來計算環(huán)路濾波器。環(huán)路濾波器會影響相位噪聲、鎖定建立時間和環(huán)路穩(wěn)定性。了解PLL理論有助于理解環(huán)路濾波器的設(shè)計。ADIsimCLK可根據(jù)應(yīng)用要求幫助計算環(huán)路濾波器。

使用外部VCO時,外部環(huán)路濾波器必須以地為參考點。圖41展示了使用外部VCO的PLL的外部環(huán)路濾波器示例。

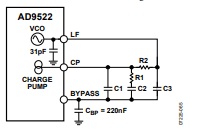

圖40. 使用內(nèi)部VCO的PLL的外部環(huán)路濾波器示例

圖41. 使用外部VCO的PLL的外部環(huán)路濾波器示例

圖42和圖43分別展示了用于生成圖30和圖31中曲線的典型PLL環(huán)路濾波器。

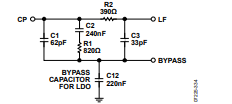

圖42. 用于時鐘生成的典型PLL環(huán)路濾波器

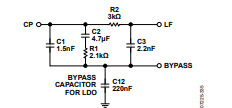

圖43. 用于時鐘凈化的典型PLL環(huán)路濾波器

PLL參考輸入

AD9522具有靈活的PLL參考輸入電路,支持全差分輸入、兩個獨立的單端輸入,或采用片上穩(wěn)幅放大器的16.62 MHz至33.33 MHz晶體振蕩器。可選的參考時鐘倍頻器可用于將PLL參考頻率加倍。差分和單端輸入均為自偏置,便于交流或直流耦合信號輸入。

必須專門啟用差分或單端參考輸入。默認情況下,所有PLL參考輸入均處于關(guān)閉狀態(tài)。

差分輸入和單端輸入共用引腳REFIN (REF1) 和 overline{text{REFIN}} (REF2)。所需的參考輸入類型由寄存器0x01C選擇和控制(見表49和表53)。

選擇差分參考輸入時,自偏置電平會使兩端略微偏移(約 -100 mV,見表2),以防止參考信號緩慢或丟失時緩沖器出現(xiàn)抖動。這會增加驅(qū)動器所需的電壓擺幅,可通過交流耦合LVDS或交流耦合LVPECL信號來克服這種偏移。

-

發(fā)生器

+關(guān)注

關(guān)注

4文章

1429瀏覽量

64588 -

pll

+關(guān)注

關(guān)注

6文章

981瀏覽量

138167 -

時鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

134988 -

VCO

+關(guān)注

關(guān)注

14文章

314瀏覽量

71304

發(fā)布評論請先 登錄

集成2.4 GHz VCO的12路LVDS/24 CMOS輸出時鐘發(fā)生器AD9522-1/PCBZ

集成2.2 GHz VCO12路LVDS/24 CMOS輸出時鐘發(fā)生器AD9522-2/PCBZ

12路LVDS/24 CMOS輸出時鐘發(fā)生器AD9522-3/PCBZ

AD9522-4 12路LVDS/24路CMOS輸出時鐘發(fā)生器,集成1.6 GHz VCO

AD9520-0:12路LVPECL/24路CMOS輸出時鐘發(fā)生器,集成2.8 GHz VCO

AD9522-1:12 LVDS/24 CMOS輸出時鐘發(fā)生器,集成2.4 GHz壓控振蕩器數(shù)據(jù)表

AD9522-0:12集成2.8 GHz壓控振蕩器數(shù)據(jù)表的LVDS/24 CMOS輸出時鐘發(fā)生器

AD9522-3:12集成2 GHz壓控振蕩器數(shù)據(jù)表的LVDS/24 CMOS輸出時鐘發(fā)生器

AD9522-5:12 LVDS/24 CMOS輸出時鐘發(fā)生器數(shù)據(jù)表

AD9522-4:12集成1.6 GHz壓控振蕩器數(shù)據(jù)表的LVDS/24 CMOS輸出時鐘發(fā)生器

集成2.2 GHz VCO數(shù)據(jù)表的AD9522-2:12 LVDS/24 CMOS輸出時鐘發(fā)生器

AD9517-4:12輸出時鐘發(fā)生器,集成1.6 GHz壓控振蕩器數(shù)據(jù)表

AD9520-4:12集成1.6 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時鐘發(fā)生器

AD9522-1 12路LVDS/24路CMOS輸出時鐘發(fā)生器,集成2.4 GHz VCO技術(shù)手冊

AD9522-3 12路LVDS/24路CMOS輸出時鐘發(fā)生器,集成2 GHz VCO技術(shù)手冊

AD9522-4 12路LVDS/24路CMOS輸出時鐘發(fā)生器,集成1.6 GHz VCO技術(shù)手冊

AD9522-4 12路LVDS/24路CMOS輸出時鐘發(fā)生器,集成1.6 GHz VCO技術(shù)手冊

評論