該CDCVF2510A是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。該CDCVF2510A使用鎖相環 (PLL) 將反饋 (FBOUT) 輸出在頻率和相位上精確對齊到時鐘 (CLK) 輸入信號。它專為與同步 DRAM 一起使用而設計。該CDCVF2510A工作電壓為 3.3V VCC還提供集成串聯阻尼 電阻器使其成為驅動點對點負載的理想選擇。

一組10個輸出提供10個低偏斜、低抖動的CLK拷貝,輸出信號占空比調整為50%,與CLK的占空比無關。輸出通過控制(G)輸入使能或禁用。當G輸入為高電平時,輸出與CLK相位和頻率切換;當G輸入為低電平時,輸出被禁用至邏輯低電平狀態。當沒有輸入信號(< 1 MHz)施加到CLK時,器件會自動進入掉電模式;輸出進入低電平狀態。

*附件:cdcvf2510a.pdf

與許多包含 PLL 的產品不同,該CDCVF2510A不需要外部 RC 網絡。片內包含用于PLL的環路濾波器,可最大限度地減少元件數量、電路板空間和成本。

由于它基于PLL電路,因此CDCVF2510A需要穩定時間才能實現反饋信號與參考信號的鎖相。在上電和施加固定頻率、CLK 上的固定相位信號或對 PLL 基準或反饋信號進行任何更改后,需要此穩定時間。PLL 可以通過捆扎 AV 來繞過CC接地用作簡單的時鐘緩沖器。

該CDCVF2510A的特點是在 0°C 至 85°C 范圍內工作。

特性

- 設計符合并超過 PC133 SDRAM 注冊 DIMM 規范修訂版 1.1

- 兼容擴頻時鐘

- 工作頻率 20 MHz 至 175 MHz

- 66 MHz至166 MHz時的靜態相位誤差分布為±125 ps

- 66 MHz至166 MHz時的抖動(cyc-cyc)為|70|PS

- 先進的深亞微米工藝使功耗比當前一代 PC133 器件降低 40% 以上

- 自動頻率檢測以禁用設備(掉電模式)

- 提供塑料 24 引腳 TSSOP

- 將一個時鐘輸入分配到一個包含 10 個輸出的組

- 外部反饋 (FBIN) 端子用于將輸出同步到時鐘輸入

- 片上25-

串聯阻尼電阻

串聯阻尼電阻 - 無需外部 RC 網絡

- 工作電壓為 3.3 V

- 應用

- DRAM 應用

- 基于PLL的時鐘分配器

- 非PLL時鐘緩沖器

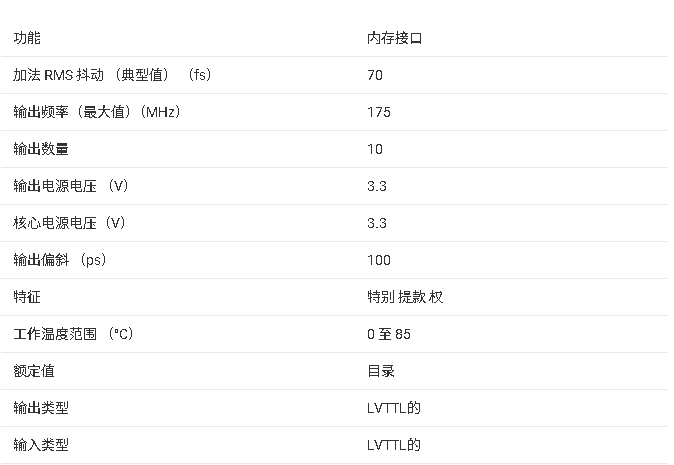

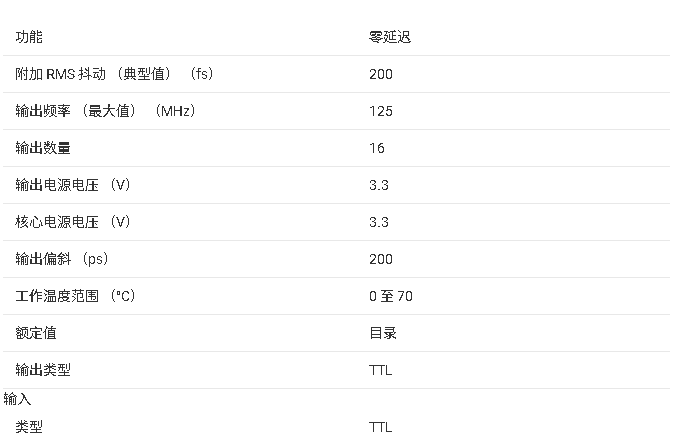

參數

?1. 產品概述?

CDCVF2510A是德州儀器(TI)設計的高性能、低偏移、低抖動的鎖相環(PLL)時鐘驅動器,專為同步DRAM應用優化。核心特性包括:

- ?工作頻率?:20 MHz至175 MHz,兼容PC133 SDRAM標準。

- ?低功耗?:先進深亞微米工藝,功耗比同類產品低40%。

- ?集成功能?:內置25Ω阻尼電阻,無需外部RC網絡,簡化設計。

- ?封裝?:24引腳TSSOP(PW封裝),支持工業溫度范圍(0°C至85°C)。

?2. 關鍵特性?

- ?靜態相位誤差?:±125 ps(66 MHz至166 MHz)。

- ?周期抖動?:≤70 ps(同頻段)。

- ?自動節能?:檢測輸入信號<1 MHz時進入低功耗模式。

- ?反饋同步?:通過FBIN/FBOUT引腳實現零相位誤差同步。

?3. 功能描述?

- ?輸出控制?:10路低偏移時鐘輸出(1Y0-1Y9),由G引腳使能(高電平有效)。

- ?PLL旁路?:AVCC接地時可繞過PLL,作為普通時鐘緩沖器使用。

- ?穩定時間?:上電或頻率變化后需1 ms鎖定時間。

?4. 電氣參數?

- ?供電電壓?:3.3 V±0.3 V,最大耐受4.3 V。

- ?輸出驅動能力?:±12 mA(高/低電平)。

- ?動態電流?:隨頻率線性增加(見圖9-10典型曲線)。

?5. 應用場景?

- ?DRAM模塊?:滿足注冊DIMM規范。

- ?時鐘分配?:適用于PLL或非PLL架構的時鐘樹設計。

?6. 設計注意事項?

- ?布局建議?:FBIN與FBOUT走線需短(推薦5mm,50Ω阻抗)。

- ?散熱?:結溫限值125°C,熱阻θJA=114.5°C/W。

-

鎖相環

+關注

關注

36文章

635瀏覽量

91211 -

電阻器

+關注

關注

22文章

4243瀏覽量

65501 -

pll

+關注

關注

6文章

985瀏覽量

138279 -

輸入信號

+關注

關注

0文章

559瀏覽量

13198 -

時鐘驅動器

+關注

關注

0文章

124瀏覽量

14401

發布評論請先 登錄

?CDCVF25081 3.3-V 鎖相環時鐘驅動器技術文檔總結

?CDCVF2509 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDC516 3.3V相位鎖定環時鐘驅動器技術文檔總結

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

評論