概述

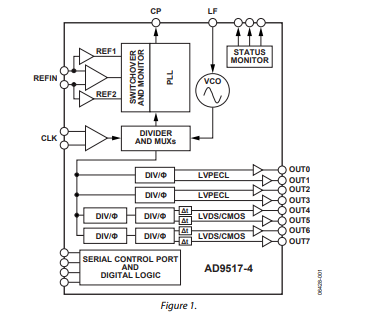

AD9517-4提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為1.45 GHz至1.80 GHz。也可以使用高達2.4 GHz的外部VCO/VCXO。

數據表:*附件:AD9517-4 12路輸出時鐘發生器,集成1.6GHz VCO技術手冊.pdf

AD9517-4具有出色的低抖動和相位噪聲特性,可極大地提升數據轉換器的性能,并且也有利于其它相位噪聲和抖動要求嚴苛的應用。

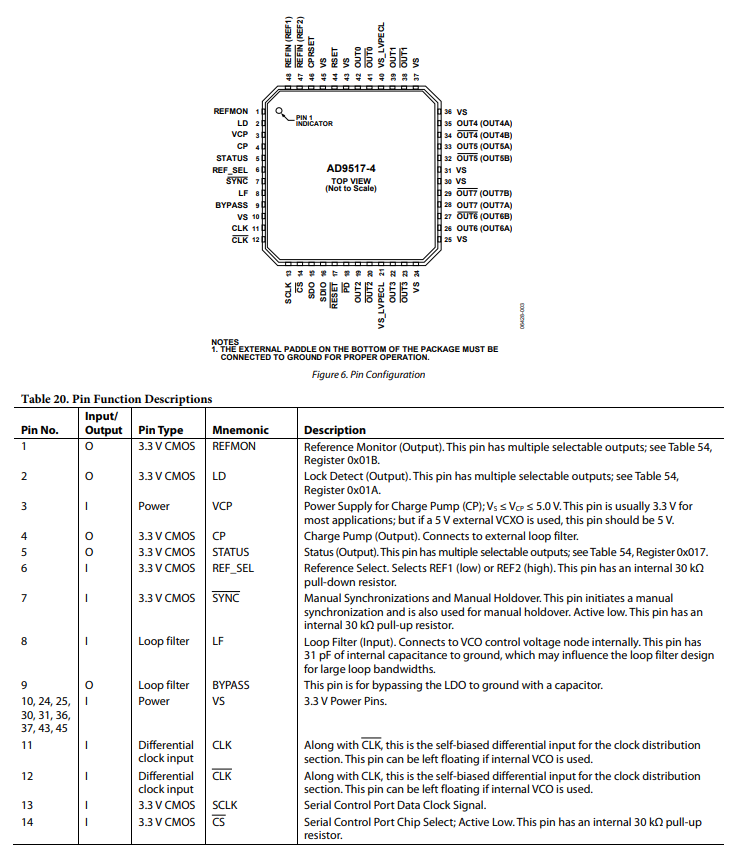

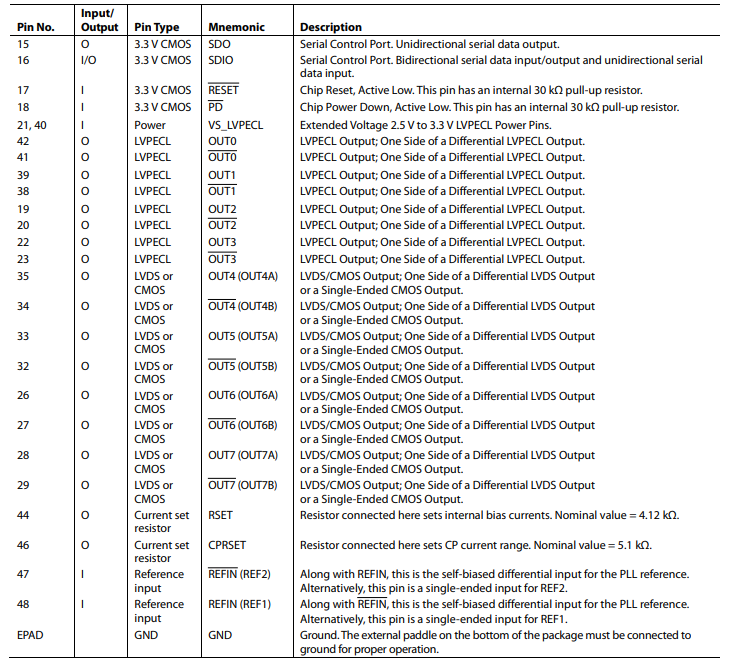

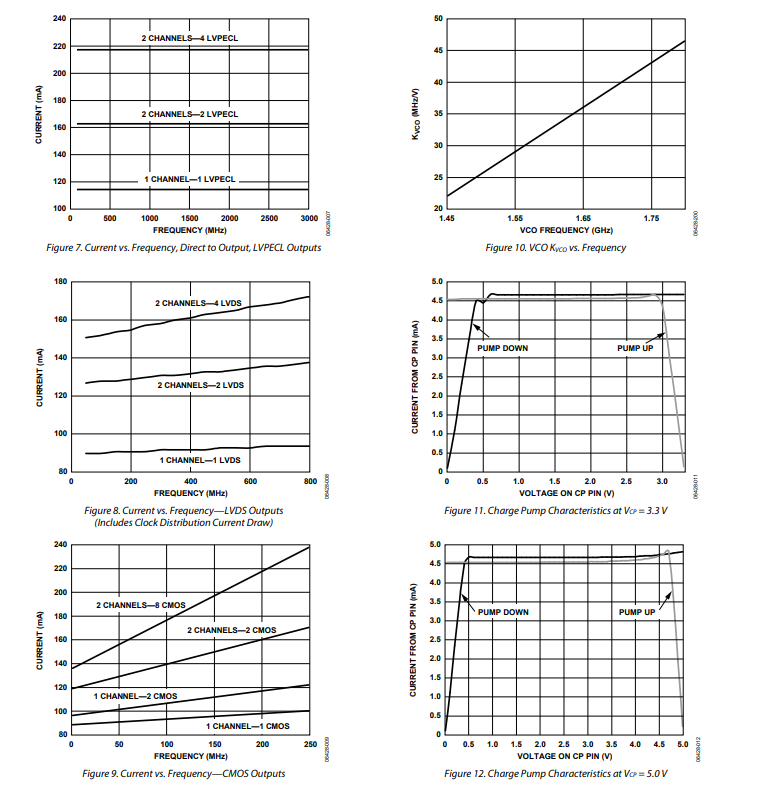

AD9517-4具有四路LVPECL輸出(分為兩對)和四路LVDS輸出(分為兩對)。可以將每路LVDS輸出重新配置為兩路CMOS輸出。LVPECL輸出的工作頻率達1.6 GHz,LVDS輸出的工作頻率達800 MHz,CMOS輸出的工作頻率達250 MHz。

每對輸出均有分頻器,其分頻比和粗調延遲(或相位)均可以設置。LVPECL輸出的分頻范圍為1至32。LVDS/CMOS輸出的分頻范圍最高可達1024。

AD9517-4提供48引腳LFCSP封裝,可以采用3.3 V單電源供電。將電荷泵電源(VCP)與5V電壓相連時,可以使用外部VCO,它需要更寬的電壓范圍。獨立的LVPECL電源可以為2.5 V至3.3 V(標稱值)。

AD9517-4的額定工作溫度范圍為?40°C至+85°C工業溫度范圍。

應用

- 低抖動、低相位噪聲時鐘分配

- 10/40/100 Gb/s網絡線路卡,包括SONET、同步以太網、OTU2/3/4

- 前向糾錯(G.710)

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE提供時鐘

- 高性能無線收發器

- 自動測試設備(ATE)和高性能儀器儀表

特性

- 低相位噪聲、鎖相環

片內VCO的調諧頻率范圍為1.45 GHz至1.80 GHz

可選外部VCO/VCXO,最高達2.4 GHz

1路差分或2路單端基準輸入

參考監控功能

自動/手動基準電壓源切換/保持模式

自動從保持狀態恢復

支持最高250 MHz的LVPECL、LVDS或CMOS基準

可編程PFD路徑延遲

可選數字或模擬時鐘檢測 - 兩對1.6 GHz LVPECL輸出

每對輸出共用1至32分頻器和粗調相位延遲

加性輸出抖動:225 fS均方根值

通道間偏斜成對輸出小于10 ps - 兩對800 MHz LVDS時鐘輸出

每對輸出共用兩個級聯的1至32分頻器和粗調相位延遲

加性輸出抖動:275S均方根值

可以精調每路LVDS輸出的延遲(Δt) - 8路250 MHz CMOS輸出(每路LVDS輸出對應兩路)

- 上電時所有輸出自動同步

- 欲了解更多特性,請參考數據手冊

框圖

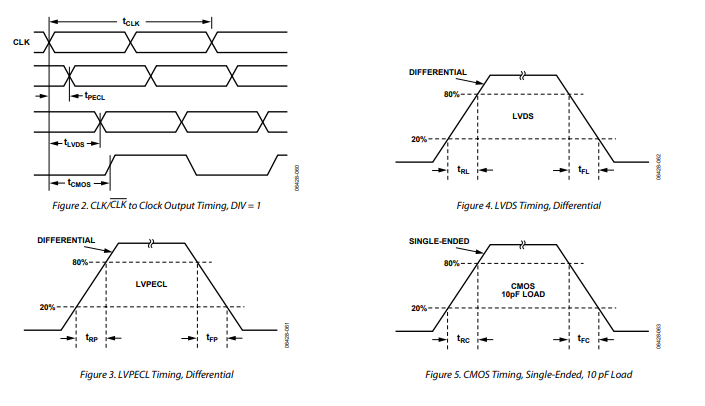

時序圖

引腳配置描述

典型性能特征

鎖相環(PLL)

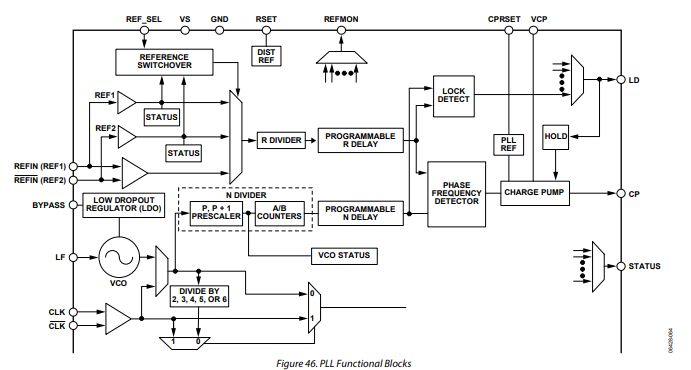

AD9517集成了片內鎖相環(PLL)和片內壓控振蕩器(VCO)。PLL模塊既可以與片內VCO配合使用,構建完整的鎖相環路,也可以與外部VCO或壓控晶體振蕩器(VCXO)搭配。PLL需要一個外部環路濾波器,該濾波器通常由少量電容和電阻組成。環路濾波器的配置和組件對于確立工作PLL的環路帶寬和穩定性至關重要。

AD9517的PLL在從輸入參考頻率生成時鐘頻率方面非常有用。這包括將參考頻率轉換為更高頻率,以便進行后續的分頻和分配。此外,PLL還可用于清理輸入抖動,并抑制噪聲參考信號的相位噪聲。PLL的確切參數和鎖定動態特性因應用而異。AD9517的PLL具有高度的靈活性和深度,能夠在眾多不同的應用和信號環境中發揮作用。

PLL的配置

AD9517允許對PLL進行靈活配置,以適應各種參考頻率、鑒頻鑒相器(PFD)比較頻率、VCO頻率(內部或外部VCO/VCXO)以及鎖相環動態特性。這是通過多種設置實現的,包括R分頻器、N分頻器、PFD極性(僅適用于外部VCO/VCXO)、防反沖脈沖寬度、電荷泵電流、內部VCO或外部VCO/VCXO的選擇,以及環路帶寬。這些設置通過可編程寄存器進行管理(見表52和表54),同時也與外部環路濾波器的設計相關。

PLL的成功運行和良好性能在很大程度上取決于PLL設置的正確配置。外部環路濾波器的設計對于PLL的正常運行至關重要。深入了解PLL理論和設計有助于優化性能。ADIsimCLK?(V1.2或更高版本)是一款免費程序,可幫助進行AD9517的設計,探索其功能特性,并設計PLL環路濾波器,可在www.analog.com/clocks獲取。

鑒頻鑒相器(PFD)

PFD接收來自R計數器和N計數器的輸入,并產生與二者之間相位和頻率差成比例的輸出。PFD包括一個可編程延遲元件,用于控制防反沖脈沖的寬度。該脈沖可確保PFD傳輸功能中不存在死區,并將參考雜散降至最低。防反沖脈沖寬度由寄存器0x017[1:0]設置。

需要注意的是,PFD存在允許的最大頻率限制,這反過來又決定了正確的防反沖脈沖設置。防反沖脈沖設置在表2的鑒頻鑒相器參數中有詳細說明。

-

pll

+關注

關注

6文章

985瀏覽量

138328 -

時鐘

+關注

關注

11文章

1998瀏覽量

135199 -

VCO

+關注

關注

14文章

320瀏覽量

71415 -

ad9517

+關注

關注

0文章

4瀏覽量

2084

發布評論請先 登錄

AD9517-4 12路輸出時鐘發生器,集成1.6 GHz VCO

AD9520-0:12路LVPECL/24路CMOS輸出時鐘發生器,集成2.8 GHz VCO

集成2.2 GHz VCO數據表的AD9522-2:12 LVDS/24 CMOS輸出時鐘發生器

AD9517-4 12路輸出時鐘發生器,集成1.6GHz VCO技術手冊

AD9517-4 12路輸出時鐘發生器,集成1.6GHz VCO技術手冊

評論