概述

AD9543支持現(xiàn)有和新興的ITU標(biāo)準(zhǔn),可通過服務(wù)提供商分包網(wǎng)絡(luò)傳輸頻率、相位和當(dāng)前時間。

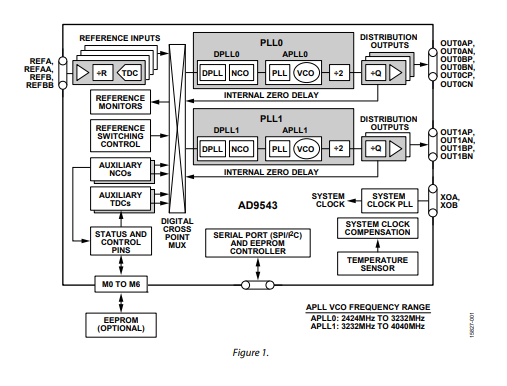

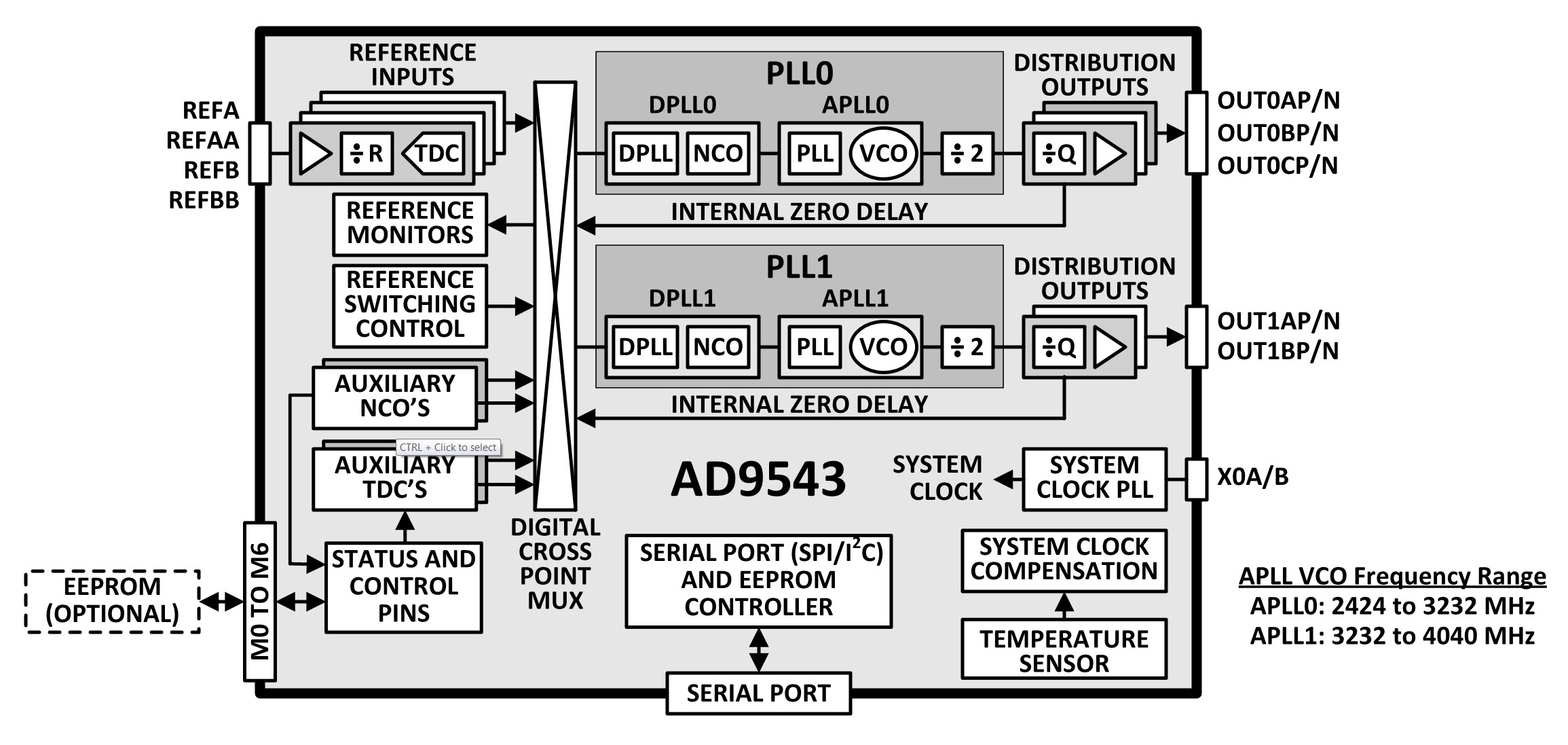

AD9543的10個時鐘輸出與最多四個輸入基準(zhǔn)電壓源之一同步。數(shù)字鎖相環(huán)(DPLL)可減少與外部基準(zhǔn)電壓源相關(guān)的時序抖動。借助數(shù)字控制環(huán)路和保持電路,即使所有參考輸入都失效,也能持續(xù)產(chǎn)生低抖動輸出信號。

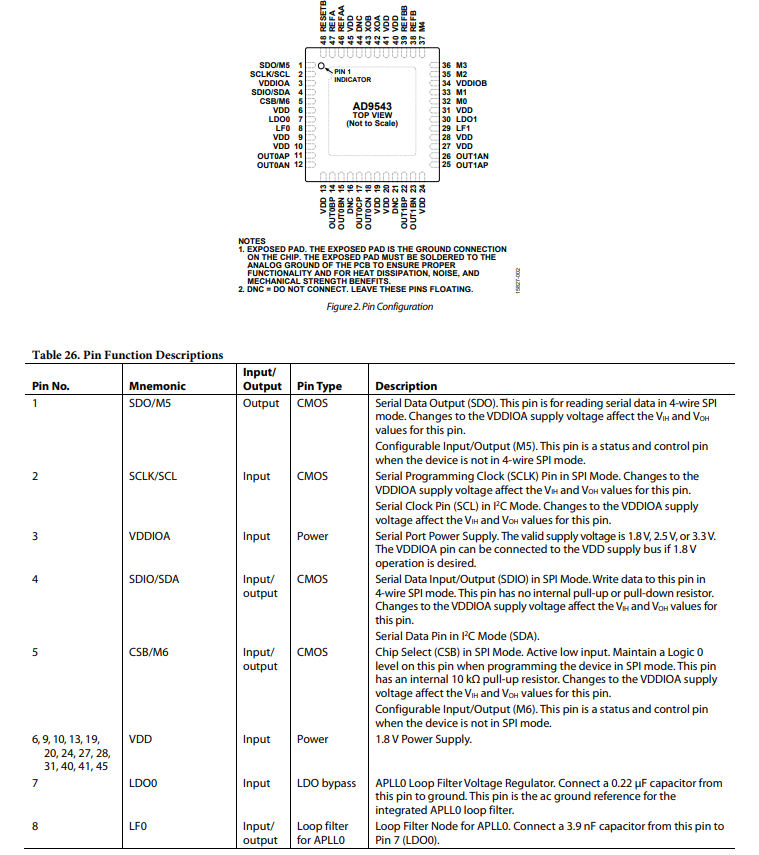

AD9543采用48引腳LFCSP (7 mm × 7 mm)封裝,額定溫度范圍為?40°C至+85°C。

請注意,在整篇數(shù)據(jù)手冊中,多功能引腳(如SDO/M5)由整個引腳名稱或引腳的單個功能表示;例如M5即表示僅與此功能相關(guān)。

數(shù)據(jù)表:*附件:AD9543四通道輸入、10路輸出、雙通道DPLL IEEE 1588同步器和抖動清除器技術(shù)手冊.pdf

應(yīng)用

- PTP (IEEE 1588) 和 SyncE 抖動清除和同步

- 光傳輸網(wǎng)絡(luò)(OTN)、SDH、宏和小型蜂窩基站

- 具有抖動凈化功能的OTN映射/解映射

- 小型基站時鐘,包括基帶和無線電

- Stratum 2、Stratum 3e 和 Stratum 3 保持、抖動清除及相位瞬態(tài)控制

- JESD204B 支持模數(shù)轉(zhuǎn)換器 (ADC) 和數(shù)模轉(zhuǎn)換器 (DAC) 時鐘

- 有線基礎(chǔ)設(shè)施

- 載波以太網(wǎng)

特性

- 雙路DPLL可同步2 kHz至750 MHz物理層時鐘,提供高噪聲參考源的頻率轉(zhuǎn)換以及抖動凈化功能

- 符合 ITU-T G.8262 和 Telcordia GR-253 標(biāo)準(zhǔn)

- 支持 Telcordia GR-1244、ITU-T G.812、G.813、G.823、G.824、G.825 和 G.8273.2

- 連續(xù)頻率監(jiān)控和參考驗(yàn)證,頻率偏差低至50 ppb

- 兩個DPLL具有24位小數(shù)分頻器和24位可編程模數(shù)

- 可編程數(shù)字環(huán)路濾波器帶寬:10^?4^ Hz 至 1850 Hz

- 兩個獨(dú)立的可編程輔助NCO(1 Hz至65,535 Hz,分辨率 < 1.4 × 10?12 Hz),適合IEEE 1588

- PTP 應(yīng)用中的第 2 版伺服反饋

- 自動和手動保持和參考切換,提供零延遲、無中斷或相位増建操作

- 基于優(yōu)先級的可編程參考切換,支持手動、自動恢復(fù)和自動非恢復(fù)模式

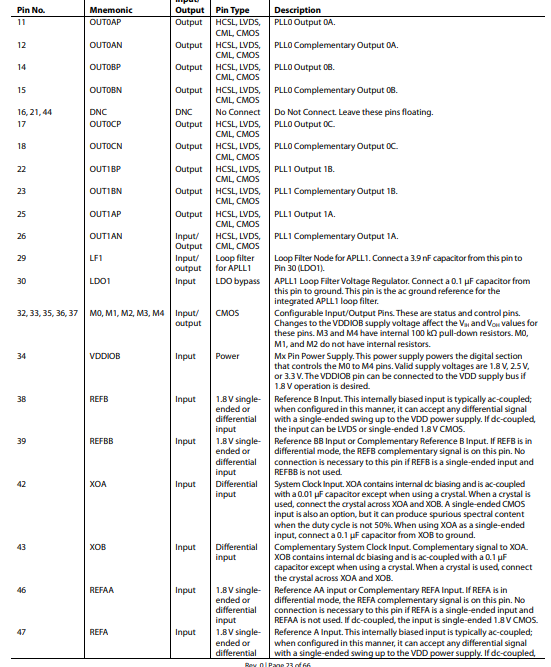

- 5對時鐘輸出引腳,每對引腳均可用作差分LVDS/HCSL/CML或2路單端輸出(1 Hz至500 MHz)

- 2 個差分或 4 個單端輸入基準(zhǔn)電壓源

- 交叉點(diǎn)多路復(fù)用器將基準(zhǔn)輸入與 PLL 互連

- 支持嵌入式(調(diào)制)輸入/輸出時鐘信號

- 快速 DPLL 鎖定模式

- 提供內(nèi)部功能,結(jié)合晶振或晶體振蕩器的低相位噪聲以及TCXO或OCXO的頻率穩(wěn)定性和精度

- 為自主初始化提供外部EEPROM支持

- 1.8 V 單電源供電,具有內(nèi)部調(diào)節(jié)特性

- 內(nèi)置溫度監(jiān)控器/警報和溫度補(bǔ)償,可增強(qiáng)零延遲性能

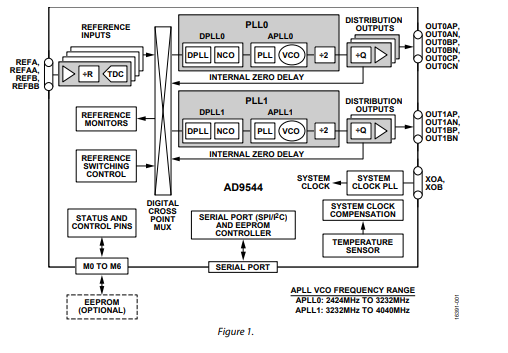

功能框圖

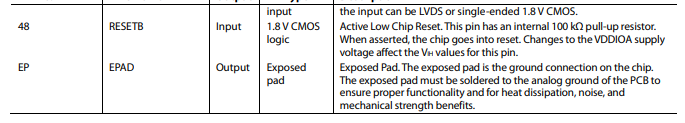

引腳配置描述

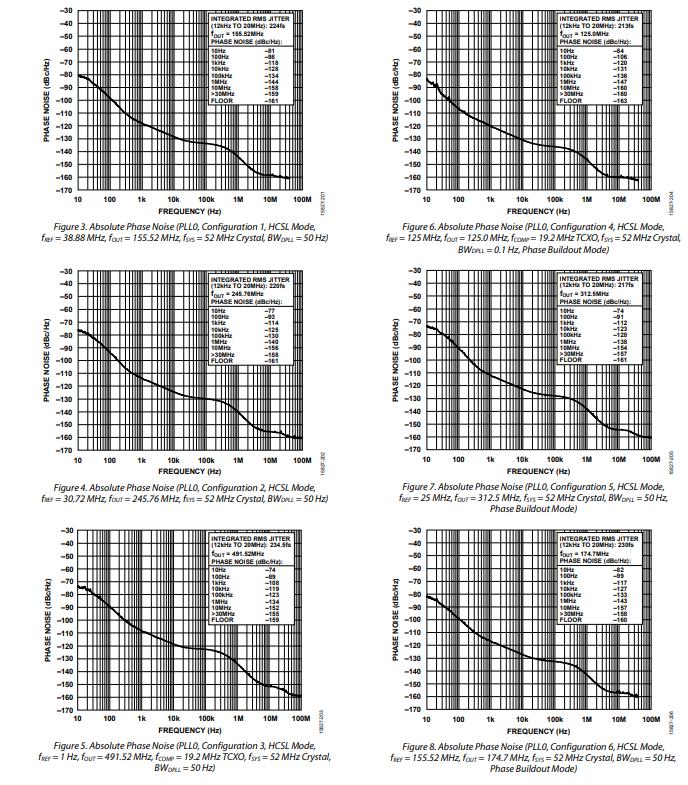

典型性能特征

應(yīng)用信息

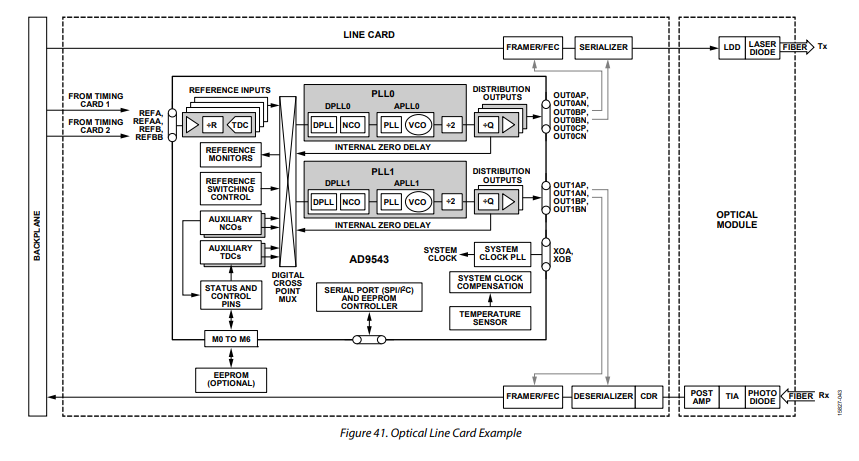

光網(wǎng)絡(luò)線路卡

在該應(yīng)用(如圖41所示)中,AD9543有多種應(yīng)用方式。

在環(huán)路定時(廣域網(wǎng))模式下,AD9543的其中一個數(shù)字鎖相環(huán)(DPLL)鎖定到時鐘數(shù)據(jù)恢復(fù)(CDR)電路,用于去除接收路徑上的抖動,并將該時鐘發(fā)送至中央定時卡和成幀器。在某些應(yīng)用中,AD9543還可執(zhí)行多種頻率轉(zhuǎn)換任務(wù),如乘以或除以前向糾錯(FEC)比率,以及/或者從間隙時鐘中去除抖動。另一個DPLL用于清理抖動,并為發(fā)射路徑提供時鐘。

其他任務(wù)包括對來自定時卡的參考時鐘進(jìn)行頻率轉(zhuǎn)換和抖動清理,以及無縫管理從定時卡1到定時卡2的參考切換。

鑒于光線路卡協(xié)議和功能不斷發(fā)展,本節(jié)列出的功能絕非詳盡無遺。

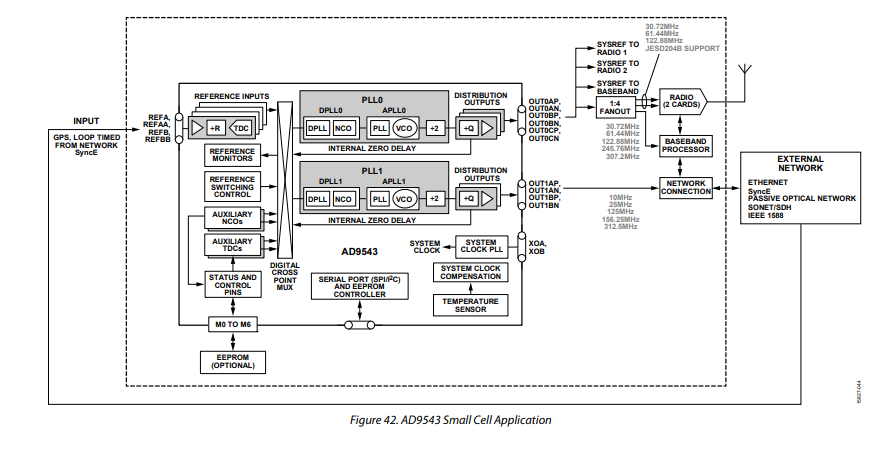

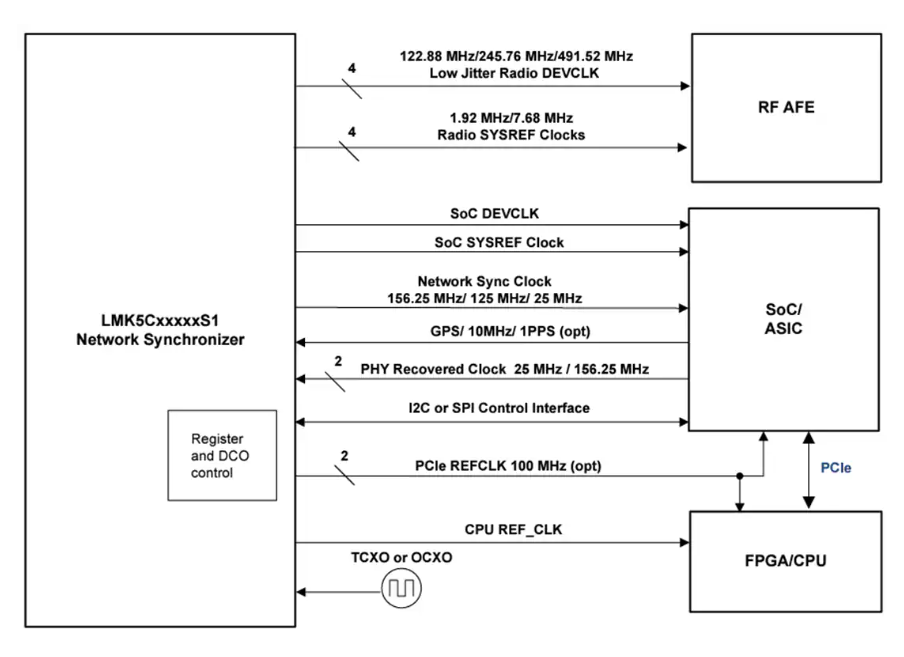

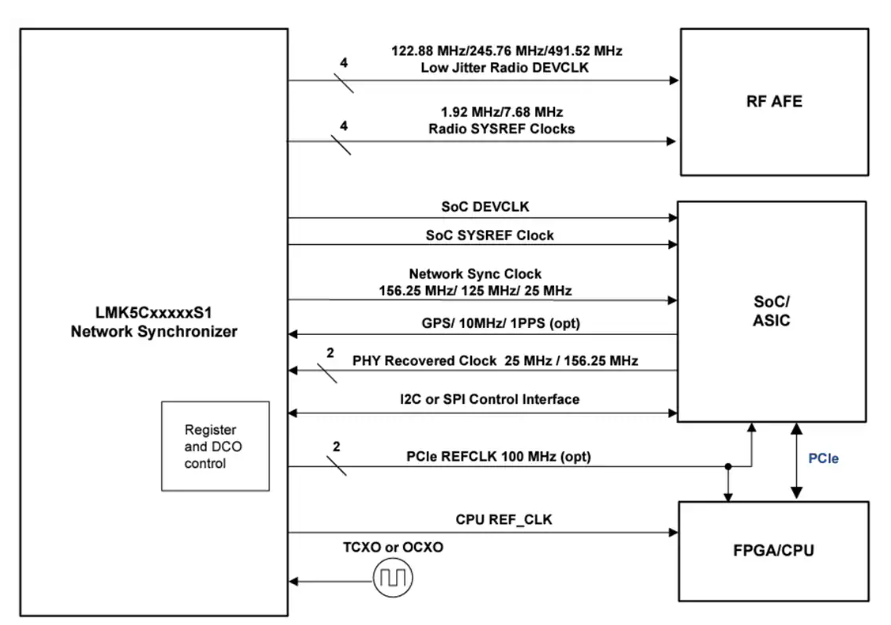

小基站

在該應(yīng)用(如圖42所示)中,AD9543為小基站的基帶單元提供所有同步功能。其內(nèi)置的JESD204B支持特性,使設(shè)計具備特別緊湊且高效的優(yōu)勢。

AD9543能夠鎖定到以下任意信號源:全球定位系統(tǒng)(GPS)、同步以太網(wǎng)(SyncE),和/或IEEE 1588(此情況需單獨(dú)的IEEE 1588伺服器和軟件棧),或針對SONET/SDH回傳的線路定時。有關(guān)使用AD9543實(shí)現(xiàn)IEEE 1588版本2或版本3的詳細(xì)信息,請見圖43。AD9543在與IEEE 1588伺服器和軟件棧配合使用時,也可按照輔助部分定時操作的定義,采用這些輸入源(即SyncE、GPS)的混合組合方式運(yùn)行。

AD9543的PLL0為設(shè)備時鐘提供支持,并且可用于為多達(dá)四個系統(tǒng)參考時鐘提供信號,這些時鐘可用于為無線收發(fā)器(如AD9371)提供時鐘。

AD9543的PLL1為回傳接口提供時鐘,還可根據(jù)需要選擇為CPU接口提供時鐘。

AD9543的電可擦可編程只讀存儲器(EEPROM)支持功能,使AD9543在加電時能夠自動加載其配置。

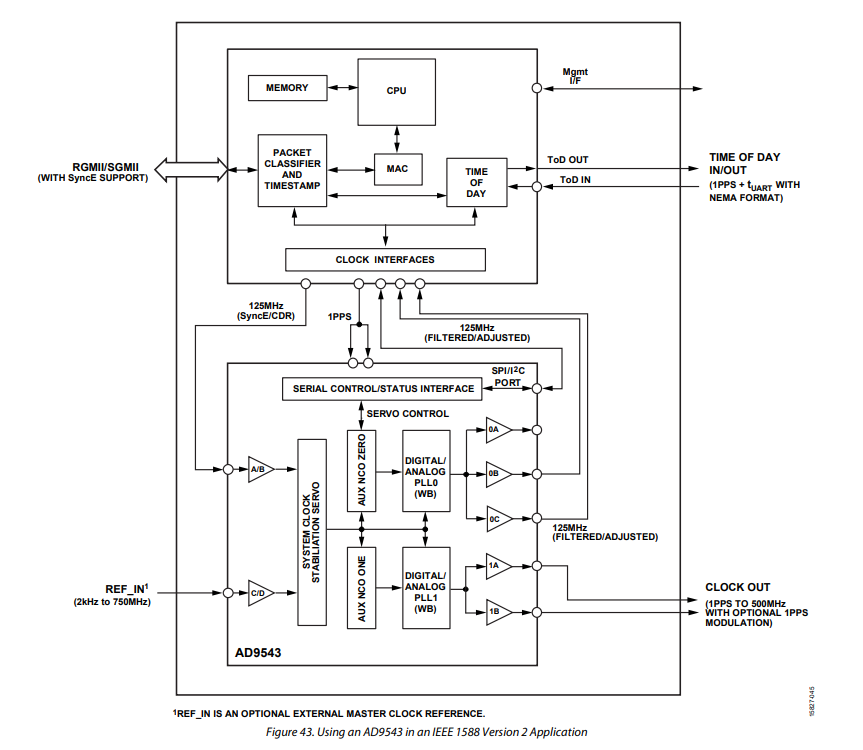

IEEE 1588伺服器

在該應(yīng)用(如圖43所示)中,AD9543為電信大樓通信(T - BC)中的IEEE 1588伺服器和軟件棧提供所有的抖動消除、相移和同步功能,支持混合應(yīng)用。該系統(tǒng)還可充當(dāng)IEEE 1588主時鐘和從時鐘。

AD9543的PLL0提供經(jīng)過濾波的125 MHz同步以太網(wǎng)(SyncE)時鐘。

AD9543的PLL1提供1脈沖每秒(1 pps)至500 MHz的輸出時鐘,具備高分辨率輸出相位調(diào)整和轉(zhuǎn)換速率限制功能。例如,這使得GPS信號能夠在適當(dāng)?shù)木_時間協(xié)議(PTP)軟件支持下進(jìn)行濾波和校正,從而提供PTP不對稱校正。

AD9543的性能和特性使其成為實(shí)現(xiàn)最新IEEE 1588功能,以及4G和5G無線通信中最新國際電信聯(lián)盟 - 電信標(biāo)準(zhǔn)化部門(ITU - T)數(shù)據(jù)包同步相關(guān)標(biāo)準(zhǔn)的理想選擇。

-

數(shù)字控制

+關(guān)注

關(guān)注

2文章

200瀏覽量

26917 -

DPLL

+關(guān)注

關(guān)注

1文章

35瀏覽量

14391 -

清除器

+關(guān)注

關(guān)注

0文章

56瀏覽量

6109 -

同步器

+關(guān)注

關(guān)注

1文章

117瀏覽量

15683

發(fā)布評論請先 登錄

可實(shí)現(xiàn)四通道模擬輸入和雙通道模擬輸出的參考設(shè)計

TLK3134 具有集成時鐘抖動清除器的高靈活性四通道Ser

美高森美IEEE1588平臺新增超低抖動網(wǎng)絡(luò)同步器產(chǎn)品

AD9543 四通道輸入、10路輸出、雙通道DPLL/IEEE 1588同步器和抖動清除器

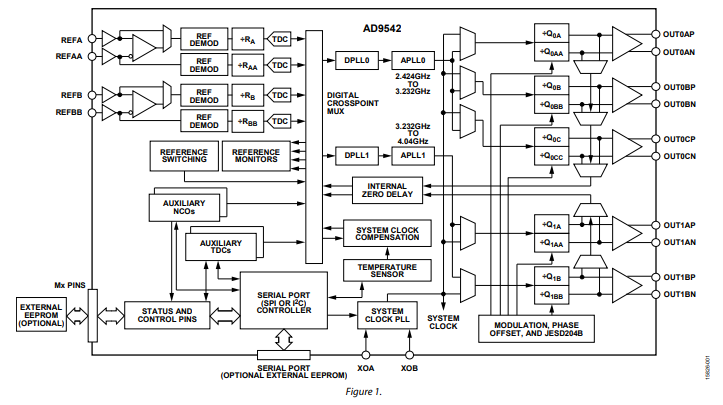

AD9542:四輸入、五輸出、雙DPLL同步器和自適應(yīng)時鐘轉(zhuǎn)換器產(chǎn)品手冊

AD9545:快速輸入,10輸出,雙DPLL/IEEE1588 1小步同步和Jetter Clearan數(shù)據(jù)Sheet

AD9544四通道輸入、10路輸出、雙通道DPLL、1pps同步器和抖動清除器技術(shù)手冊

AD9554四路PLL、四通道輸入、八通道輸出多服務(wù)線路卡自適應(yīng)時鐘轉(zhuǎn)換器技術(shù)手冊

AD9542雙路DPLL、四路輸入、10路輸出、多服務(wù)線路卡時鐘轉(zhuǎn)換器和抖動清除器技術(shù)手冊

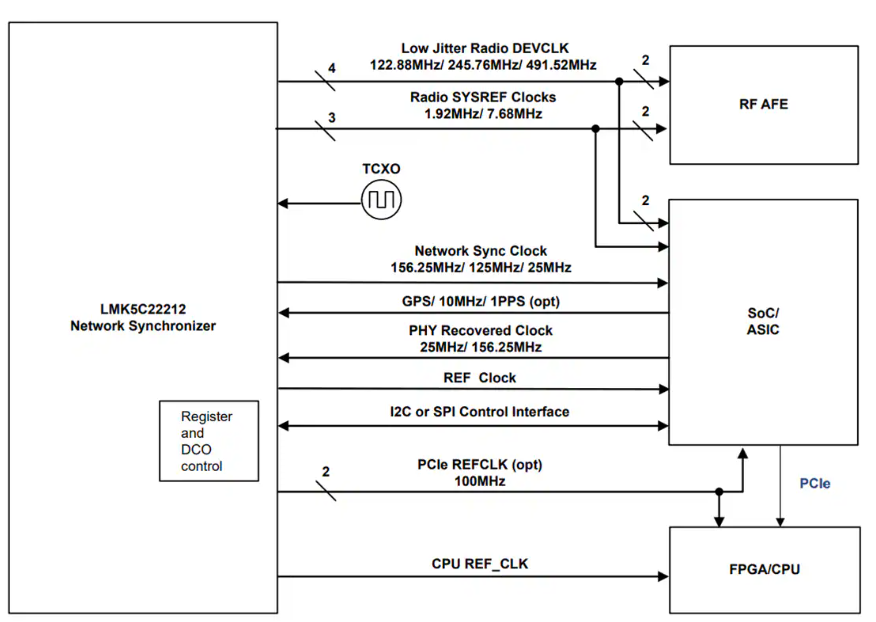

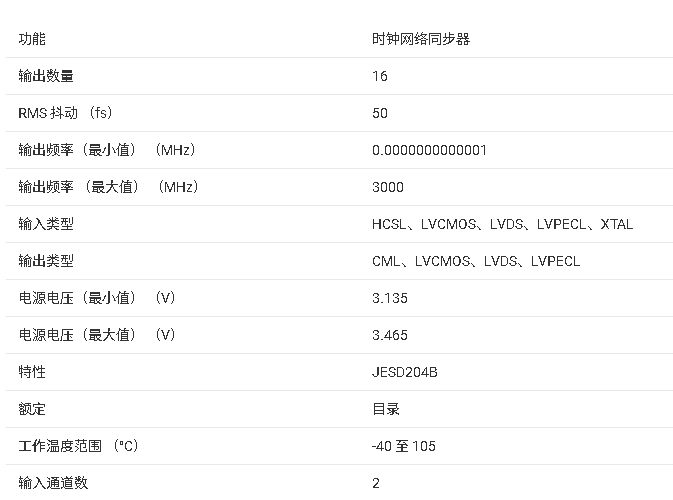

Texas Instruments LMK5C22212AS1網(wǎng)絡(luò)同步器數(shù)據(jù)手冊

Texas Instruments LMK5C33216AS1網(wǎng)絡(luò)同步器數(shù)據(jù)手冊

Texas Instruments LMK5C33414AS1網(wǎng)絡(luò)同步器數(shù)據(jù)手冊

?LMK5C33216A 網(wǎng)絡(luò)同步器與抖動清除器總結(jié)

AD9543四通道輸入、10路輸出、雙通道DPLL/IEEE 1588同步器和抖動清除器技術(shù)手冊

AD9543四通道輸入、10路輸出、雙通道DPLL/IEEE 1588同步器和抖動清除器技術(shù)手冊

評論