概述

LTC6952 是一款高性能、超低抖動 JESD204B/C 時鐘生成和分配 IC。該器件包括一個鎖相環 (PLL) 內核,由基準分頻器、具有鎖相指示器的相位頻率檢波器 (PFD)、超低噪聲充電泵和整數反饋分頻器構成。LTC6952 的 11 個輸出可配置為最多 5 個 JESD204B/C subclass 1 器件時鐘/SYSREF 對以及一個通用輸出,或者就是 11 個面向非 JESD204B/C 應用的通用時鐘輸出。每個輸出都有自己的可單獨編程分頻器和輸出驅動器。所有輸出也可以采用單獨的粗略半周期數字延遲和精細模擬時間延遲實現同步,并設定為精確的相位對齊。

對于需要 11 個以上總輸出的應用,可以使用 EZSync 或 ParallelSync 同步協議將多個 LTC6952 連接在一起。

數據表:*附件:LTC6952具有11個輸出并支持JESD204B JESD204C協議的超低抖動、4.5GHz PLL技術手冊.pdf

應用

- 高性能數據轉換器時鐘

- 無線基礎設施

- 測試和測量

特性

- JESD204B/C,子類 1 SYSREF 信號生成

- 低噪聲整數 N PLL

- 附加輸出抖動 < 6fs

RMS- (集成帶寬 = 12kHz 至 20MHz,f = 4.5GHz)

- 附加輸出抖動 65fs

RMS(ADC SNR 方法) - EZSync ^?^ 、ParallelSync^?^ 多芯片同步

- –229dBc/Hz 歸一化帶內相位本底噪聲

- –281dBc/Hz 歸一化帶內 1/f 噪聲

- 11 個獨立低噪聲輸出,具有可編程粗數字延遲和精細模擬延遲

- 靈活的輸出可以用作套件時鐘或 SYSREF 信號

- 基準輸入頻率達 500MHz

- LTC6952Wizard^?^ 軟件設計工具支持

- 工作結溫范圍為 –40oC 至 125°C

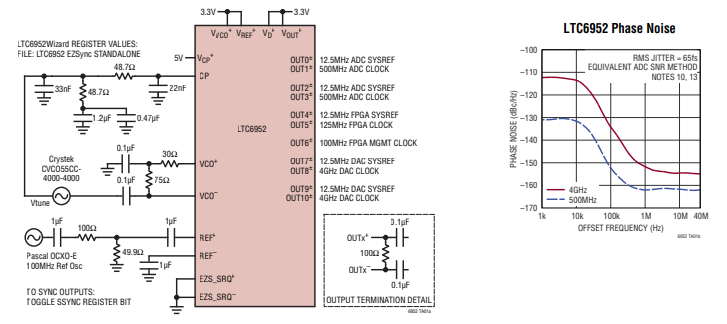

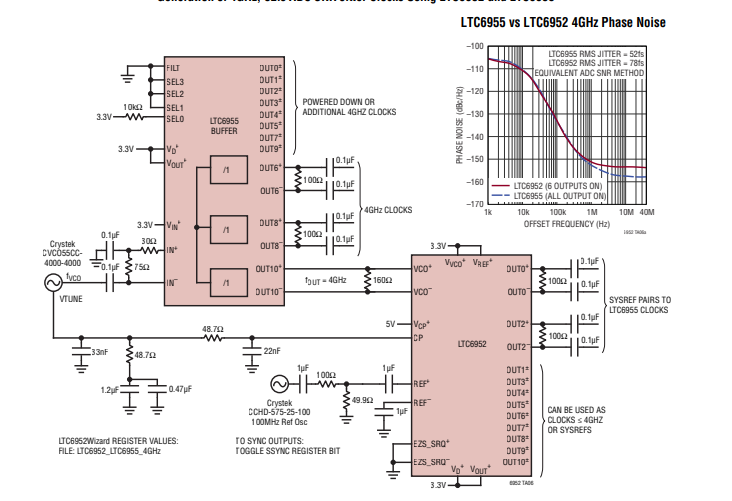

典型應用

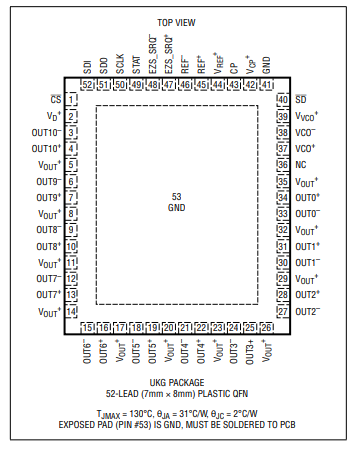

引腳圖

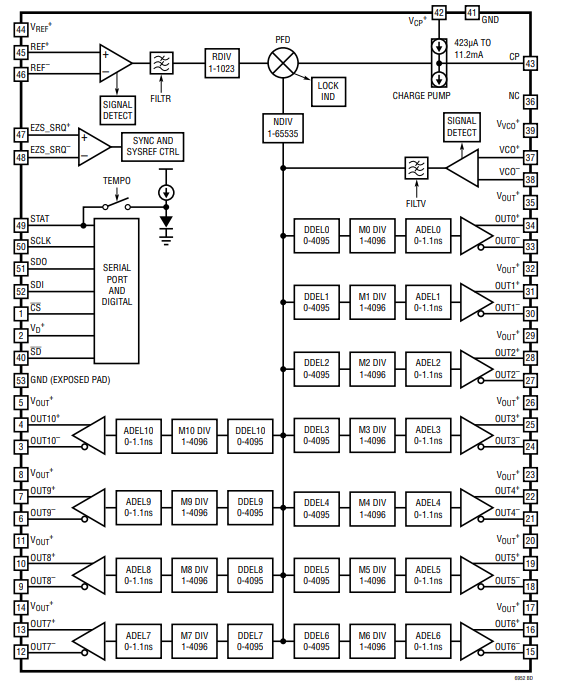

框圖

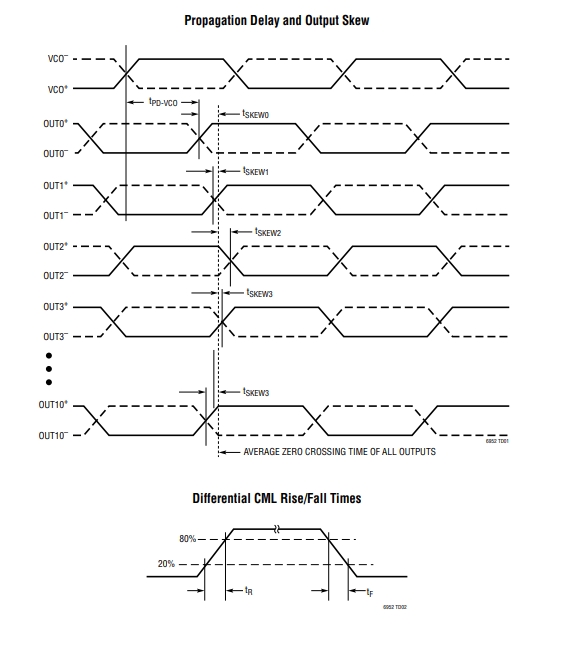

時序圖

應用電路

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

分頻器

+關注

關注

43文章

536瀏覽量

53349 -

pll

+關注

關注

6文章

981瀏覽量

138155 -

時鐘

+關注

關注

11文章

1971瀏覽量

134984

發布評論請先 登錄

相關推薦

熱點推薦

JESD204B的系統級優勢

的引腳數。因此它能獲得工程師的青睞和關注也就不足為奇了,它具備如下系統級優勢:更小的封裝尺寸與更低的封裝成本:JESD204B 不僅采用 8b10b 編碼技術串行打包數據,而且還有助于支持

發表于 09-18 11:29

JESD204B串行接口時鐘的優勢

都是基于這個版本設計的。本文就以JESD204B subclass1 來討論時鐘的時序需要以及TI 時鐘芯片方案的實現。任何一個串行協議都離不開幀和同步,JESD204B 也不例外,也

發表于 06-19 05:00

帶JESD204B輸出的14位170Msps雙通道ADC

DC1974A-C,LTC2122演示板,14位,170Msps雙通道ADC,帶JESD204B輸出。演示電路1974A-C

發表于 06-20 08:05

JESD204C的標準和新變化

的選項。完整的JESD204C規范可通過 JEDEC獲得。 本入門文章由兩部分組成,旨在介紹JESD204C標準,著重說明其與JESD204B的不同之處,并詳細闡明為達成上述目標、提

發表于 01-01 07:44

JESD204B協議有什么特點?

和 FPGA 至 DAC 鏈路問題的協議部分,這兩種鏈路本來就是相同的 TX 至 RX 系統。作為一名應用工程師,所需要的就是了解其中的細微差別,這樣才能充分利用 JESD204B 通過現有 LVDS 和 CMOS 接口提供的優勢。J

發表于 04-06 06:53

如何采用系統參考模式設計JESD204B時鐘

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器

發表于 11-18 06:36

JESD204B協議介紹

欄目下閱讀了各種技術文章及其它博客文章,明白了為什么 JESD204B 是 LVDS 和 CMOS 接口的后續產品。有一個沒有深入討論的主題就是解決 ADC 至 FPGA 和 FPGA

發表于 11-21 07:02

LTC6952 具有 11 個輸出和 JESD204B/JESD204C 支持的超低抖動 4.5GHz PLL

電子發燒友網為你提供ADI(ti)LTC6952相關產品參數、數據手冊,更有LTC6952的引腳圖、接線圖、封裝手冊、中文資料、英文資料,LTC69

發表于 02-22 15:53

LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持數據表

LTC6952:超低抖動、4.5 GHz PLL,帶11

發表于 04-22 15:52

?9次下載

LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個輸出和JESD204B/JESD204C支持數據表

LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個

發表于 05-19 15:23

?14次下載

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

電子發燒友網為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關產品參數、數據手冊,更有AD9207

發表于 10-16 19:02

從JESD204B升級到JESD204C時的系統設計注意事項

電子發燒友網站提供《從JESD204B升級到JESD204C時的系統設計注意事項.pdf》資料免費下載

發表于 09-21 10:19

?6次下載

JESD204B使用說明

能力更強,布線數量更少。 本篇的內容基于jesd204b接口的ADC和FPGA的硬件板卡,通過調用jesd204b ip核來一步步在FPGA內部實現高速ADC數據采集,jesd204b協議

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

LTC6953 是一款高性能、超低抖動的 JESD204B/JESD204C 時鐘分配 IC。LTC

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

評論