CDC2536是一款高性能、低偏斜、低抖動的時鐘驅動器。它使用鎖相環 (PLL) 將時鐘輸出信號在頻率和相位上精確對齊到時鐘輸入 (CLKIN) 信號。它專門設計用于同步 DRAM 和流行的微處理器,在配置為半頻輸出的輸出上以 50 MHz 至 100 MHz 或低至 25 MHz 的速度運行。該CDC2536工作電壓為 3.3V VCC設計用于驅動 50 W 傳輸線。該CDC2536還提供片上串聯阻尼電阻器,無需外部端接組件。

*附件:cdc2536.pdf

反饋 (FBIN) 輸入用于將輸出時鐘的頻率和相位與輸入時鐘 (CLKIN) 同步。六個輸出時鐘中的一個必須反饋給 FBIN,以便 PLL 保持 CLKIN 和輸出之間的同步。用作反饋引腳的輸出與 CLKIN 同步到相同的頻率。

Y 輸出可以配置為同相切換,頻率與 CLKIN 相同。選擇 (SEL) 輸入將三個 Y 輸出配置為以 CLKIN 頻率的二分之一或兩倍運行,具體取決于反饋到 FBIN 的引腳(見表 1 和表 2)。所有輸出信號占空比都調整為50%,與輸入時鐘的占空比無關。

輸出使能 (OE) 用于輸出控制。當OE為高電平時,輸出處于高阻抗狀態。當 OE 為低電平時,輸出處于活動狀態。TEST 用于設備的工廠測試,可用于繞過 PLL。TEST 應綁在 GND 上才能正常運行。

與許多包含PLL的產品不同,CDC2536不需要外部RC網絡。片內包含用于PLL的環路濾波器,可最大限度地減少元件數量、電路板空間和成本。

由于它基于PLL電路,因此CDC2536需要穩定時間才能實現反饋信號與參考信號的鎖相。在 CLKIN 上電和應用固定頻率、固定相位信號后,以及 PLL 基準或反饋信號發生任何變化后,需要此穩定時間。此類更改發生在更改 SEL 時,通過 TEST 啟用 PLL,以及通過 OE 啟用所有輸出時。

該CDC2536的特點是在0°C至70°C范圍內工作。

特性

- 低輸出偏斜,適用于時鐘分配和時鐘生成應用

- 工作電壓為 3.3V V

CC - 將一個時鐘輸入分配到六個輸出

- 一個選擇輸入將三個輸出配置為以輸入頻率的二分之一或兩倍工作

- 無需外部 RC 網絡

- 片內系列阻尼電阻器

- 外部反饋引腳 (FBIN) 用于將輸出同步到時鐘輸入

- 同步DRAM高速微處理器的應用

- TTL 兼容輸入和輸出

- 輸出驅動 50 條并聯端接傳輸線

- 先進的 EPIC-II**B ? BiCMOS 設計可顯著降低功耗

- 分布式V

CC接地引腳可降低開關噪聲 - 采用塑料 28 引腳收縮小外形封裝

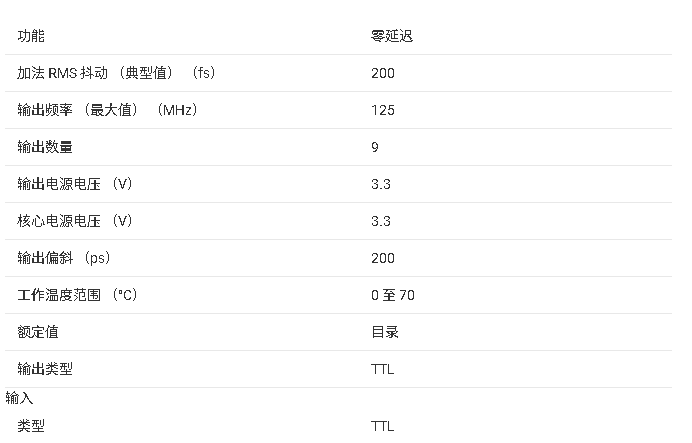

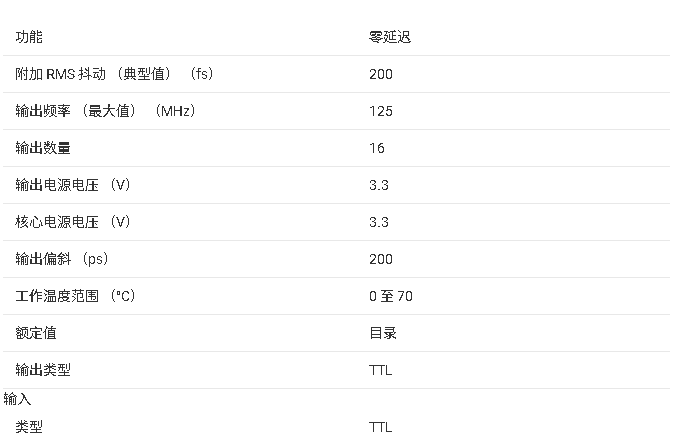

參數

?1. 產品概述?

CDC2536是德州儀器(TI)推出的 ?3.3V鎖相環(PLL)時鐘驅動器?,具有低偏移、低抖動特性,專為同步DRAM和高速微處理器設計。核心功能包括:

- ?信號分配?:1路輸入(CLKIN)驅動6路輸出(1Y1-1Y3, 2Y1-2Y3),支持 ?50Ω傳輸線驅動?。

- ?頻率配置?:通過 ?SEL引腳? 選擇輸出 ?1×、1/2×或2×輸入頻率?(詳見表1、表2)。

- ?鎖相環同步?:需將任意輸出反饋至 ?FBIN引腳? 以同步頻率和相位。

- ?輸出控制?:?OE引腳? 使能/禁用輸出(高阻態)。

- ?低功耗設計?:EPIC-IIB? BiCMOS工藝,集成阻尼電阻減少外部元件。

- ?封裝?:28引腳SSOP(DB),工作溫度 ?0°C至70°C?。

?2. 關鍵特性?

- ?頻率范圍?:

- ?配置A?(SEL=L):輸入50-100MHz,輸出1×或1/2×頻率。

- ?配置B?(SEL=H):輸入25-50MHz,輸出1×或2×頻率。

- ?低抖動?:RMS抖動≤200ps,輸出偏移(tsk(o))≤0.5ns。

- ?快速鎖定?:PLL穩定時間≤50μs(需固定頻率/相位輸入)。

- ?集成功能?:

- 片內環路濾波器,無需外部RC網絡。

- 50%占空比輸出(與輸入占空比無關)。

?3. 電氣參數?

| ?參數? | ?條件? | ?最小值? | ?典型值? | ?最大值? | ?單位? |

|---|---|---|---|---|---|

| ?**供電電壓(VCC)**? | - | 3.0 | 3.3 | 3.6 | V |

| ?**輸出驅動電流(IOH/IOL)**? | - | ±12 | - | - | mA |

| ?**輸入電容(Ci)**? | VI=3.3V/0V | - | 3 | - | pF |

| ?**功耗(ICC)**? | 無負載 | - | 6 | 9 | mA |

?4. 絕對最大額定值?

- ?電壓范圍?:輸入/輸出 ?**-0.5V至7V ?,VCC ? -0.5V至4.6V**?。

- ?功耗限制?:最大 ?0.68W?(55°C靜止空氣)。

- ?存儲溫度?:?**-65°C至150°C**?。

?5. 應用設計要點?

- ?反饋路徑?:必須將任一輸出連接至FBIN以實現PLL同步。

- ?布局建議?:

- 輸入信號過渡時間≤2.5ns,避免振鈴。

- 未使用的輸入引腳(如TEST、CLR)需接地。

- ?熱管理?:確保結溫≤150°C。

?總結?:CDC2536是一款高精度時鐘分配芯片,適用于需要低抖動、多頻率配置的同步系統,其集成PLL和靈活的輸出配置簡化了電路設計。

-

鎖相環

+關注

關注

36文章

635瀏覽量

91182 -

DRAM

+關注

關注

41文章

2396瀏覽量

189326 -

pll

+關注

關注

6文章

983瀏覽量

138251 -

輸出信號

+關注

關注

0文章

311瀏覽量

12797 -

時鐘驅動器

+關注

關注

0文章

122瀏覽量

14397

發布評論請先 登錄

CDC2536具有三態輸出的3.3鎖相LO0P時鐘驅動器數據表

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDC509 3.3V相位鎖定環時鐘驅動器技術文檔總結

?CDC2536 鎖相環時鐘驅動器技術文檔總結?

?CDC2536 鎖相環時鐘驅動器技術文檔總結?

評論