CDCE421A是一款高性能、低相位噪聲時鐘發生器。它有兩個完全集成、低噪聲、基于 LC 的壓控振蕩器 (VCO),可在 1.750 GHz 至 2.350 GHz 頻率范圍。它還具有集成晶體振蕩器,與外部AT切割晶體配合使用,以產生穩定的頻率 基于鎖相環 (PLL) 頻率合成器的參考。

輸出頻率(f 外 )與輸入晶體的頻率成正比(f XTAL的 ).預分頻器分頻器、反饋分頻器、輸出分頻器和VCO 選擇設置相對于 f 的輸出頻率 XTAL的 .

*附件:cdce421a.pdf

在CDCE421A中,反饋分頻器是相對于預分頻器設置自動設置的。如圖所示,預分頻器和反饋分頻器的乘積應在 60 到 64 之間,以保持穩定的控制回路。

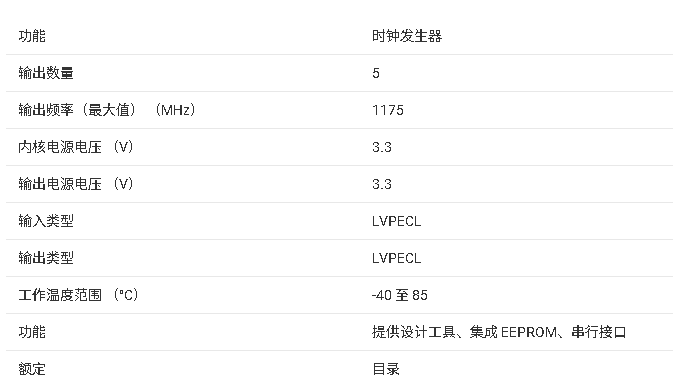

該CDCE421A支持一個差分LVDS時鐘輸出或一個差分LVPECL輸出。所有器件設置均可通過專有的簡單串行接口 (SSI) 進行編程。

該器件在 LVPECL 和 LVDS 輸出的 3.3V 電源環境中工作,工作溫度范圍為 -40°C 至 +85°C。 該CDCE421A采用QFN-24 4mm×4mm封裝。

特性

- 3.3 V單電源,用于LVPECL或LVDS工作

- 高性能時鐘乘法器,將晶體振蕩器電路與集成頻率合成器相結合

- 低輸出抖動:380 fs RMS(典型值)(10 kHz 至 20 MHz)

- 高頻低相位噪聲 (708MHz LVPECL):

- 載波的典型值為-109 kHz時為-109 dBc/Hz,10 MHz時為-146dBc/Hz

- 支持27.35 MHz至38.33 MHz的晶體或LVCMOS輸入頻率

- 輸出頻率范圍為 10.9 MHz 至 766.7 MHz 和 875.2 MHz 至 1175 MHz

- 低壓差分信號 (LVDS) 輸出,100

差分片外終端,10.9 MHz 至 400 MHz 頻率范圍

差分片外終端,10.9 MHz 至 400 MHz 頻率范圍 - 差分低壓正發射極耦合邏輯 (LVPECL) 輸出,頻率范圍為 10.9 MHz 至 1.175 GHz

- 兩個完全集成的壓控振蕩器 (VCO) 支持寬輸出頻率范圍

- 完全集成的可編程環路濾波器

- 3.3 V 時的典型功耗:

- LVDS 模式下為 274 mW

- LVPECL 模式下為 250 mW

- 芯片使能控制引腳

- 簡單的串行接口允許在制造后進行編程

- 集成片內非易失性存儲器 (EEPROM) 存儲設置,無需施加高壓

- 采用 4 mm × 4 mm QFN-24 封裝

- ESD 保護超過 2 kV (HBM)

- 工業溫度范圍:-40°C 至 +85°C

- 應用

- 低成本、高頻晶體振蕩器

參數

?1. 產品概述?

CDCE421A是德州儀器(TI)推出的高性能、低相位噪聲時鐘發生器芯片,主要特點包括:

- ?集成設計?:內置晶體振蕩器電路和頻率合成器,支持27.35 MHz至38.33 MHz的晶體或LVCMOS輸入頻率。

- ?低抖動性能?:典型RMS抖動為380 fs(10 kHz至20 MHz帶寬)。

- ?輸出類型?:支持LVDS(10.9 MHz至400 MHz)和LVPECL(10.9 MHz至1.175 GHz)兩種差分輸出。

- ?雙VCO架構?:集成兩個電壓控制振蕩器(VCO),覆蓋1.750 GHz至2.350 GHz頻率范圍。

- ?可編程性?:通過串行接口(SSI)配置分頻器、預分頻器等參數,并內置EEPROM存儲設置。

?2. 關鍵特性?

- ?電源?:單3.3 V供電,工業級溫度范圍(-40°C至+85°C)。

- ?功耗?:LVDS模式典型274 mW,LVPECL模式250 mW。

- ?封裝?:4 mm × 4 mm QFN-24封裝,ESD保護超過2 kV(HBM)。

?3. 應用場景?

?4. 功能模塊?

- ?晶體振蕩器?:提供基準頻率輸入。

- ?PLL合成器?:通過反饋分頻器(12/16/20/32)和輸出分頻器(1/2/4/8/16/32)生成目標頻率。

- ?控制接口?:單線串行編程接口(SDATA),支持實時配置和EEPROM存儲。

?5. 配置示例?

- ?頻率計算?:通過公式 fXTAL=輸出分頻×fOUT反饋分頻fXTAL ? =反饋分頻輸出分頻**×fOUT??** 確定所需晶體頻率。

- ?寄存器設置?:6個控制字(Word0-Word5)配置VCO選擇、分頻參數、電荷泵電流等。

?6. 電氣特性?

- ?LVDS輸出?:差分電壓247-454 mV,上升/下降時間≤230 ps。

- ?LVPECL輸出?:擺幅≥600 mV,相位噪聲典型值-146 dBc/Hz(10 MHz偏移)。

?7. 設計注意事項?

?8. 版本差異?

- 相比前代CDCE421,CDCE421A改進了啟動電路和LVDS緩沖器性能,需注意寄存器配置差異(如Word0 Bit10必須置1)。

?附錄?

- 提供測試配置圖(LVDS/LVPECL的AC/DC端接方案)及相位噪聲曲線(如708 MHz輸出時典型值-109 dBc/Hz @10 kHz)。

- 封裝選項包括卷帶(RGE)和小卷帶(ARGET)形式,符合RoHS標準。

該文檔完整覆蓋了芯片功能、配置方法、電氣規格及應用設計指南,適用于硬件工程師進行時鐘系統設計參考。

-

鎖相環

+關注

關注

36文章

635瀏覽量

91177 -

合成器

+關注

關注

0文章

316瀏覽量

27930 -

pll

+關注

關注

6文章

983瀏覽量

138242 -

時鐘發生器

+關注

關注

1文章

307瀏覽量

70100 -

晶體振蕩器

+關注

關注

9文章

749瀏覽量

33301

發布評論請先 登錄

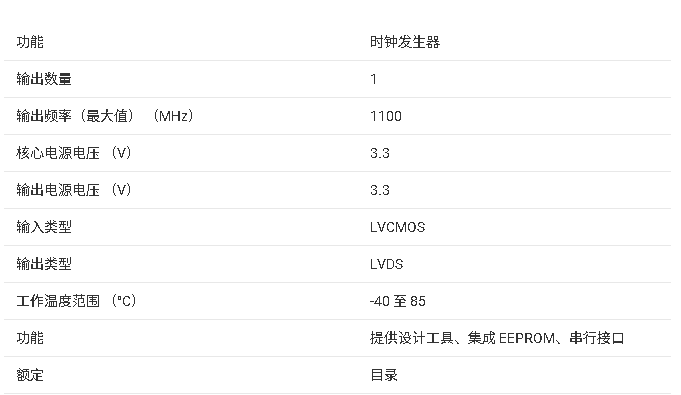

CDCE421A全集成、寬范圍、低抖動晶體振蕩器時鐘發生器數據表

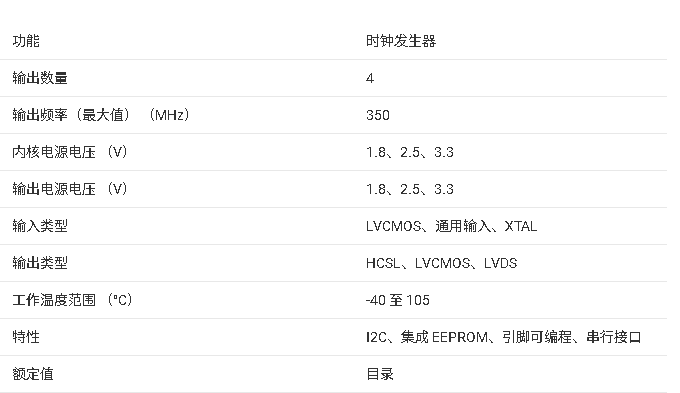

?CDCE6214 超低功耗時鐘發生器技術文檔總結

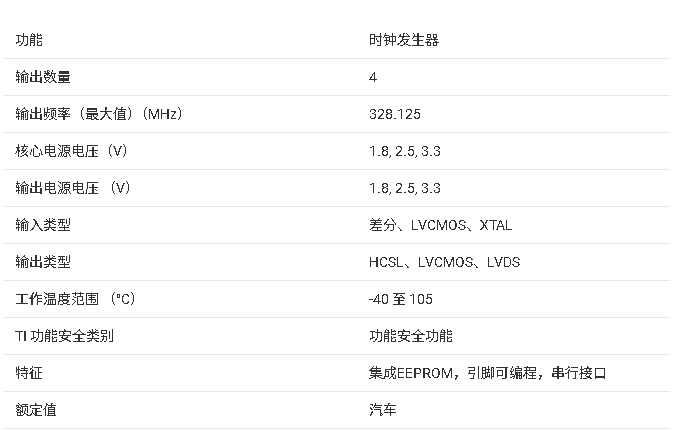

?CDCE6214-Q1 超低功耗時鐘發生器技術文檔總結

?CDCE62002 四輸出時鐘發生器/抖動清除器技術文檔總結

?CDCE62005 時鐘發生器芯片技術文檔總結

?CDCE421A 時鐘發生器芯片技術文檔總結

?CDCE421A 時鐘發生器芯片技術文檔總結

評論