該CDCUA877是一款高性能、低抖動、低偏斜、零延遲緩沖器,可將差分時鐘輸入對(CK、CK)分配給十個差分時鐘輸出對(Yn、Yn)和一個差分反饋時鐘輸出對(FBOUT、FBOUT)。時鐘輸出由輸入時鐘(CK、CK)、反饋時鐘(FBIN、FBIN)、LVCMOS控制引腳(OE、OS)和模擬電源輸入(AV DD ).當OE為低電平時,除FBOUT/FBOUT外,時鐘輸出被禁用,而內部PLL繼續保持其鎖定頻率。OS(輸出選擇)是必須連接到 GND 或 V 的程序引腳 DD .當作系統為高電平時,OE 功能如前所述。當OS和OE都較低時,OE對Y7/Y7沒有影響,它們是自由運行的。當 AVDD接地時,PLL 被關閉并旁路用于測試目的。

*附件:cdcua877.pdf

當兩個時鐘輸入(CK、CK)邏輯低電平時,器件進入低功耗模式。差分輸入上的輸入邏輯檢測電路獨立于輸入緩沖器,檢測邏輯低電平,并在所有輸出、反饋和PLL關閉的低功耗狀態下運行。當時鐘輸入從邏輯低電平轉換為差分信號時,PLL重新導通,輸入和輸出使能,PLL在規定的穩定時間內獲得反饋時鐘對(FBIN、FBIN)和時鐘輸入對(CK、CK)之間的鎖相。

該CDCUA877能夠跟蹤擴頻時鐘 (SSC) 以降低 EMI。該器件的工作溫度范圍為 -40°C 至 85°C)。

特性

- 1.8V/1.9V鎖相環時鐘驅動器,適用于雙倍數據速率(DDR II)應用

- 兼容擴頻時鐘

- 工作頻率:125 MHz 至 410 MHz

- 應用頻率:160 MHz 至 410 MHz

- 低電流消耗:<200 mA(典型值)

- 低抖動(周期間):±40 ps

- 低輸出偏斜:35 ps

- 穩定時間 <6 μs

- 將一個差分時鐘輸入分配給十個差分輸出

- 52 焊球 μBGA(MicroStar Junior? BGA,0.65 mm 間距)

- 外部反饋引腳(FBIN、FBIN)用于將輸出同步到輸入時鐘

- 符合或超過PC2-3200/4300/5300/6400o的CUA877/CAU878規范PLL標準

- 故障安全輸入

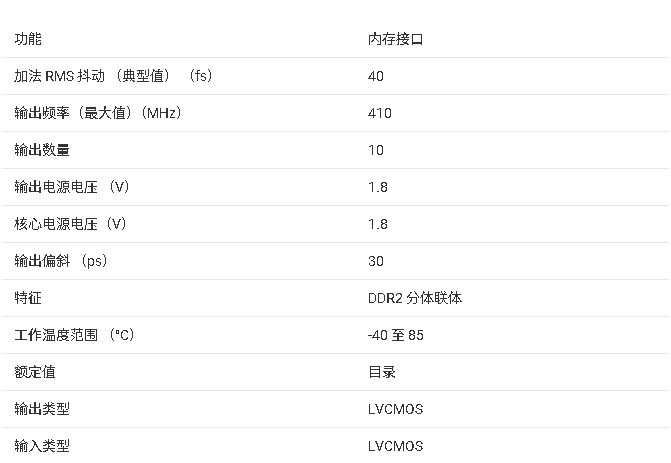

參數

?1. 核心功能?

- 專為DDR II應用設計的高性能時鐘緩沖器,支持1.8V/1.9V工作電壓

- 將1對差分時鐘輸入(CK/CK)分配至10對差分時鐘輸出(Yn/Yn)及1對反饋輸出(FBOUT/FBOUT)

- 兼容展頻時鐘(SSC),支持125MHz至410MHz操作頻率(應用頻率160MHz-410MHz)

?2. 關鍵特性?

- ?低功耗?:靜態電流<200mA,支持邏輯低電平自動進入省電模式

- ?高精度時序?:

- 周期抖動±40ps(cycle-cycle)

- 輸出偏移35ps

- 鎖相環穩定時間<6μs

- ?控制功能?:

- 異步輸出使能(OE)

- 輸出選擇引腳(OS)可配置Y7/Y7自由運行模式

- 外部反饋引腳(FBIN/FBIN)同步輸出與輸入時鐘

?3. 封裝與規格?

- 52球μBGA封裝(0.65mm間距,型號CDCUA877ZQL)

- 工作溫度范圍:-40°C至85°C

- 符合PC2-3200/4300/5300/6400標準

?4. 電氣特性?

- 輸入電壓范圍:-0.5V至VDDQ+0.5V

- 差分輸入電壓(VID):0.3V至VDDQ+0.4V

- 輸出驅動能力:±9mA(高/低電平)

?5. 應用設計要點?

- 推薦AVDD電源濾波方案(2200pF電容+磁珠)

- 需匹配輸入/反饋時鐘的壓擺率(建議2.5V/ns)

- 測試模式下可通過接地AVDD旁路PLL

-

驅動器

+關注

關注

54文章

9082瀏覽量

155475 -

緩沖器

+關注

關注

6文章

2227瀏覽量

48877 -

時鐘輸出

+關注

關注

0文章

11瀏覽量

5832 -

鎖相環時鐘

+關注

關注

0文章

2瀏覽量

1265

發布評論請先 登錄

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCUA877 1.8V鎖相環時鐘驅動器技術文檔總結

?CDCUA877 1.8V鎖相環時鐘驅動器技術文檔總結

評論