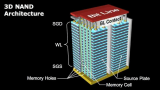

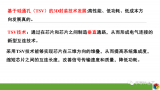

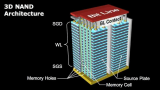

這項新技術允許使用超過60,000個TSV孔堆疊12個DRAM芯片,同時保持與當前8層芯片相同的厚度。 全球先進半導體技術的領導者三星電子今天宣布,它已開發出業界首個12層3D-TSV(直通硅通孔

2019-10-08 16:32:23 6863

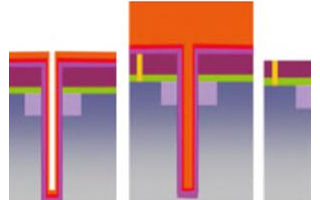

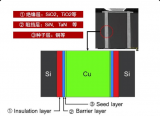

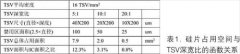

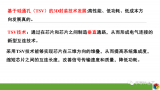

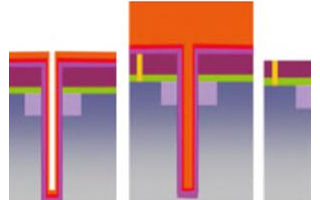

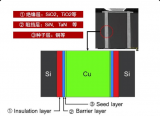

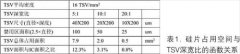

6863 本文報道了硅通孔三維互連技術的核心工藝以及基于TSV形成的眾多先進封裝集成技術。形成TSV主要有Via-First、Via-Middle、Via-Last 3大技術路線。TSV 硅刻蝕、TSV 側壁

2024-11-01 11:08:07 5236

5236

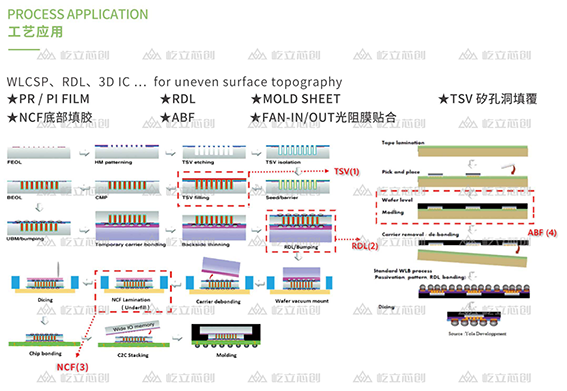

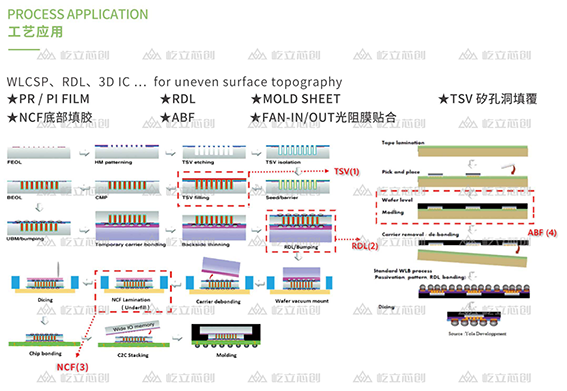

2.5D/3D封裝技術作為當前前沿的先進封裝工藝,實現方案豐富多樣,會根據不同應用需求和技術發展動態調整,涵蓋芯片減薄、芯片鍵合、引線鍵合、倒裝鍵合、TSV、塑封、基板、引線框架、載帶、晶圓級薄膜

2025-08-05 15:03:08 2815

2815

本文主要講述TSV工藝中的硅晶圓減薄與銅平坦化。 硅晶圓減薄與銅平坦化作為 TSV 三維集成技術的核心環節,主要應用于含銅 TSV 互連的減薄芯片制造流程,為該技術實現短互連長度、小尺寸、高集成度等特性提供了重要支撐。

2025-08-12 10:35:00 1545

1545

在“NEPCON日本2013”的技術研討會上,英特爾和高通分別就有望在新一代移動SoC(系統級芯片)領域實現實用的 TSV(硅通孔)三維封裝技術發表了演講。兩家公司均認為,“三維封裝是將來的技術方向”。

2013-01-22 09:06:01 1822

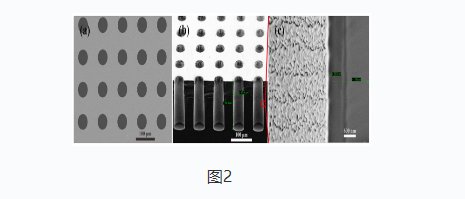

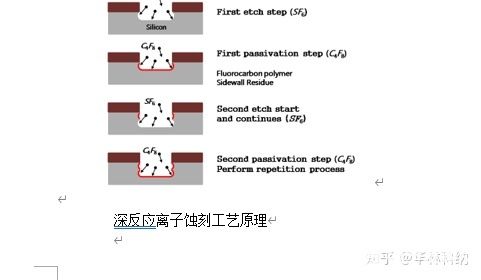

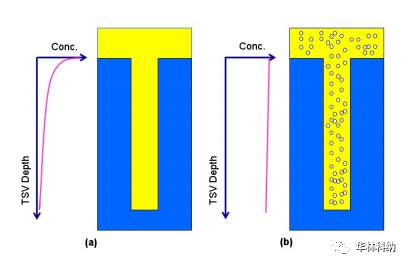

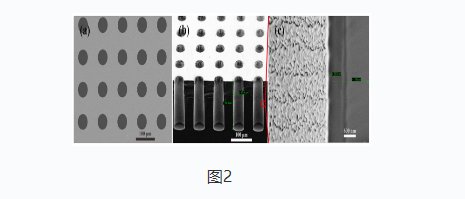

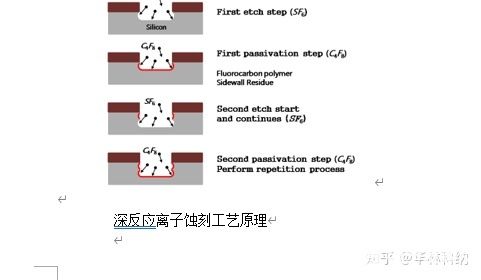

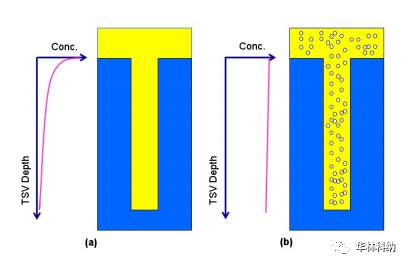

1822 本文介紹了一種新型的高縱橫比TSV電鍍添加劑系統,利用深層反應離子蝕刻(DRIE)技術對晶片形成圖案,并利用物理氣相沉積(PVD)技術沉積種子層。通過陽極位置優化、多步驟TSV填充過程、添加劑濃度

2021-12-27 16:00:41 3170

3170

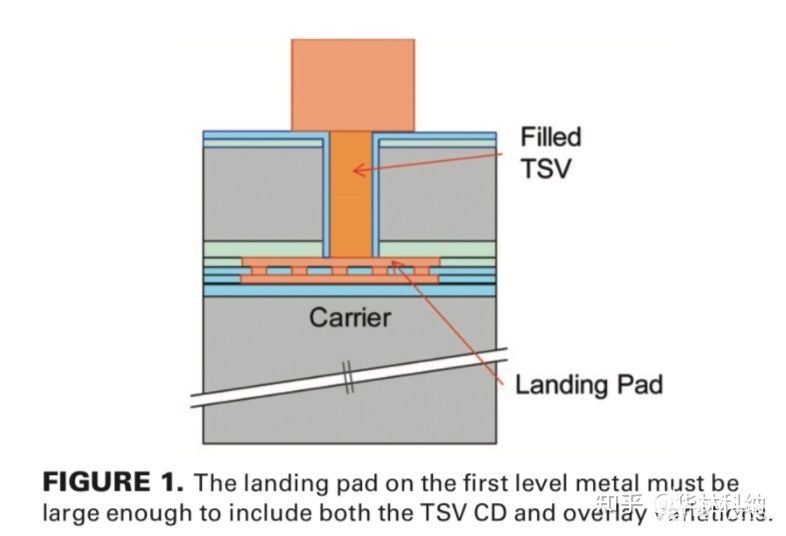

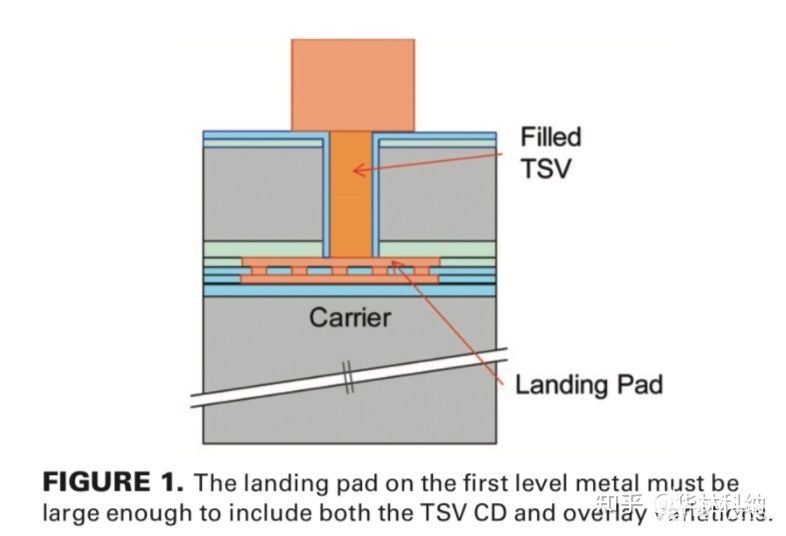

引言 隨著對多功能移動消費電子設備需求的增加,半導體芯片互連密度的復雜性不斷增加。傳統的芯片到封裝集成(CPI)使用引線鍵合將鍵合焊盤互連到封裝引線。隨著芯片規模向原子級發展,采用硅通孔(TSV

2022-06-15 17:22:22 5508

5508

華林科納對包括背照式圖像傳感器、中介層和 3D 存儲器在內的消費產品相關設備的需求正在推動使用硅通孔 (TSV) [1] 的先進封裝。 TSV 處理的各種工藝流程(先通孔、中間通孔和最后通孔

2022-07-19 14:51:42 1227

1227

1. BGA和CSP封裝技術詳解 2.?干貨分享丨BGA開路金相切片分析 (BGA Open Cross-Section) ? ? ? 審核編輯:彭靜

2022-07-26 14:43:18 7462

7462 在集成電路的制造階段延續摩爾定律變得越發困難,而在封裝階段利用三維空間可以視作 對摩爾定律的拓展。硅通孔是利用三維空間實現先進封裝的常用技術手段,現有技術中對于應用于 CMOS 圖像傳感器件封裝

2023-04-12 14:35:41 2896

2896 硅通孔(TSV) 是當前技術先進性最高的封裝互連技術之一。基于 TSV 封裝的核心工藝包括 TSV 制造、RDL/微凸點加工、襯底減薄、圓片鍵合與薄圓片拿持等。

2023-05-08 10:35:24 5731

5731

主要的技術路徑。2.5D/3D封裝正在加速3D互連密度的技術突破,TSV及TGV的技術作為2.5D/3D封裝的核心技術,越來越受到重視。

2023-05-23 12:29:11 5750

5750

來源:半導體風向標 從HBM存儲器到3D NAND芯片,再到CoWoS,硬件市場上有許多芯片是用英文稱為TSV構建的,TSV是首字母縮寫,意為“通過硅通孔”并翻譯為via硅的事實,它們垂直地穿過

2023-07-26 10:06:15 2219

2219 )、凸塊制作(Bumping)及硅通孔(TSV)等工藝技術,涉及與晶圓制造相似的光刻、顯影、刻蝕、剝離等工序步驟。

2023-08-07 10:59:46 3328

3328

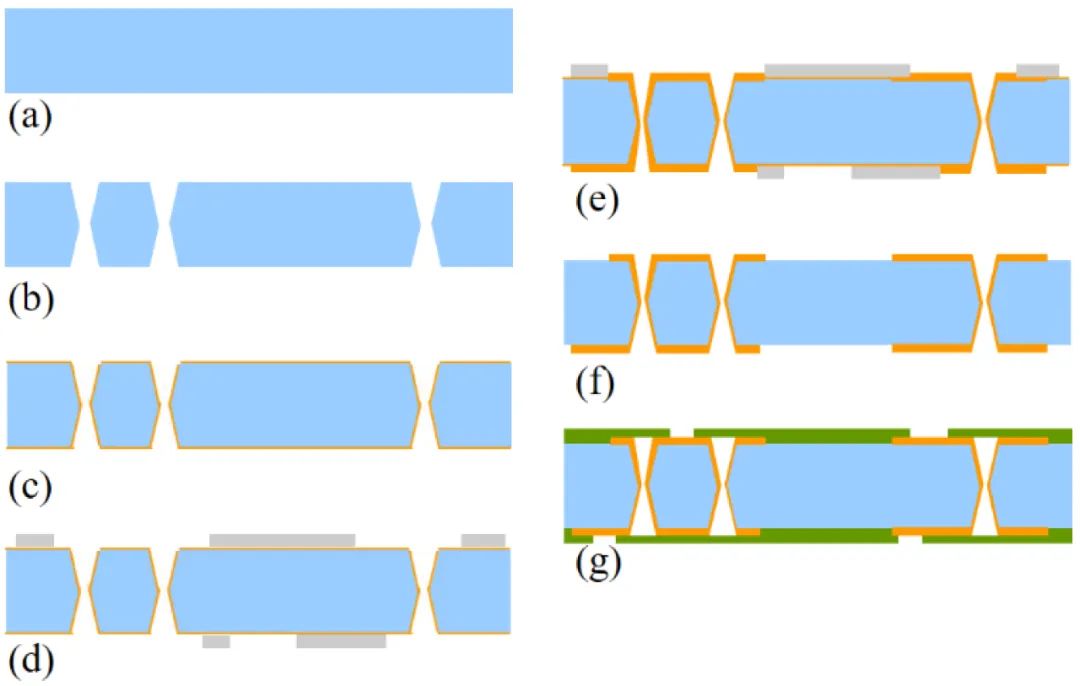

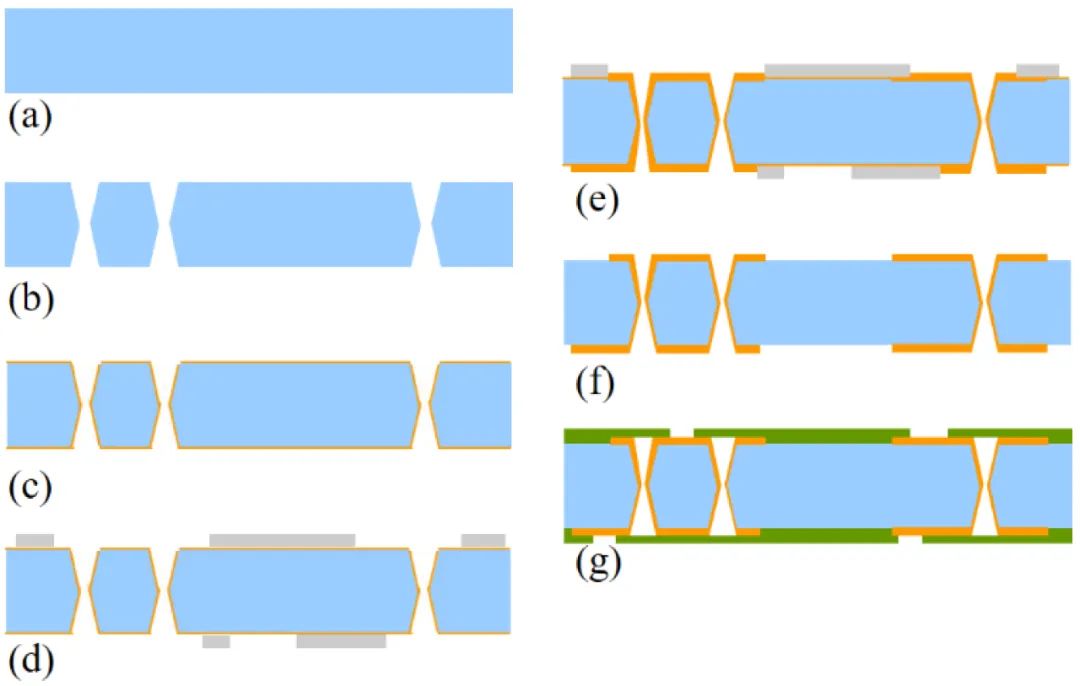

在上篇文章中介紹了扇入型晶圓級芯片封裝(Fan-In WLCSP)、扇出型晶圓級芯片封裝(Fan-Out WLCSP)、重新分配層(RDL)封裝、倒片(Flip Chip)封裝,這篇文章著重介紹硅通孔(TSV)封裝工藝。

2023-11-08 10:05:53 7069

7069

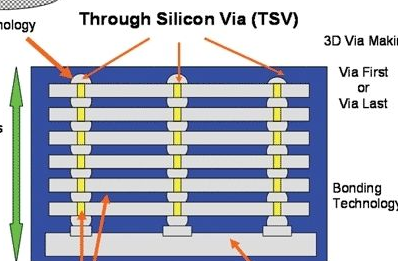

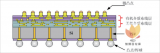

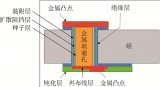

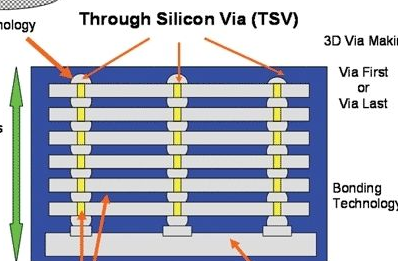

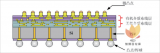

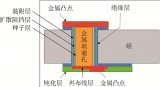

硅通孔技術(TSV,Through Silicon Via)是通過在芯片和芯片之間、晶圓和晶圓之間制作垂直導通,實現芯片之間互連的技術,是2.5D/3D 封裝的關鍵工藝之一。通過垂直互連減小互連長度、信號延遲,降低電容、電感,實現芯片間低功耗、高速通訊,增加帶寬和實現小型化。

2024-01-09 09:44:13 23017

23017

以硅通孔(TSV)為核心的 2.5D/3D 封裝技術可以實現芯片之間的高速、低功耗和高帶寬的信號傳輸。

2024-02-25 16:51:10 2811

2811

匹配), 多芯片模塊封裝 (MCM, 可集成異質芯片), 晶圓級封裝 (WLP,包括扇出型晶圓級封裝(FOWLP)、 微型表面貼裝元器件 (microSMD)等),三維封裝(微凸塊互連封裝、TSV 互連封裝等),系統封裝(SIP), 芯片系統 (

2024-10-14 13:31:24 4817

4817

3D-IC通過采用TSV(Through-Silicon Via,硅通孔)技術,實現了不同層芯片之間的垂直互連。這種設計顯著提升了系統集成度,同時有效地縮短了互連線的長度。這樣的改進不僅降低了信號傳輸的延時,還減少了功耗,從而全面提升了系統的整體性能。

2025-02-21 15:57:02 2460

2460

本文主要講述什么是系統級封裝技術。 從封裝內部的互連方式來看,主要包含引線鍵合、倒裝、硅通孔(TSV)、引線框架外引腳堆疊互連、封裝基板與上層封裝的凸點互連,以及扇出型封裝和埋入式封裝中的重布線等

2025-08-05 15:09:04 2135

2135

。然而,當系統級集成需求把 3D 封裝/3D IC 技術推向 WLCSP 時,傳統方案——引線鍵合堆疊、PoP、TSV 硅通孔——因工藝窗口、CTE 失配及成本敏感性而顯著受限。

2025-08-28 13:46:34 2894

2894

硅通孔(Through Silicon Via,TSV)技術是一種通過在硅介質層中制作垂直導通孔并填充導電材料來實現芯片間垂直互連的先進封裝技術。

2025-10-13 10:41:46 3147

3147

具有代表性的技術包括晶圓級封裝(WLP)及采用TSV(硅通孔)的硅轉接板等,潛藏著新的商機。

2011-08-28 12:17:46 4724

4724

,支持現代服務器不斷增長的需求。 三星DDR5芯片采用新型的硅通孔(TSV) 8 層技術,與DDR4相比,該技術使得DDR5的單個芯片能夠包含兩倍的堆棧數量。每個雙列直插式存儲模塊(DIMM)還提供高達512GB的存儲空間。其數據傳輸速度高達4800 MT/s,專門用于

2020-02-16 07:34:00 1980

1980 電子發燒友網報道(文/黃山明)TSV(Through Silicon Via)即硅通孔技術,是通過在芯片和芯片之間、晶圓和晶圓之間制作垂直導通,實現芯片之間互連的技術,是2.5D/3D封裝的關鍵

2025-04-14 01:15:00 2555

2555 硅通孔(TSV)技術借助硅晶圓內部的垂直金屬通孔,達成芯片間的直接電互連。相較于傳統引線鍵合等互連方案,TSV 技術的核心優勢在于顯著縮短互連路徑(較引線鍵合縮短 60%~90%)與提升互連密度

2025-10-14 08:30:00 6446

6446

實現利用硅光電路和微光學元件的創新解決方案,同時可實現控制電子元件和系統封裝的最優集成。MACOM始終關注采用細線光刻來實現高密度功能的硅微光子綜合技術。這些技術將高性能低功率光學器件與最佳功能及最大封裝

2017-11-02 10:25:07

硅通孔(TSV)電鍍的高可靠性是高密度集成電路封裝應用中的一個有吸引力的熱點。本文介紹了通過優化濺射和電鍍條件對完全填充TSV的改進。特別注意具有不同種子層結構的樣品。這些樣品是通過不同的濺射和處理

2021-01-09 10:19:52

其導通角,就可以改變其輸出電壓有效值,從而實現調光功能。除了可控硅以外,還有晶體管前沿、后沿調光技術等,基本原理都差不多。2、可控硅調光的缺點和問題 在用可控硅調光時,還是會存在如下的一系列問題

2016-12-16 18:42:52

詳解面向TDD系統手機的SAW濾波器的技術動向

2021-05-10 06:18:34

DIP封裝(Dual In-line Package),也叫雙列直插式封裝技術,指采用雙列直插形式封裝的集成電路芯片,絕大多數中小規模集成電路均采用這種封裝形式,其引腳數一般不超過100。DIP封裝

2018-08-23 09:33:08

所謂“CPU封裝技術”是一種將集成電路用絕緣的塑料或陶瓷材料打包的技術。以CPU為例,我們實際看到的體積和外觀并不是真正的CPU內核的大小和面貌,而是CPU內核等元件經過封裝后的產品

2018-08-29 10:20:46

誰來闡述一下cof封裝技術是什么?

2019-12-25 15:24:48

,我們將采用穿硅通孔(TSV)用于晶圓級堆疊器件的互連。該技術基本工藝為高密度鎢填充穿硅通孔,通孔尺寸從1μm到3μm。用金屬有機化學汽相淀積(MOCVD)淀積一層TiN薄膜作為籽晶層,隨后同樣也采用

2011-12-02 11:55:33

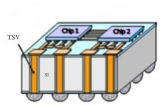

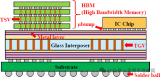

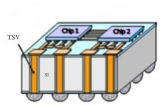

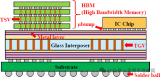

是2.5D封裝,將光芯片和電芯片都和一個中介板相連(通過TSV和bump),中介板可以實現芯片間高速互聯,這個中介板稱為interposer。【TSV是硅通孔,可以實現硅芯片內部的互聯;bump是金屬

2023-03-29 10:48:47

;?引腳數。引腳數越多,越高級,但是工藝難度也相應增加;其中,CSP由于采用了FlipChip技術和裸片封裝,達到了 芯片面積/封裝面積=1:1,為目前最高級的技術;芯片封裝測試流程詳解ppt[hide]暫時不能上傳附件 等下補上[/hide]

2012-01-13 11:46:32

芯片堆疊技術在SiP中應用的非常普遍,通過芯片堆疊可以有效降低SiP基板的面積,縮小封裝體積。 芯片堆疊的主要形式有四種: 金字塔型堆疊 懸臂型堆疊 并排型堆疊 硅通孔TSV型堆疊

2020-11-27 16:39:05

研究院(先進電子封裝材料廣東省創新團隊)、上海張江創新學院、深圳集成電路設計產業化基地管理中心、桂林電子科技大學機電工程學院承辦的 “第二期集成電路封裝技術 (IC Packaging

2016-03-21 10:39:20

集成電路芯片封裝技術知識詳解本電子書對封裝介紹的非常詳細,所以和大家分享。因為太大,沒有上傳。請點擊下載。[此貼子已經被作者于2008-5-12 22:45:41編輯過]

2008-05-12 22:44:28

集成電路封裝技術詳解包括了概述,陶瓷封裝,塑料封裝,金屬封裝,其它封裝等。

2008-05-12 22:41:56 705

705 硅通孔互連技術的開發與應用封國強 蔡堅 王水弟(清華大學微電子學研究所,北京,100084,中國)摘要:隨著三維疊層封裝、MEMS 封裝、垂直集成傳感器陣列以及臺面MOS 功

2009-12-14 11:35:44 9

9 被稱之為“堆疊硅片互聯技術”的3D封裝方法采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術,實現了多芯

2010-10-29 17:54:25 1168

1168 3D-IC設計者希望制作出高深寬比(HAR>10:1)硅通孔(TSV),從而設計出更小尺寸的通孔,以減小TSV通孔群在硅片上的占用空間,最終改進信號的完整性。事實上,當前傳統的TSV生產供應鏈已落后于ITRS對其的預測。

2011-01-14 16:10:40 2333

2333

高通(Qualcomm)先進工程部資深總監Matt Nowak日前指出,在使用高密度的硅穿孔(TSV)來實現芯片堆疊的量產以前,這項技術還必須再降低成本才能走入市場。他同時指出,業界對該技術價格和

2011-10-14 09:16:36 2748

2748 意法半導體率先將硅通孔技術(TSV)引入MEMS芯片量產。在意法半導體的多片MEMS產品(如智能傳感器、多軸慣性模塊)內,硅通孔技術以垂直短線方式取代傳統的芯片互連線方法,在尺寸更小

2011-10-19 09:15:31 1113

1113 重點討論了垂直互連的硅通孔(TSV)互連工藝的關鍵技術及其加工設備面臨的挑戰.提出了工藝和設備開發商的應對措施并探討了3DTSV封裝技術的應用前景。

2011-12-07 10:59:23 89

89 對3D封裝技術結構特點、主流多層基板技術分類及其常見鍵合技術的發展作了論述,對過去幾年國際上硅通孔( TSV)技術發展動態給與了重點的關注。尤其就硅通孔關鍵工藝技術如硅片減薄

2011-12-07 11:00:52 153

153 2011年,半導體封裝業界的熱門話題是采用TSV(硅通孔)的三維封裝技術。雖然TSV技術此前已在CMOS圖像傳感器等產品上實用化,但始終未在存儲器及邏輯LSI等用途中普及。最近,存儲器及邏

2011-12-23 09:34:58 5386

5386 中微半導體設備有限公司(以下簡稱“中微”)推出了8英寸硅通孔(TSV)刻蝕設備Primo TSV200E?

2012-03-15 09:39:40 1776

1776 在日本,硅通孔(TSV:Through Silicon Via)技術從10多年前開始就備受業界關注。比如,日本超尖端電子技術開發機構(ASET)從1999年度起就在通過名為“超高密度電子SI”的研究項目推

2012-04-18 09:43:11 1757

1757 Invensas Corporation 為半導體技術解決方案的領先供應商,同時也是 Tessera Technologies的全資子公司,今日推出了焊孔陣列 (BVA) 技術。BVA 是替代寬幅輸入/輸出硅通孔 (TSV) 的超高速輸入

2012-05-25 14:54:59 1184

1184 硅通孔TSV發生開路故障和泄漏故障會降低三維集成電路的可靠性和良率,因此對綁定前的TSV測試尤為重要。現有CAFWAS測試方法對泄漏故障的測試優于其他方法(環形振蕩器等),缺點是該方法不能測試

2017-11-22 10:56:29 17

17 要實現三維集成,需要用到幾個關鍵技術,如硅通孔(TSV),晶圓減薄處理,以及晶圓/芯片鍵合。TSV 互連具有縮短路徑和更薄的封裝尺寸等優點,被認為是三維集成的核心技術。

2017-11-24 16:23:48 66425

66425

硅通孔技術(Through Silicon Via, TSV)技術是一項高密度封裝技術,正在逐漸取代目前工藝比較成熟的引線鍵合技術,被認為是第四代封裝技術。TSV技術通過銅、鎢、多晶硅等導電物質

2018-08-14 15:39:10 92829

92829 被稱之為“堆疊硅片互聯技術”的3D封裝方法采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術,實現了多芯片可編程平臺。

2019-01-03 13:20:59 3796

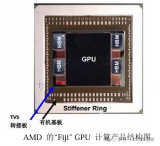

3796 從英特爾所揭露的技術資料可看出,Foveros本身就是一種3D IC技術,透過硅穿孔(Through-Silicon Via, TSV)技術與微凸塊(micro-bumps)搭配,把不同的邏輯芯片堆疊起來。

2019-08-14 11:18:42 4607

4607

從低密度的后通孔TSV 硅3D集成技術,到高密度的引線混合鍵合或3D VSLI CoolCubeTM解決方案,研究人員發現許多開發新產品的機會。本文概述了當前新興的硅3D集成技術,討論了圖像傳感器

2020-01-16 09:53:00 1550

1550 直到最近,如果你希望將異構die放在單個封裝上以實現最佳性能,則可以將這些die放置在一塊稱為中介層的硅片上,并通過中介層進行布線以進行通信。硅通孔(TSV)(電連接)穿過中介層并進入基板,該基板形成了封裝的底部。

2020-09-17 16:22:38 2420

2420 直通硅通孔(TSV)器件是3D芯片封裝的關鍵推動者,可提高封裝密度和器件性能。要實現3DIC對下一代器件的優勢,TSV縮放至關重要。

2022-04-12 15:32:46 1788

1788

硅通孔(Through Silicon Via,TSV)技術是一項高密度封裝技術,它正在逐漸取代目前工藝比較成熟的引線鍵合技術,被認為是第四代封裝技術。在2.5D/3D IC中TSV被大規模應用于

2022-05-31 15:24:39 3876

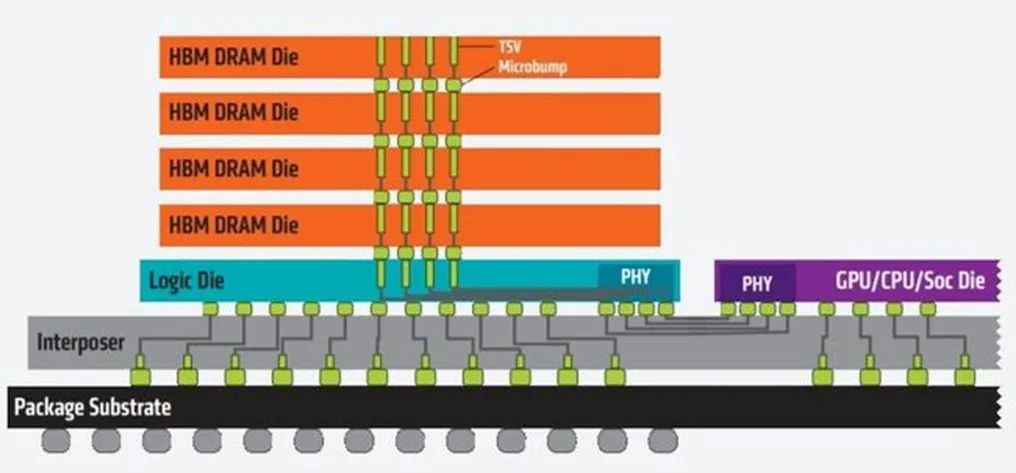

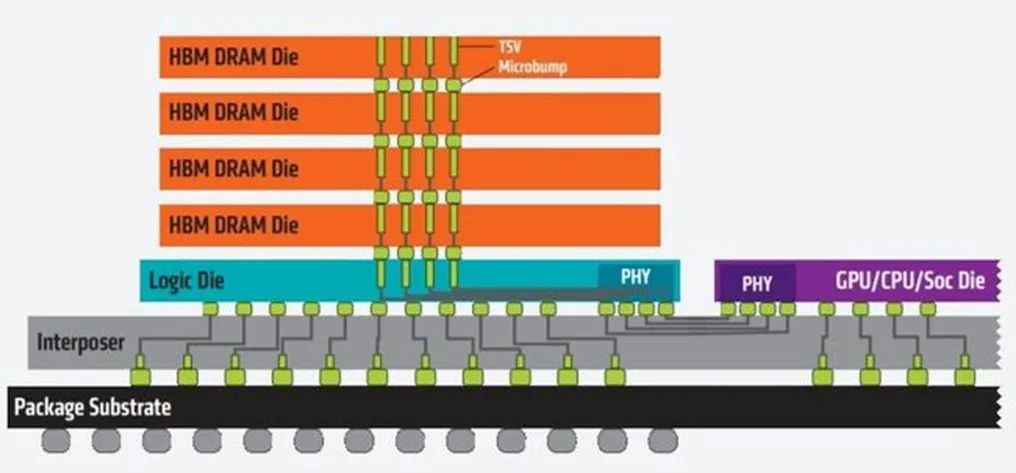

3876 ;通過硅通道(TSV)提供與封裝凸點的連接。硅插入器技術提供了改進的互連密度,這對高信號計數HBM接口至關重要。最近,臺積電提供了一種有機干擾器(CoWos-R),在互連密度和成本之間進行權衡。

2022-07-05 11:37:03 4023

4023 2.5D封裝是傳統2D IC封裝技術的進展,可實現更精細的線路與空間利用。在2.5D封裝中,裸晶堆棧或并排放置在具有硅通孔(TSV)的中介層(interposer)頂部。其底座,即中介層,可提供芯片之間的連接性。

2022-11-14 10:14:53 2151

2151 一文詳解精密封裝技術

2022-12-30 15:41:12 2358

2358 硅通孔(Through Si Vias,TSV)硅轉接基板技術作為先進封裝的一種工藝方式,是實現千級IO芯片高密度組裝的有效途徑,近年來在系統集成領域得到快速應用。

2023-06-16 16:11:33 1614

1614

本文要點:3D集成電路需要一種方法來連接封裝中垂直堆疊的多個裸片由此,與制造工藝相匹配的硅通孔(Through-SiliconVias,TSV)設計應運而生硅通孔設計有助于實現更先進的封裝能力,可以

2022-11-17 17:58:04 2260

2260

隨著晶體管尺寸不斷向原子尺度靠近,摩爾定律正在放緩,面對工藝技術持續微縮所增加的成本及復雜性,市場亟需另辟蹊徑以實現低成本前提下的芯片高性能,以TSV(Through Silicon Via,硅通孔)技術為代表的先進封裝成為芯片集成的重要途徑。

2023-06-30 16:39:34 2413

2413

編者注:TSV是通過在芯片與芯片之間、晶圓和晶圓之間制作垂直導通;TSV技術通過銅、鎢、多晶硅等導電物質的填充,實現硅通孔的垂直電氣互聯,這項技術是目前唯一的垂直電互連技術,是實現3D先進封裝的關鍵技術之一。

2023-07-03 09:45:34 5432

5432

TSV不僅賦予了芯片縱向維度的集成能力,而且它具有最短的電傳輸路徑以及優異的抗干擾性能。隨著摩爾定律慢慢走到盡頭,半導體器件的微型化也越來越依賴于集成TSV的先進封裝。

2023-07-25 10:09:36 1496

1496

硅通孔(TSV)有望成為電子器件三維芯片堆疊技術的未來。TSV互連的結構是通過首先在晶片表面蝕刻深過孔,然后用所需金屬填充這些過孔來形成的。目前,銅基TSV是最具成本效益的大規模生產TSV。一旦過孔

2023-08-30 17:19:11 1234

1234

先進封裝中硅通孔(TSV)銅互連電鍍研究進展

2023-09-06 11:16:42 2280

2280

主要以實現多層的高密度互連,高精 細化則關注在精細的線和微小的孔,之前提升的方 向以線路能力提升為主,隨著線路能力提升的速度減緩以及生產成本激增,發展的方向將逐步轉化為 孔的提升,因此,封裝基板微盲孔

2023-09-15 10:37:33 3627

3627

BGA和CSP封裝技術詳解

2023-09-20 09:20:14 4693

4693

先進封裝技術以SiP、WLP、2.5D/3D為三大發展重點。先進封裝核心技術包括Bumping凸點、RDL重布線、硅中介層和TSV通孔等,依托這些技術的組合各廠商發展出了滿足多樣化需求的封裝解決方案,SiP系統級封裝、WLP晶圓級封裝、2.5D/3D封裝為三大發展重點。

2023-09-28 15:29:37 4970

4970

半導體產品在由二維向三維發展,從技術發展方向半導體產品出現了系統級封裝(SiP)等新的封裝方式,從技術實現方法出現了倒裝(FlipChip),凸塊(Bumping),晶圓級封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進封裝技術。

2023-10-31 09:16:29 3859

3859

瓜分全部的市場份額,在新應用催化下,也為后端封測廠和TSV設備公司帶來了市場機會。 硅通孔 /? TSV(Through-Silicon Via) 硅通孔TSV是一種能讓3D封裝遵循摩爾定律演進的互連

2023-11-09 13:41:21 7320

7320

TSV 指 Through Silicon Via,硅通孔技術,是通過硅通道垂直穿過組成堆棧的不同芯片或不同層實現不同功能芯片集成的先進封裝技術。TSV 主要通過銅等導電物質的填充完成硅通孔的垂直

2023-11-19 16:11:06 4110

4110

硅通孔(TVS)技術相關知識

2023-11-20 11:15:46 1562

1562

3D-IC 中 硅通孔TSV 的設計與制造

2023-11-30 15:27:28 2237

2237

共讀好書 魏紅軍 段晉勝 (中國電子科技集團公司第二研究所) 摘要: 論述了 TSV 技術發展面臨的設備問題,并重點介紹了深硅刻蝕、 CVD/PVD 沉積、電鍍銅填充、晶圓減薄、晶圓鍵合等幾種制約

2024-03-12 08:43:59 2370

2370

隨著半導體技術的飛速發展,傳統的二維平面集成方式已經逐漸接近其物理極限。為了滿足日益增長的性能需求,同時克服二維集成的瓶頸,三維集成技術應運而生。其中,穿透硅通孔(Through-Silicon

2024-04-03 09:42:34 6386

6386

TSV(Through-Silicon Via)是一種先進的三維集成電路封裝技術。它通過在芯片上穿孔并填充導電材料,實現芯片內、芯片間以及芯片與封裝之間的垂直連接。

2024-04-11 16:36:36 9819

9819

Via, TSV )成為了半導體封裝核心技術之一,解決芯片垂直方向上的電氣和物理互連,減小器件集成尺寸,實現封裝小型化。本文介紹了硅通孔技術的可靠性,包括熱應力可靠性和工藝技術可靠性兩方面。過大熱應力可能會導致通孔側壁粗糙,并影響內部載流子遷移率,從而使器

2024-04-12 08:47:43 909

909 上圖是TSV工藝的一般流程。TSV,全名Through-Silicon Via,又叫硅通孔工藝。

2024-04-17 09:37:56 4129

4129

TGV(Through-Glass Via),玻璃通孔,即是一種在玻璃基板上制造貫穿通孔的技術,與硅通孔(TSV)都是先進封裝中不可或缺的。

2024-10-18 15:06:51 2780

2780

摘要:在最近的半導體封裝中,采用硅通孔 (TSV) 技術已成為集成 2.5 和 3D Si芯片以及中介層的關鍵。TSV 具有顯著的優勢,包括高互連密度、縮短信號路徑和提高電氣性能。然而,TSV 實施

2024-12-06 09:19:36 4743

4743

Hello,大家好,今天我們來分享下什么是先進封裝中的TSV/硅通孔技術。 TSV:Through Silicon Via, 硅通孔技術。指的是在晶圓的硅部分形成一個垂直的通道,利用這個垂直的通道

2024-12-17 14:17:51 3345

3345

先進封裝簡介 先進封裝技術已成為半導體行業創新發展的主要推動力之一,為突破傳統摩爾定律限制提供了新的技術手段。本文探討先進封裝的核心概念、技術和發展趨勢[1]。 圖1展示了硅通孔(TSV)技術

2024-12-18 09:59:38 2451

2451

Advanced Packaging) - 4 Chiplet 異構集成(下) 先進封裝技術(Semiconductor Advanced Packaging) - 5 TSV 異構集成與等效熱仿真 先進封裝技術

2024-12-24 10:57:32 3383

3383

Advanced Packaging) - 4 Chiplet 異構集成(下) 先進封裝技術(Semiconductor Advanced Packaging) - 5 TSV 異構集成與等效熱仿真 先進封裝技術

2024-12-24 10:59:43 3078

3078

TSV 三維封裝技術特點鮮明、性能好、前景廣闊, 是未來發展方向,但是 TSV 堆疊芯片這種結構和工 藝復雜性的提高,為三維封裝的可靠性控制帶來了 挑戰。主要體現在以下 4 個方面 :(1) TSV

2024-12-30 17:37:06 2629

2629 玻璃通孔(TGV,Through-Glass Via)技術是一種在玻璃基板上制造貫穿通孔的技術,它與先進封裝中的硅通孔(TSV)功能類似,被視為下一代三維集成的關鍵技術。TGV技術不僅提升了電子設備

2025-02-02 14:52:00 6697

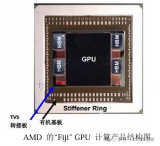

6697 高性能計算機中日益廣泛采用“處理器+存儲器”體系架構,近兩年來Intel、AMD、 Nvidia都相繼推出了基于該構架的計算處理單元產品,將多個存儲器與處理器集成在一個TSV硅轉接基板上,以提高計算

2025-01-27 10:13:00 3792

3792

在現代半導體封裝技術不斷邁向高性能、小型化與多功能異構集成的背景下,硅通孔(TSV,Through-SiliconVia)工藝作為實現芯片垂直互連與三維集成(3DIC)的核心技術,正日益成為先進封裝

2025-04-17 08:21:29 2508

2508

日月光半導體最新推出FOCoS-Bridge TSV技術,利用硅通孔提供更短供電路徑,實現更高 I/O 密度與更好散熱性能,滿足AI/HPC對高帶寬與高效能的需求。

2025-05-30 15:30:42 1120

1120 TGV(Through Glass Via)和TSV(Through Silicon Via)是兩種用于實現不同層面之間電氣連接的技術。

2025-06-16 15:52:23 1608

1608

在半導體三維集成(3D IC)技術中,硅通孔(TSV)是實現芯片垂直堆疊的核心,但受深寬比限制,傳統厚硅片(700-800μm)難以制造直徑更小(5-20μm)的TSV,導致芯片面積占比過高,且多層堆疊后總厚度可能達毫米級,與智能手機等應用對芯片厚度的嚴苛限制(通常<1mm)沖突。

2025-07-29 16:48:59 1367

1367

相較于傳統CMOS工藝,TSV需應對高深寬比結構帶來的技術挑戰,從激光或深層離子反應刻蝕形成盲孔開始,經等離子體化學氣相沉積絕緣層、金屬黏附/阻擋/種子層的多層沉積,到銅電鍍填充及改進型化學機械拋光(CMP)處理厚銅層,每一步均需對既有設備與材料進行適應性革新,最終構成三維集成的主要工藝成本來源。

2025-08-01 09:13:51 1977

1977 在TSV制造技術中,既包含TSV制造技術中通孔刻蝕與絕緣層的相關內容。

2025-08-01 09:24:23 1781

1781

HBM通過使用3D堆疊技術,將多個DRAM(動態隨機存取存儲器)芯片堆疊在一起,并通過硅通孔(TSV,Through-Silicon Via)進行連接,從而實現高帶寬和低功耗的特點。HBM的應用中,CowoS(Chip on Wafer on Substrate)封裝技術是其中一個關鍵的實現手段。

2025-09-22 10:47:47 1618

1618 技術區別TSV硅通孔(ThroughSiliconVia),指連接硅晶圓兩面并與硅襯底和其他通孔絕緣的電互連結構。硅中介層有TSV的集成是最常見的一種2.5D集成技術,芯片通常通過MicroBump

2025-10-11 16:39:24 746

746

電子發燒友App

電子發燒友App

評論