文章來源:學習那些事

原文作者:前路漫漫

本文主要講述什么是系統級封裝技術。

互連技術

從封裝內部的互連方式來看,主要包含引線鍵合、倒裝、硅通孔(TSV)、引線框架外引腳堆疊互連、封裝基板與上層封裝的凸點互連,以及扇出型封裝和埋入式封裝中的重布線等。在同一個系統級封裝(SiP)結構里,可以同時存在多種內部互連方式。例如,引線鍵合與倒裝芯片相結合,能夠實現堆疊型封裝,其中包括基于中介層的內部互連和芯片間直接互連這兩種堆疊型封裝形式。

SIP 結構

系統級封裝(SIP)的結構由其應用需求、成本等多種因素共同決定,而結構又會對封裝的效率和密度產生影響。

1.引線框架形式

小外形封裝(SOP)、四方扁平封裝(QFP)、方形扁平無引腳封裝(QFN)、柵格陣列封裝(LGA)等封裝類型都屬于引線框架結構的封裝形式,芯片與引線框架之間采用引線鍵合的方式實現互連,其結構又可分為水平結構、雙面結構、芯片堆疊、封裝堆疊以及上述多種形式的組合結構等。

2.基板形式封裝

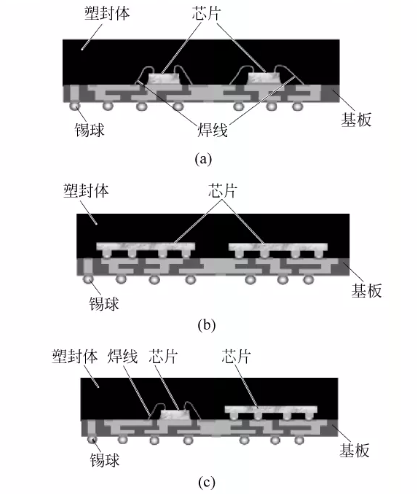

基板形式的封裝通常采用陣列引腳方式,涵蓋球柵陣列封裝(BGA)、柵格陣列封裝(LGA)以及具有微小焊球陣列的芯片級封裝(CSP)。基板的類型包括陶瓷基板、有機基板和撓性基板等。這類封裝內部芯片之間以及芯片與基板之間的互連方式主要有引線鍵合、倒裝、硅通孔(TSV)等,同時配合重布線技術。其結構又能夠分為 2D、2.5D 和 3D 封裝形式,以及在這些基本結構基礎上形成的進一步混合結構。

2D 封裝結構根據芯片之間信號的互連方式,又可分為引線鍵合互連、倒裝互連,以及采用球焊工藝與倒裝工藝相結合的引線鍵合和倒裝混合互連。

2.5D 封裝的詳細結構可參考之前文章中關于 2.5D 封裝的內容。

3D 封裝結構包含基于基板的芯片堆疊、封裝堆疊、雙面封裝等。芯片堆疊又能分為引線鍵合互連、引線鍵合與倒裝混合互連、基于硅通孔(TSV)的芯片堆疊等結構,具體內容也可參考之前文章中關于芯片堆疊的相關介紹。封裝堆疊主要包括基于載帶互連的封裝堆疊和基于焊球互連的封裝堆疊,具體內容也可參考關于封裝堆疊的相關文章介紹。

3.晶圓級芯片尺寸封裝(WLCSP)、扇出型晶圓級封裝(FOWLP)和埋入式封裝結構

在這類封裝中,重布線和凸點發揮著主要的互連作用。其結構同樣可以分為 2D、2.5D 和 3D 封裝形式,以及在這些基本結構基礎上形成的進一步混合結構。

無源元器件與集成技術

根據系統級封裝(SIP)的定義,為了更好地實現系統功能,SIP 中可以包含無源元器件,在某些情況下還需要大量的無源元器件。

無源元器件通常涵蓋電阻、電容、電感、濾波器、諧振器等。它們可分為分立的表面貼裝技術(SMT)類型無源元器件,以及集成無源器件(Integrated Passive Device,IPD)。

1.分立的無源元器件

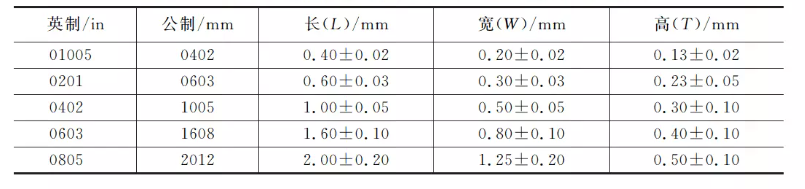

SIP 所使用的分立無源元器件屬于 SMT 類型,其最初源于印刷電路板(PCB)組裝中使用的 SMT 無源元器件,目前在大部分應用場景中,兩者仍處于共享狀態。SIP 對 SMT 無源元器件的要求比普通 SMT 更高,這也推動了 SMT 元器件向持續微型化的方向發展。系統級封裝中常用的貼片電阻、電容和電感有著相應的標準尺寸參數。

SIP 集成 SMT 類型分立無源元器件的方法主要是表面貼裝工藝,該工藝源于 PCB 組裝所采用的表面貼裝工藝,兩者的工藝內容基本一致。不過,SIP 對貼裝精度、工藝溫度以及殘留控制的要求更為嚴格。

2.集成無源器件

分立無源元器件存在占用面積大、貼裝成本高的缺點。

集成無源器件技術是通過薄膜層壓、晶圓制造平臺及工藝、介質膜埋入等方式,將電阻、電容、電感等無源器件集成在基板、晶圓表面或基板內部,同時也能將濾波器、耦合器、天線等射頻無源器件集成在基板或封裝表面內。這種技術是實現 SMT 小型化、高性能和低價格的有效途徑之一。

主要的集成方式包括集成于低溫共燒陶瓷(LTCC)、多芯片模塊(MCM-D)、晶圓級封裝(WLP)、扇出型晶圓級封裝(FOWLP)、埋入式、硅通孔(TSV)等結構中。

基于 LTCC 的無線射頻系統級封裝應用組件庫已被開發,該組件庫采用緊湊的電感器和電容器拓撲結構,其中 1.4nH 電感器的品質因數(Q 值)可高達 100。

薄膜多層 MCM-D 技術被證實是集成高性能無線前端系統的可行方法。由于采用高質量的電介質和銅金屬化工藝,能夠制作出高品質的傳輸線和電感器,同時還能實現帶通濾波器、功率分配器、正交耦合器、微波饋通、DECT 壓控振蕩器以及 14GHz 低噪聲放大器等器件。

利用 WLP 工藝可以制作出電感、電容、電阻、傳輸線等元件,并已實現可倒裝的 LC 濾波器和多個電阻集成的兩種集成無源器件(IPD)。

2017 年,中國電子科技集團公司第五十八研究所的周秀峰等人提出了以扇出型晶圓級封裝(FOWLP)為基礎的高 Q 值集成無源器件(IPD)。他們選擇玻璃作為襯底,借助玻璃通孔(TGV)制作出三維結構電感,成功制備出 Q 值高達 70 的電感。研究結果顯示,基于嵌入式晶圓級封裝(eWLP)的插入器集成無源器件,在異構系統集成方面表現先進,且具有外形尺寸小、電氣性能優異等顯著優勢。2010 年,英特爾公司的 Telesphor Kamgaing 等人研發出在多層有機封裝基板的核心層中埋入小尺寸射頻集成無源器件(IPD)的技術。

2011 年,Dzafir Shariff 等人實現了將集成無源器件(IPD)與硅通孔(TSV)集成到一塊減薄至 100μm 的硅轉接板上。2020 年,臺積電的 W.T.Chen 等人推出了硅通孔(TSV)深槽電容。2021 年,西安理工大學的 Fengjuan Wang 等人設計出基于硅通孔(TSV)技術的三種五階超小型發夾式帶通濾波器。

新型異質元器件與集成技術

為了更全面地實現系統功能,系統級封裝(SIP)中還可包含其他異質元器件,例如聲表面波器件、聲體波器件、晶振、天線、微機電系統(MEMS)、發光二極管(LED)、圖像傳感器、光波導,以及其他半導體(如砷化鎵(GaAs)、碳化硅(SiC)、氮化鎵(GaN)、鍺硅(GeSi))器件等。

電磁干擾屏蔽技術

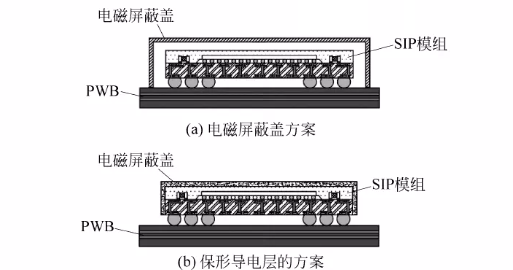

為確保電子設備不受外界電磁干擾,同時不對周圍其他電子設備產生電磁干擾,必須進行電磁屏蔽設計。電磁屏蔽設計已廣泛應用于手機射頻的功率放大模組、無線通信的 WiFi 模組、智能穿戴手表的內存 / 無線接入點 / 近場通信模組等領域。系統級封裝(SIP)實現封裝級電磁屏蔽主要有兩種方式。

第一種是電磁屏蔽蓋方案,通過回流工藝將電磁屏蔽蓋直接焊接在線路板上,從而覆蓋需要屏蔽的封裝體。

第二種是保形導電涂層或鍍層方案,即在封裝體的頂面和四個側面通過保形涂覆一層導電材料來實現電磁屏蔽。保形導電涂層的涂覆方法包括導電層噴涂、導電層印刷、電鍍、化學鍍、蒸發、濺射等。

與屏蔽蓋方案相比,保形導電涂層或鍍層方案具有諸多優勢:屏蔽導電層緊密貼合封裝體,不會占用線路板額外空間;無需額外設計制作屏蔽蓋,也省去了額外的回流工藝,大幅降低了成本。

對于保形導電層方案,基板上通過兩種方式實現鍍層的接地設計:一是在基板內層邊緣開設接地孔,孔中心與封裝外緣對齊,封裝切割后會露出通孔側壁,在完成涂層或鍍層工藝后,即可實現保形導電層與通孔金屬的連接,進而達成接地;二是將接地設計延伸至基板表面邊緣,模塑尺寸設計得比接地層小,模塑后接地層會顯露出來,導電涂層或鍍層工藝完成后便能實現接地。

無論是通過接地孔還是邊緣接地層進行接地設計,都需要保證一定的連接數量和橫截面積,以確保與外層鍍層的穩定連接。

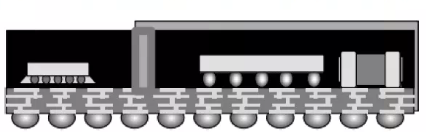

對于結構復雜的 SIP 封裝,若封裝內部集成了天線和其他子系統,天線以外的部分需要屏蔽,或者封裝內部各子系統之間存在相互干擾,就需要在封裝內部進行隔離。此外,大尺寸 SIP 封裝的整個屏蔽結構電磁諧振頻率較低,加之數字系統自身噪聲帶寬較寬,容易在 SIP 內部形成共振,導致系統無法正常工作。因此,封裝內部的局部屏蔽應用日益增多,即在封裝內部構建屏蔽墻,與封裝表面的保形屏蔽層共同將各子系統完全隔離。屏蔽墻的具體實現方法是通過激光打穿塑封體,露出封裝基板上的接地銅箔,再灌入導電填料形成。另外,劃區屏蔽將屏蔽腔劃分成多個小腔體,縮小了屏蔽腔尺寸,使其諧振頻率遠高于系統噪聲頻率,從而避免電磁共振,保障系統穩定運行。

-

SiP

+關注

關注

5文章

540瀏覽量

107716 -

系統級封裝

+關注

關注

0文章

44瀏覽量

9371 -

倒裝芯片

+關注

關注

1文章

119瀏覽量

16843

原文標題:系統級封裝技術解析

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

SiP(系統級封裝)技術的應用與發展趨勢

Endicott Interconnect投放系統級封裝設計

倒裝芯片和晶片級封裝技術及其應用

基于系統級封裝技術的車用壓力傳感器

系統級封裝技術綜述

系統級封裝電磁屏蔽技術介紹

系統級封裝技術解析

系統級封裝技術解析

評論