文章來源:學習那些事

原文作者:前路漫漫

本文主要講述硅通孔電鍍材料。

硅通孔(TSV)技術借助硅晶圓內部的垂直金屬通孔,達成芯片間的直接電互連。相較于傳統引線鍵合等互連方案,TSV 技術的核心優勢在于顯著縮短互連路徑(較引線鍵合縮短 60%~90%)與提升互連密度(最高可達 1500 I/O/mm2),因此能實現封裝體的輕薄化(厚度可降至 50μm 以下)與高集成度,是三維(3D)集成封裝領域不可或缺的關鍵技術。

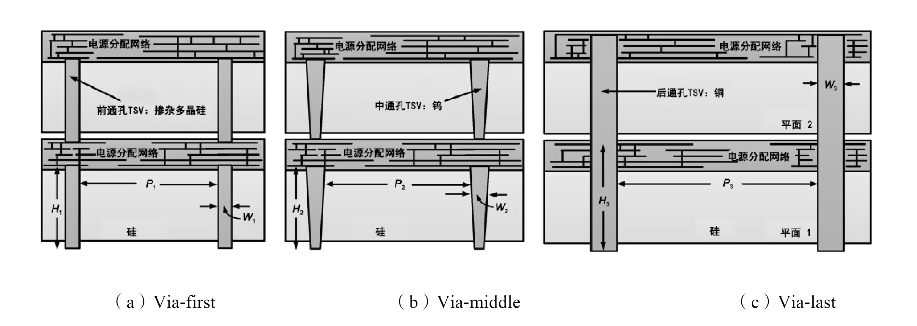

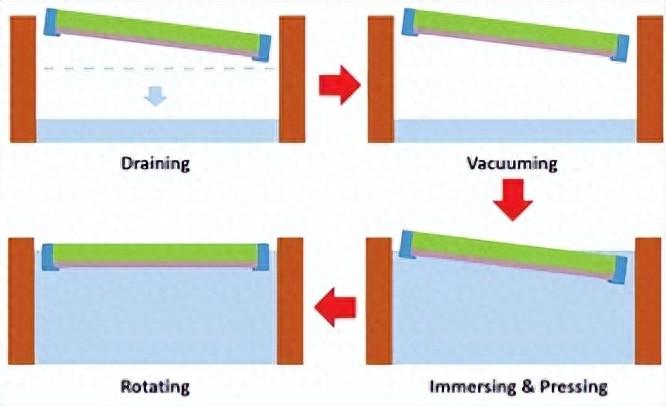

依據 TSV 制造工序在晶圓全流程工藝中的時序順序,可將其劃分為前通孔(Via-first)、中通孔(Via-middle)與后通孔(Via-last)三類技術(如圖1所示)。其中,前通孔技術的 TSV 制備需在前道工序(FEOL,主要負責晶體管等核心器件制造)啟動前完成,故通孔不會穿透后續形成的金屬互連層;中通孔技術的 TSV 制造介于 FEOL 與后道工序(BEOL,側重金屬布線與封裝前處理)之間,同樣不會破壞金屬互連層;后通孔技術的 TSV 形成于 BEOL 之后,因此通孔會完全穿透已成型的金屬互連層,適配靈活度更高的芯片集成場景。

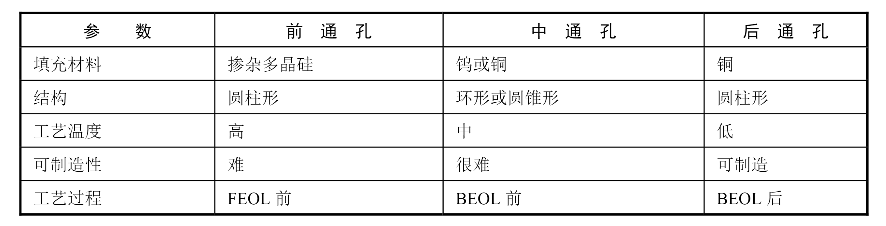

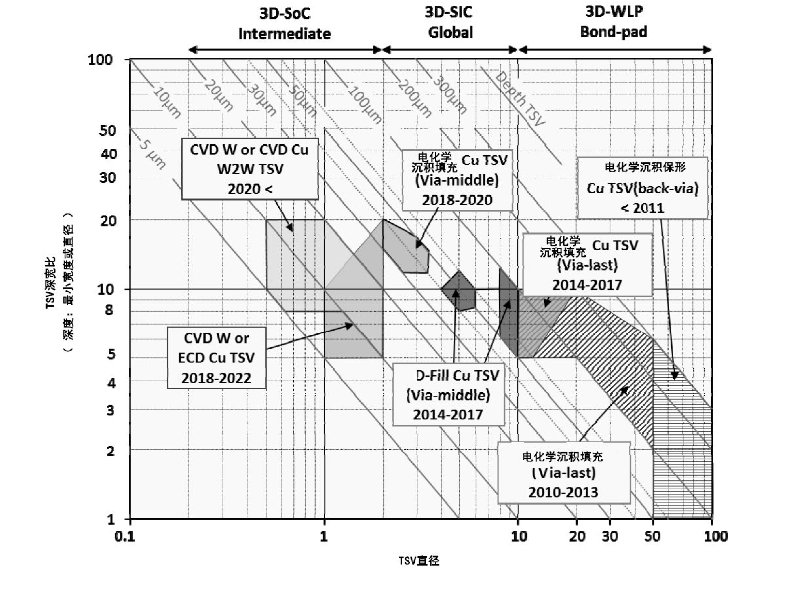

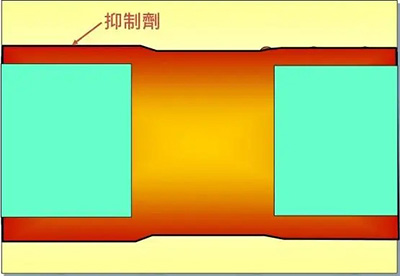

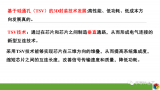

盡管前、中、后通孔技術的制造時序存在差異,但三者的核心工藝環節一致,均包含通孔刻蝕、通孔薄膜沉積、通孔填充、化學機械研磨(CMP)、超薄晶圓減薄等步驟,各工藝的性能指標對比如表 1 所示。TSV 的電互連功能需通過導電材料填充實現,而填充方式與材料的選擇,主要取決于 TSV 的制造階段與尺寸參數(如孔徑、深寬比)(如圖2所示)。目前主流的 TSV 填充方式分為兩類:電鍍與化學氣相沉積(CVD)。通常而言,若 TSV 孔徑較小(2μm 以下),液體電鍍液難以滲透至微孔內部,易形成空洞或縫隙,因此需依賴 CVD 技術實現無缺陷填充,常用的 CVD 導電材料包括銅、鎢、多晶硅等;而當前先進封裝中應用的 TSV 孔徑多在 5μm 以上,從工藝效率(電鍍填充速率較 CVD 快 3~5 倍)與成本(電鍍設備投入較 CVD 低 40% 左右)綜合考量,電鍍成為主流填充方式。

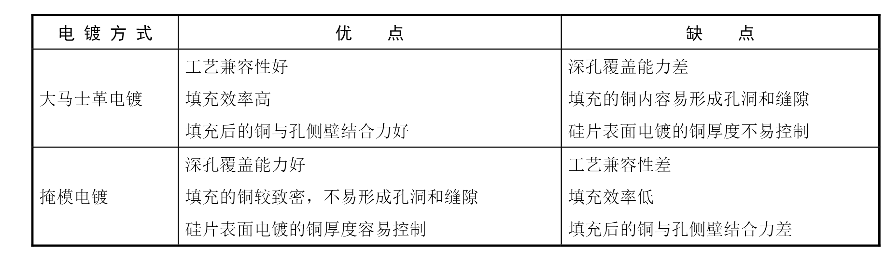

單質金屬銅具備優異的電導率(59.6 S/m)與熱導率(401 W/(m?K)),且電鍍銅工藝具備多重優勢:設備結構簡單、采購成本較低,可在室溫與常壓環境下操作;在優化的工藝參數(如電流密度 1~3 A/dm2、pH 值 1.8~2.2)下,能在水溶液體系中形成均勻性偏差 < 5% 的銅沉積層;沉積速率可達 1~5 μm/h,適配產業化大批量生產需求;同時與傳統 FEOL、BEOL 工藝兼容性良好,因此電鍍銅被視為先進封裝中 TSV 填充的最優方案。TSV 電鍍銅工藝主要分為大馬士革電鍍(Damascene Electroplating)與掩模電鍍(Through Mask Electroplating)兩類。

大馬士革電鍍的工藝流程為:先在晶圓表面通過光刻工藝制作圖形,形成具備特定深寬比(孔深與孔徑的比值,通常為 5:1~20:1)的盲孔;隨后沉積種子層(多為銅 - 鈦復合層,厚度 50~100nm),且種子層覆蓋圖形表面與盲孔內壁;電鍍過程中,盲孔內部與晶圓表面均會沉積金屬銅;電鍍結束后,需通過化學機械研磨(CMP)工藝去除晶圓表面多余的銅層,僅保留盲孔內的銅填充體。

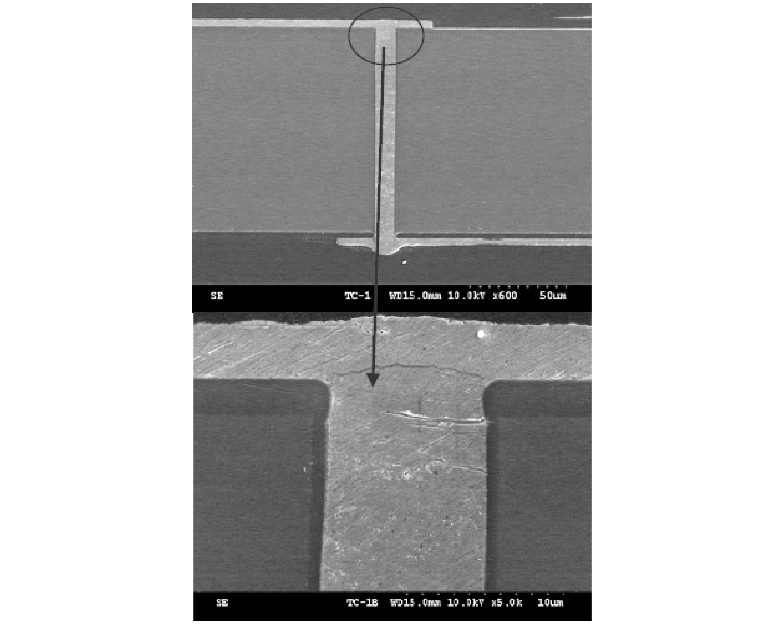

掩模電鍍的流程則有所不同:先在晶圓表面沉積種子層,再通過光刻工藝制作圖形,此時種子層僅在圖形暴露區域可見;電鍍過程中,金屬銅僅在種子層暴露區域沉積;電鍍完成后,需采用蝕刻工藝去除未電鍍區域的種子層,避免殘留金屬引發短路。兩類工藝的優缺點對比如表2所示。此外,需注意銅與硅的熱膨脹系數差異顯著 —— 常溫下銅的熱膨脹系數為 17.7 ppm/K,而硅僅為 2.5 ppm/K,當 TSV 孔徑較大(>15μm)或密度較高(>100 個 /mm2)時,銅填充體與硅基體在溫度循環過程中會產生顯著熱應力,可能導致 TSV 互連結構失效。如圖 3所示,TSV 結構經 1000 次熱循環(-40℃~125℃)后,其頂部再布線層已出現明顯裂紋。

硅通孔電鍍材料在先進封裝中的應用

TSV 技術通過芯片垂直方向的互連縮短路徑長度,從而降低信號傳輸延遲(可減少至 10ps 以下)、降低寄生電容與電感(電容可降至 0.1pF 以下),最終實現電子元器件與芯片間的低功耗(功耗降低 20%~30%)、高速通信(傳輸速率提升至 100Gbps 以上)與高帶寬,為元器件三維集成提供核心支撐。

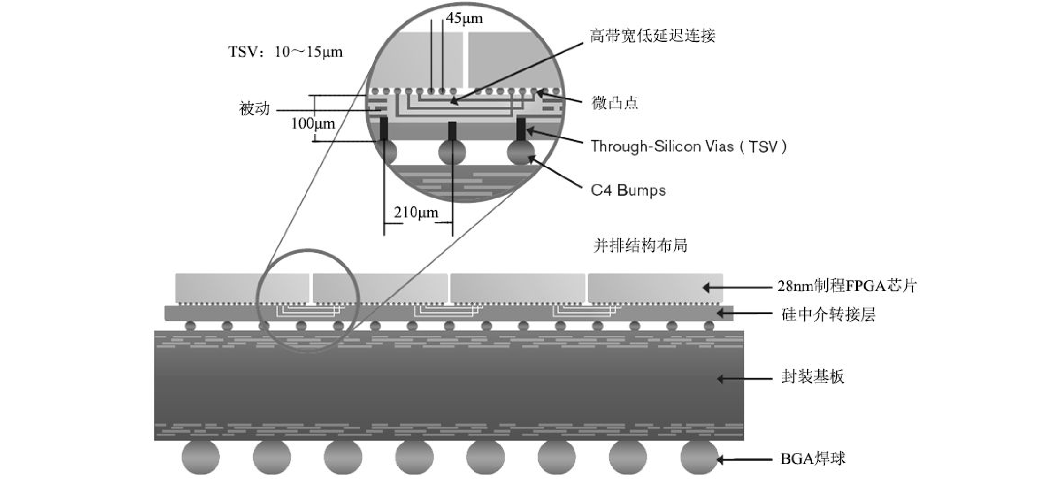

目前,基于 TSV 技術的三維集成已廣泛應用于多個領域:存儲器三維堆疊(如 3D NAND、DRAM 堆疊)、多芯片集成的硅中介轉接層(Silicon Interposer)、射頻(RF)模組、微機電系統(MEMS)及圖像傳感器(CIS)的 2.5D/3D 集成與組裝。例如,賽靈思(Xilinx)Virtex 7 系列 FPGA 芯片與三星電子(Samsung Electronics)面向服務器領域的 RDIMM DDR4 SRAM 存儲模塊,均采用 TSV 技術實現高密度集成;如圖 4 所示的 Xilinx Virtex-7 2000T FPGA 組裝結構中,硅中介轉接層的 TSV 孔徑為 10~15μm,深寬比約為 8:1。

-

電鍍

+關注

關注

16文章

477瀏覽量

25735 -

TSV

+關注

關注

4文章

137瀏覽量

82633 -

硅通孔

+關注

關注

2文章

28瀏覽量

12114

原文標題:硅通孔電鍍材料

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一種用于先進封裝的圓臺硅通孔的刻蝕方法

硅通孔封裝工藝流程與技術

TSV硅通孔填充材料

【轉帖】影響PCB電鍍填孔工藝的幾個基本因素

寧波材料所在先進氣體傳感材料與傳感器關鍵技術方面取得進展

晶圓微凸點技術在先進封裝中的應用

Chiplet在先進封裝中的重要性

硅通孔電鍍材料在先進封裝中的應用

硅通孔電鍍材料在先進封裝中的應用

評論