文章來源:學習那些事

原文作者:小陳婆婆

本文主要講述TSV制造技術里的通孔刻蝕與絕緣層。

TSV制造技術

在三維集成電路工藝中,TSV(硅通孔)制造作為核心環節,其復雜性與成本占比尤為突出。

相較于傳統CMOS工藝,TSV需應對高深寬比結構帶來的技術挑戰,從激光或深層離子反應刻蝕形成盲孔開始,經等離子體化學氣相沉積絕緣層、金屬黏附/阻擋/種子層的多層沉積,到銅電鍍填充及改進型化學機械拋光(CMP)處理厚銅層,每一步均需對既有設備與材料進行適應性革新,最終構成三維集成的主要工藝成本來源。

本文重點介紹其通孔刻蝕與絕緣層,分述如下:

通孔刻蝕

通孔刻蝕工藝對比

絕緣層

通孔刻蝕

在三維集成電路制造中,TSV通孔刻蝕作為核心工藝環節,其技術難度與成本占比始終居于首位。由于TSV需實現微米級深度、高深寬比(通常超過20:1)的垂直結構,對刻蝕技術提出了極高要求:需兼顧高刻蝕速率以降低生產成本,同時保證側壁光滑度以減少后續介質層與阻擋層沉積缺陷,并嚴格控制掩膜層下橫向刻蝕以避免短路或銅擴散等可靠性問題。

當前主流的通孔刻蝕方案分為濕法與干法兩大類,濕法刻蝕雖能實現高孔型控制精度,但速率較慢,難以滿足量產需求;干法刻蝕則以博世(Bosch)工藝(即深反應離子刻蝕DRIE)和激光刻蝕為主,其中Bosch工藝憑借高選擇比與垂直度優勢,成為高深寬比TSV的首選方案,但其側壁起伏大、掩膜下橫向刻蝕明顯(可達500nm)的缺陷,曾一度限制其應用——傳統Bosch工藝需通過縮短刻蝕周期、提高交替頻率來抑制側壁粗糙度,但此舉會降低刻蝕速率與選擇比,抵消其效率優勢。

近年行業通過射頻功率源與氣體調制技術的革新,實現了更高等離子體密度與氟基團濃度,在保證刻蝕速率的同時顯著優化側壁質量,部分先進設備甚至可在不犧牲速率的前提下獲得亞納米級光滑側壁,為先通孔工藝的可靠性提升奠定基礎。

低溫刻蝕技術則是另一重要分支,其無側壁起伏、無聚合物殘留的特性,大幅降低了后續介質層沉積難度與電場集中風險,且刻蝕后殘余物可隨溫度回升自動揮發,避免了腔體清洗與殘留物去除工藝,簡化了流程并提升器件可靠性。配合磁增強電容耦合等離子體(CCP)設備與腔體結構優化,低溫刻蝕已能實現直徑1-5μm、深寬比超20:1的深孔加工,速率達20μm/min,片間非一致性低于1%,同時保留了側壁光滑、無橫向刻蝕的優勢。

值得關注的是,基于磁中性環路放電(NLD)的常溫穩態刻蝕技術近年發展迅速,其結合高等離子體密度與化學活性優勢,在實現小直徑盲孔(<100nm)加工的同時,刻蝕速率較低溫工藝提升顯著,且無需復雜低溫系統,設備復雜度更低。針對后通孔集成工藝中SiO?介質層刻蝕引發的電子吸附與氟離子偏置問題,行業通過C?F?/Ar/O?等離子體沉積側壁阻擋層(厚度100-200nm),并動態調整平板電容功率(如初期30W物理轟擊去除底部阻擋層),有效抑制了橫向刻蝕,同時平衡了選擇比與工藝效率。

此外,為應對PVD沉積擴散阻擋層/種子層的方向性局限及電鍍空洞問題,錐形TSV結構逐漸成為優化方向。當錐形角度控制在83-85°時,可顯著降低深孔內層材料沉積難度,提升電鍍Cu柱的均勻性與可靠性,盡管其電性能仍需進一步驗證,但已成為高深寬比TSV工藝集成的重要探索方向。

通孔刻蝕工藝對比

在TSV通孔刻蝕工藝中,低溫刻蝕、Bosch刻蝕與激光刻蝕技術各具特點,其參數優化與工藝集成直接影響三維集成電路的可靠性及制造成本。

低溫刻蝕通過調控氧氣流量與襯底溫度,可精準控制刻蝕結構形貌:增加氧氣流量至總氣體流量的14%時,側壁保護層增厚使傾角從89.5°降至88°,但刻蝕速率下降約20%;而襯底溫度從-130℃升至-90℃時,刻蝕角度由94°收窄至88°,實現錐形結構。這種溫度敏感性使得低溫工藝在保留無聚合物殘留、側壁光滑優勢的同時,需平衡效率與形貌控制。

Bosch刻蝕雖以高深寬比加工能力著稱,但其側壁起伏控制難度更高。保護氣體流量調整雖可微調錐形角度,但離子轟擊效應限制了工藝窗口,且開口處橫向刻蝕易引發剖面非線性甚至互聯風險。為此,三步法工藝成為主流解決方案:先通過常規Bosch刻蝕完成50%-60%深度,再以SF?/O?/Ar混合氣體進行RIE刻蝕,利用O?的側壁保護與Ar的離子轟擊去除底部聚合物,最后通過無掩膜各向同性刻蝕擴展開口,實現光潔化錐形結構。該方法雖工序增加,但有效避免了中部擴展問題,適用于前通孔工藝。

激光刻蝕則以無掩膜、多材料兼容性見長,尤其適合低密度TSV應用。東芝圖像傳感器已采用該技術實現高效加工,其通過優化光路與掃描策略,使單臺設備產能達每秒2000個TSV,效率為DRIE的3倍,成本降至后者的1/15。然而,納秒激光器導致的側壁粗糙與殘留物問題,需結合HF-HNO?濕法刻蝕改善表面質量。盡管激光工藝在GaN、玻璃等非硅基材上仍具速度優勢,但其串行加工特性限制了高密度TSV的量產應用。

絕緣層

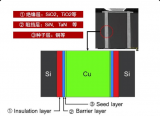

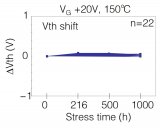

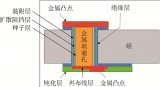

在TSV制造工藝中,絕緣層作為導體Cu柱與硅襯底間的關鍵隔離界面,其材料選擇與沉積工藝直接決定了器件的可靠性及制造成本。

不同于平面互連,TSV的高深寬比結構對絕緣層提出了特殊要求:除需具備優良絕緣性能、低應力及工藝兼容性外,更需解決深孔內的共形沉積難題。當前主流介質材料包括SiO?、Si?N?及高分子聚合物,其中SiO?憑借成熟的工藝基礎占據主導地位,但其沉積方式需根據工藝順序動態調整——先通孔工藝可采用950℃以上熱氧化生成致密SiO?,而中通孔及后通孔工藝因溫度限制(<450℃),需轉向APCVD、LPCVD或PECVD等中低溫CVD技術。以SiH?/N?O為反應源的PECVD-SiO?雖沉積溫度低,但共形能力受限,深寬比超過10:1時易出現覆蓋缺陷;基于TEOS的SACVD工藝通過優化氣體調制,可實現片內均勻性優于5%、擊穿場強達360MV/m(雖僅為熱氧化層的15%),但需保證厚度≥150nm以滿足50V耐壓需求。

Si?N?憑借其密實結構與抗Cu擴散能力,成為介質層與擴散阻擋層二合一的潛在方案。APCVD/LPCVD工藝在700-900℃下生成的化學計量比Si?N?(Si:N=3:4)雖拉應力較高(>400MPa),但通過富硅化調整可降至100MPa;PECVD工藝則通過頻率調控(13.56MHz降至50Hz)實現應力軟化,最低可達200MPa,同時保留對Cu擴散的阻擋效能。值得注意的是,Si?N?的臺階覆蓋能力仍弱于熱氧化SiO?,需結合深孔形貌優化沉積參數。

氮氧化硅(SiNO)作為柵極介質層的經典材料,其高介電常數(較SiO?提升約20%)與抗硼穿透特性,在先進制程中用于緩解短溝道效應。當引入TSV領域時,SiNO可同步實現絕緣與擴散阻擋功能,但單一材料仍難以完全替代TaN等專用阻擋層。

-

制造技術

+關注

關注

1文章

121瀏覽量

14966 -

TSV

+關注

關注

4文章

137瀏覽量

82624 -

刻蝕

+關注

關注

2文章

220瀏覽量

13776

原文標題:TSV制造技術——通孔刻蝕與絕緣層

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電線外徑測厚儀——絕緣層厚度便捷檢測

硅通孔(TSV)電鍍

基于數字圖像處理的電纜絕緣層參數測量系統

中微推出用于3D芯片及封裝的硅通孔刻蝕設備Primo TSV200E(TM)

導線絕緣層恢復材料和絕緣層恢復方法

技術普及篇|網線絕緣層

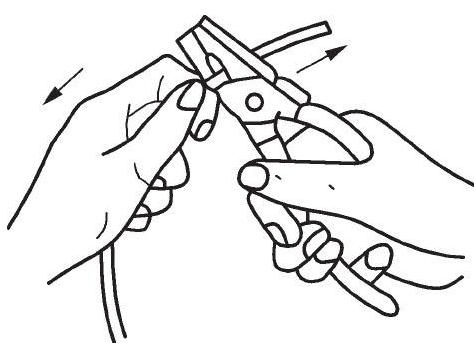

如何恢復導線的絕緣層_導線絕緣層的恢復方法

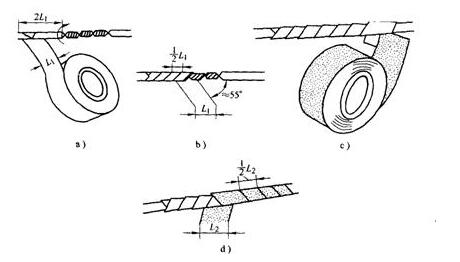

圖文詳解:導線絕緣層的剝削

TSV制造技術里的通孔刻蝕與絕緣層

TSV制造技術里的通孔刻蝕與絕緣層

評論