文章來源:Jeff的芯片世界

原文作者:Jeff的芯片世界

本文主要講述TSV的工藝技術。

硅通孔(Through Silicon Via,TSV)技術是一種通過在硅介質層中制作垂直導通孔并填充導電材料來實現芯片間垂直互連的先進封裝技術。作為三維系統級封裝(3D-SiP)的核心技術,TSV能夠顯著縮短互連路徑,降低寄生電容和電感,從而提升系統性能、降低功耗,并支持器件小型化與異構集成。與傳統水平的引線鍵合和倒裝芯片互連相比,TSV實現了芯片在垂直方向的堆疊與連接,被視為第三代封裝互連技術的重要代表。

TSV制造工藝概述

TSV制造主要包括通孔形成、側壁涂層和導體填充三大步驟。

1.通孔形成

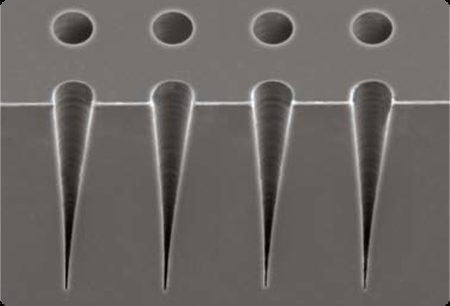

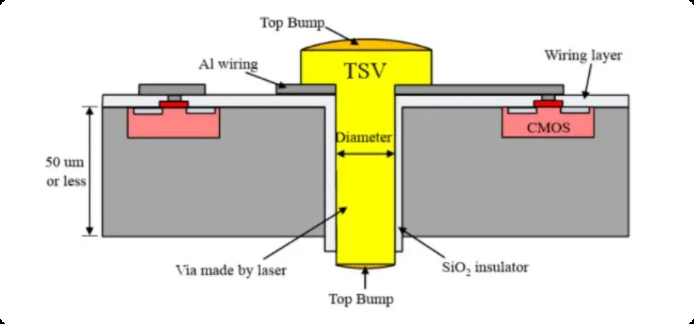

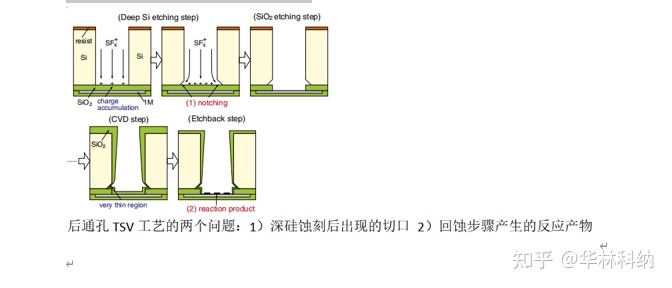

通孔形成通常采用深反應離子刻蝕(DRIE)、激光鉆孔或濕法刻蝕等方法。其中,Bosch刻蝕作為主流的干法刻蝕工藝,通過刻蝕與鈍化的交替循環,實現高深寬比的通孔刻蝕,深度可達數百微米,但也存在扇形側壁、微觀負載效應等問題,需通過優化射頻功率、氣體流量等參數改善。激光鉆孔利用高能激光束進行光熱燒蝕,具有高精度、無機械磨損的優點,但易產生熱影響區和濺渣沉積,可通過多脈沖紫外激光或添加掩膜等方式解決。濕法刻蝕早期使用KOH溶液,成本低但側壁不垂直且易污染,現代改進工藝如HNA刻蝕體系、TMAH工藝和光輔助電化學刻蝕提高了通孔圓度和CMOS兼容性。

2.側壁涂層

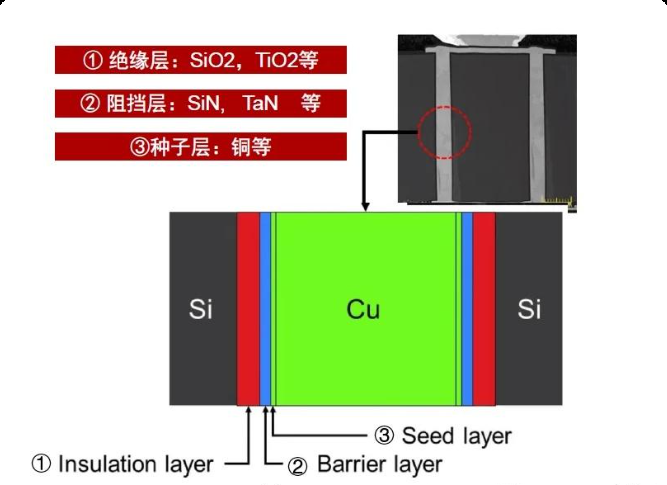

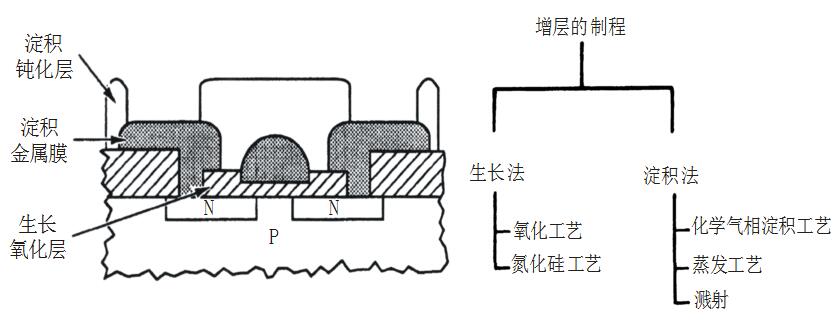

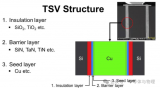

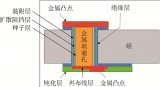

TSV側壁涂層包括絕緣層、阻擋層和種子層,直接影響電氣性能與可靠性。絕緣層常用SiO?,通過熱氧化法、PECVD或HDPCVD制備,用于防止漏電和串擾;阻擋層采用Ti、TiN或Ta等材料,通過原子層沉積、化學鍍或濺射工藝沉積,防止金屬離子擴散并提升粘合度;種子層如Ti/Cu或Ti/Au薄層,通過濺射形成,影響后續填充機制,高深寬比TSV中需解決涂層均勻性問題,可引入化學鍍CoWB等材料優化。

3.導體填充

導體填充以電鍍法為主,核心挑戰是避免電鍍角效應導致的空洞。采用Cu-Ni、Cu-W等新型填充材料可提升填充速率與質量;周期性反向脈沖(PPR)電鍍能細化晶粒、實現無空洞填充,但填充時間較長,需通過調整鍍液添加劑縮短周期。添加劑的使用需精確控制成分與比例,單一添加劑也可降低工藝復雜度。超聲波輔助電鍍通過聲流與空化效應加速傳質,提高填充速度與質量,且能減少添加劑使用,但需控制超聲波功率以避免降低銅與側壁的黏附性。

TSV鍵合工藝與應用

TSV鍵合工藝主要包括焊錫凸點、銅柱凸點(CPB)和混合鍵合。電鍍法是主流的凸點制備方式,通過光刻膠控制尺寸,但工序復雜、焊料成分難調控;非光刻工藝可低成本制備Sn-3.5Ag凸點,而焊膏壓印工藝通過模板壓印和回流焊簡化流程,但受模板限制難用于超細間距TSV,可結合激光邊緣技術改善。銅柱凸點結合光刻與電鍍,在TSV上形成高銅柱并鍍薄焊錫膜,實現更小間距、避免橋接,且散熱性和機械強度高,但熱處理中易形成金屬間化合物,需添加鎳層解決;焊錫注模(IMS)工藝可制備無鉛凸點,但需耐高溫光刻膠材料。混合鍵合實現介質層與金屬(如銅)界面的無縫鍵合,通過表面處理提高親水性和降低粗糙度,再經退火增強鍵合強度,但成本較高,且需優化等離子體處理以避免Cu?O形成。

TSV技術應用廣泛,涵蓋低密度與高密度場景。低密度應用如單個MEMS器件,通過TSV實現電信號從晶圓正面到背面的傳導,并將MEMS堆疊在CMOS芯片上,例如慣性傳感器集成,采用DRIE、MOCVD沉積銅等工藝。

高密度應用包括傳感器/MEMS陣列與CMOS集成,如CMOS圖像傳感器(CIS),索尼IMX400采用三層堆疊結構,通過TSV與重布線層互聯,TSV最小直徑達2.5μm。中介層技術(2.5D集成)作為芯片與封裝基板間的襯底,應用于多芯片集成與I/O再分配,如光電異構集成系統。多層與晶圓堆疊用于3D封裝與高帶寬存儲器(HBM)互聯,通過TSV與微凸點連接,實現薄形化晶圓堆疊,減小間隙與總厚度。

在具體應用方向上,TSV可分為背面連接、2.5D封裝和3D封裝。背面連接用于CMOS圖像傳感器和SiGe功率放大器,通過TSV替代引線鍵合,減小模組尺寸并簡化晶圓級封裝。2.5D封裝如FPGA器件,使用硅中介層實現密切連接,解決大尺寸芯片技術難題。3D封裝以存儲器堆疊為代表,如寬I/O DRAM,降低封裝高度與功耗,提升帶寬。

TSV技術優勢與挑戰

TSV技術的主要優勢包括縮短互連長度以降低信號延遲、電容和電感,從而提升通信速度與帶寬,同時降低功耗;支持垂直堆疊,實現器件小型化;促進異構集成,高效整合邏輯、內存和MEMS等不同功能芯片。

然而,TSV也面臨制造成本高、工藝復雜、熱應力問題等挑戰。成本高源于深硅刻蝕、電鍍填充等復雜步驟;熱應力因銅與硅的熱膨脹系數差異,可能導致介質層開裂或分層;工藝涉及刻蝕、涂層、填充和平坦化等多步驟,對精度要求極高。

未來展望與發展方向

TSV技術持續優化,推動3D-SiP向更高效、可靠的三維集成發展。未來創新方向包括通孔尺寸縮減、晶圓減薄、材料與工藝改進,以及應對散熱、信號傳輸和可靠性挑戰。

企業如臺積電通過CoWoS和InFO技術提升TSV產能,加速HBM商業化;三星電子在HBM封裝中推動高層數堆疊;英特爾利用Foveros 3D封裝實現邏輯與內存芯片整合;國內企業在CIS等領域實現技術突破,增強產業鏈競爭力。隨著集成電路封裝需求增長,TSV將在5G、人工智能、自動駕駛等領域發揮關鍵作用,但仍需解決可靠性、散熱和測試等問題以促進廣泛應用。

-

制造工藝

+關注

關注

2文章

213瀏覽量

21286 -

TSV

+關注

關注

4文章

137瀏覽量

82627 -

先進封裝

+關注

關注

2文章

533瀏覽量

1026

原文標題:TSV工藝技術介紹

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TSV技術的關鍵工藝和應用領域

TSV工藝流程與電學特性研究

硅通孔(TSV)電鍍

TSV關鍵工藝設備及特點

TSV的工藝流程和關鍵技術綜述

基于兩步刻蝕工藝的錐形TSV制備方法

TSV以及博世工藝介紹

TSV制造工藝概述

TSV制造工藝概述

評論