文章來源:學習那些事

原文作者:前路漫漫

本文主要講述什么是TSV工藝。

TSV工藝概述

2.5D/3D封裝技術作為當前前沿的先進封裝工藝,實現方案豐富多樣,會根據不同應用需求和技術發展動態調整,涵蓋芯片減薄、芯片鍵合、引線鍵合、倒裝鍵合、TSV、塑封、基板、引線框架、載帶、晶圓級薄膜工藝等多種類型。部分工藝需根據2.5D/3D封裝的特定要求進一步發展,例如3D封裝中的引線鍵合技術,對線弧高度、焊點尺寸等有了更高標準,需要工藝上的改良與創新。除TSV工藝外,本書已對多數相關技術進行過介紹,受篇幅限制,本章僅重點講解TSV工藝技術。

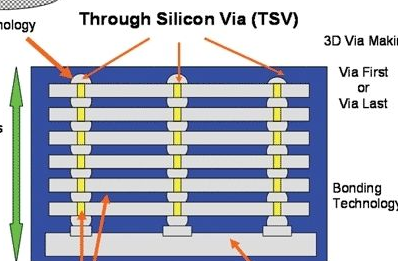

與引線鍵合相比,TSV能大幅縮短互連線長度,降低信號傳輸延遲與損耗,提升信號傳輸速度與帶寬,同時減少功耗并縮小封裝體積,是實現多功能、高性能、高可靠性,以及更輕、更薄、更小的系統級封裝的有效手段之一。作為2.5D/3D封裝的核心技術,TSV與其他采用基板、薄膜布線等中介的3D封裝不同,芯片間通過導電通孔與焊料鍵合連接,熱失配程度小,互連長度更短。

TSV的3D封裝性能優異且發展潛力巨大,因此被稱為第四代封裝技術。20世紀80年代中期,垂直TSV中填充導體的概念已被明確提出,盡管當時尚未實現。20世紀90年代中期,博世公司研發出深反應離子刻蝕(DRIE)技術,使得在硅晶圓上刻蝕出垂直深孔成為可能。20世紀末,成功實現了用鎢或多晶硅導體填充的高深徑比TSV。2000年以來,深孔內電鍍銅逐漸成為填充高深徑比TSV的主要方式。此后,晶圓鍵合、凸點制造、晶圓薄化及化學機械拋光等技術的進步,進一步推動了TSV封裝技術的完善。

TSV工藝流程

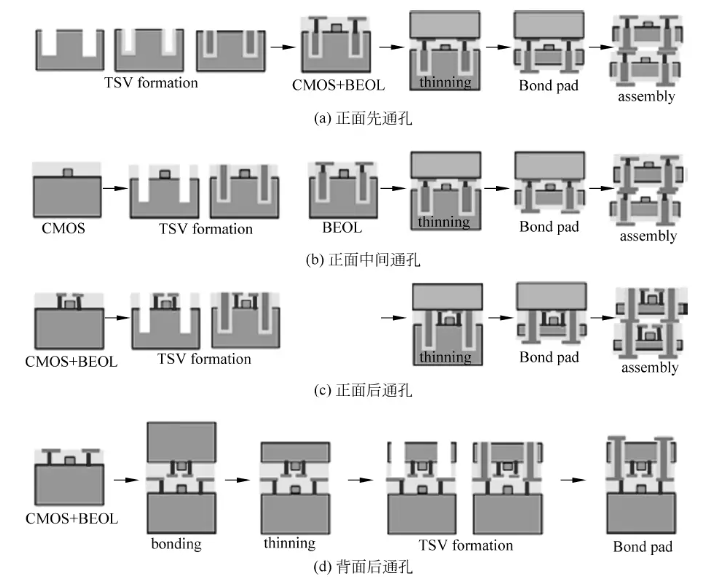

TSV技術本質上屬于晶圓級制程,因此其制作可融入集成電路制造工藝的不同環節,具體可分為正面先通孔、正面中間通孔、正面后通孔及背面后通孔四種類型。

正面通孔指在晶圓的有源電路面鉆孔。正面先通孔技術是在初始硅襯底上先形成通孔,也就是在芯片前道制造工藝的有源層形成之前就完成通孔制作,此時TSV制作可在晶圓制造廠前端金屬互連工序前進行。正面后通孔技術則是在芯片后道工藝完成后再制作通孔,該方案的顯著優勢是無需改變現有集成電路的流程與設計,同時還能降低種子層沉積成本、縮短電鍍時間并提高產能,目前已有部分廠商在高端Flash和DRAM領域采用這一技術。當TSV孔在CMOS與芯片后段制程(Back End of Line,BEOL)之間制作時,稱為正面中間通孔,其中BEOL指芯片制造的后段工序,始于單個器件完成后的第一層金屬互連,在晶圓制造廠內完成。背面后通孔技術是在芯片或晶圓與另一晶圓鍵合后,再在背面鉆孔。

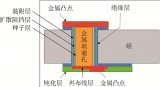

TSV制作的工藝流程具體如下:①在硅片上鉆制深孔,深度超過TSV的目標厚度;②沉積介質層;③在硅片表面及深孔內沉積阻擋層、黏附層與種子金屬層;④通過電鍍銅或采用其他導電材料填充深孔;⑤利用化學機械拋光實現表面平坦化,并去除多余的種子金屬層;⑥通過磨削或刻蝕使銅層或通孔導電層暴露出來。

TSV技術的關鍵工藝

TSV的關鍵工藝包括晶圓減薄、通孔制作和鍵合等環節。

1. 減薄

TSV工藝對晶圓厚度要求嚴格,需控制在75μm以內;隨著TSV封裝密度提升與孔徑縮小,晶圓厚度還在不斷減小,因此晶圓減薄成為TSV工藝的關鍵環節之一。傳統封裝的減薄工藝通常只需將晶圓減至200~350μm,特殊封裝也僅需減至150~180μm,此時硅片仍有足夠厚度承受減薄過程中磨削造成的損傷與內在應力,且自身剛性便于搬送。但TSV工藝要求晶圓減薄至50μm以下,如何減少減薄損傷、實現柔性晶圓的穩定搬送成為新的挑戰。傳統減薄工藝中,粗磨與精磨后殘留的表面損傷是導致硅片破碎的主要原因——磨削屬于物理損傷性工藝,通過物理施壓、損傷、破裂與移除過程去除硅材料。為消除這類表面損傷與應力,行業嘗試了干法拋光、濕法拋光、干法刻蝕、濕法刻蝕等多種方法。目前業界的主流解決方案是采用一體化設備,將硅片的磨削、拋光、保護膜去除及劃片膜粘貼等工序整合在同一設備中,通過機械式搬送系統使硅片從磨削到粘貼劃片膜的全過程都被吸附在真空吸盤上,始終保持平整狀態。當硅片粘貼到劃片膜上后,即使厚度薄于劃片膜,也會順應膜的形狀保持平整,不再發生翹曲或下垂,從而解決了搬送難題。

2. 通孔

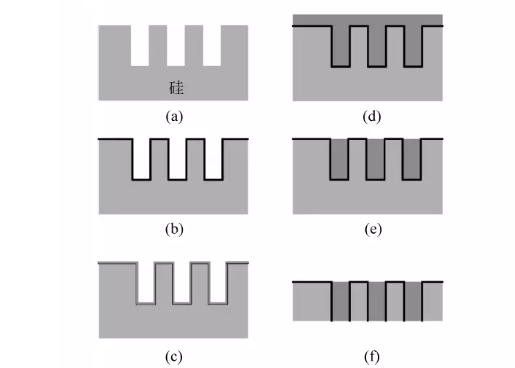

1) 鉆孔

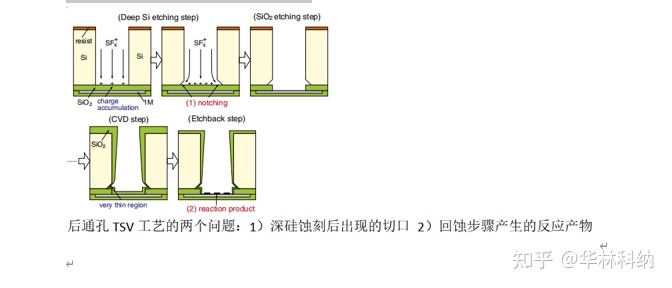

晶圓鉆孔是TSV工藝的核心環節,目前主要采用干法刻蝕(又稱Bosch刻蝕)與激光刻蝕兩種方式。Bosch刻蝕工藝最初為MEMS技術開發,其特點是快速交替進行硅去除(采用SF?等離子刻蝕)與側壁鈍化(采用CF?等離子沉積)過程。干法刻蝕速率可達50μm/min,深寬比能達到1:80,精度為亞微米級。

激光刻蝕無需掩膜,省去了光刻膠涂敷、曝光、顯影及去膠等工序。韓國三星公司已將該技術應用于存儲器堆疊中。激光刻蝕的深寬比約為7:1,性能弱于干法刻蝕,更適合芯片上通孔數量較少的場景;若通孔數量超過10000個,采用光刻結合干法刻蝕的效率更高。此外,當通孔尺寸縮小至10μm以下時,激光鉆孔能否進一步縮小孔徑仍面臨挑戰。

2) 通孔絕緣

通孔絕緣通常通過CVD工藝沉積氧化物(SiO?)絕緣層,原料多采用硅烷或TEOS。若在芯片電路制造完成后進行TSV絕緣與填充,為避免影響已完成的電路部分,需選擇適宜的沉積溫度。TEOS沉積的典型溫度為275~350℃,可獲得性能合適的功能性絕緣層;而對于CMOS圖像傳感器、存儲器等應用,則要求更低的沉積溫度。目前,部分設備制造商已開發出低溫氧化物沉積技術,可在室溫下沉積薄膜作為TSV的高效有機絕緣層。

3) 阻擋層、種子層與填鍍

在銅通孔工藝中,通常采用濺射方式沉積TiN黏附/阻擋層與銅種子層。但對于深寬比大于4:1的通孔,傳統PVD直流磁控技術的臺階覆蓋效果欠佳,而基于離子化金屬等離子體(IMP)的PVD技術可實現孔側壁與底部銅種子層的均勻沉積。由于電鍍銅成本較低,種子層沉積后通常采用電鍍銅填充通孔。不過,TSV電鍍時,孔口因尖端效應會聚集更多電力線,導致此處電流密度遠高于孔內;若不使用添加劑,孔口沉積速率會遠快于孔內,加之孔內銅離子交換困難,容易出現孔口填滿而孔內未完全沉積的情況。因此,需通過添加劑調節孔底部、側壁與表面的電鍍沉積速率(抑制孔口沉積、增強底部沉積),或采用周期反向脈沖電流電鍍,以實現通孔的完整填充。無空洞鍍銅填充耗時較長,會降低生產效率,這是TSV鍍銅填充面臨的問題。

3. TSV鍵合

TSV鍵合所采用的工藝包括金屬間鍵合技術與高分子黏結鍵合等。鍵合的核心目標是讓芯片或元件之間形成穩定的機械連接、電連接和熱傳導通道,將原本分立的芯片與元件整合為一個完整的封裝產品。

從鍵合過程的特點來看,金屬間鍵合主要分為熱壓鍵合和共晶鍵合兩類。例如,銅-銅鍵合采用熱壓鍵合方式,而銅錫、金錫等鍵合則屬于共晶鍵合。銅-銅熱壓鍵合的原理是:在真空環境或保護性氣氛中,對緊密貼合的兩個銅表面施加高溫和高壓,并保持足夠長的時間,使兩個鍵合面的銅原子充分擴散,最終融合為一個整體,從而實現鍵合。不過,這種鍵合方式耗時較長,對工藝條件的要求也更為嚴苛。

近年來,低溫金屬鍵合成為封裝領域的研究熱點。研究人員希望找到一種能在較低溫度下形成良好電連接和機械結合,且反應產物可耐受高溫的鍵合方式。銅-錫鍵合因其優異的電學和熱學性能,以及較低的鍵合溫度(錫的熔點為232℃)而成為首選。銅-錫共晶鍵合過程中,低溫下金屬錫熔化形成液態,促使銅與錫充分接觸,加速兩者相互擴散,快速生成亞穩態高熔點金屬間化合物Cu?Sn?(熔點415℃)和穩態化合物Cu?Sn(熔點676℃),進而完成鍵合。這種鍵合方式在多層堆疊時,能有效避免已鍵合部位因后續鍵合過程中的熱量而熔化,對三維封裝的可靠性至關重要。此外,由于錫焊料具有良好的形變能力,銅-錫鍵合對鍵合表面的平整度和潔凈度要求不高,即便表面存在一定起伏或微小顆粒,也能形成良好的鍵合。同時,液態錫能加快銅與錫的擴散速度,使鍵合效率更高。隨著互連密度的提升,最新發展的混合鍵合技術也可能成為重要選擇。

TSV應用發展情況

借助TSV技術可實現2.5D和3D封裝,這類封裝在當前3D封裝方案中,在封裝密度和互連長度方面均具有明顯優勢。因此,TSV的應用進展在一定程度上反映了3D封裝領域的前沿發展態勢。

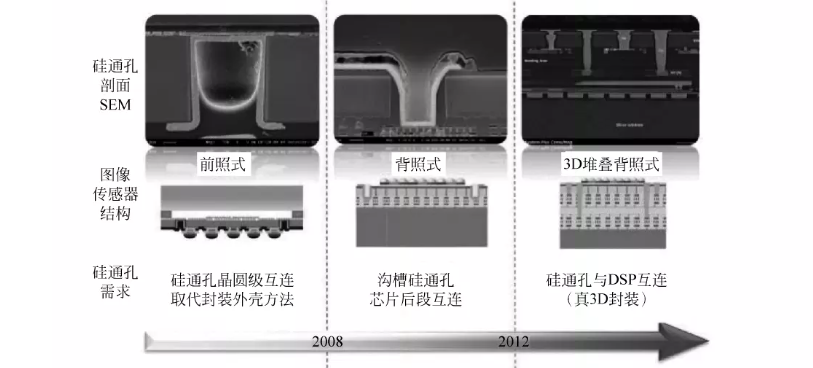

1. CMOS圖像傳感器

2006年,東芝公司推出了全球首個集成TSV技術的產品——CMOS圖像傳感器(CIS),并于2007年實現量產。性能提升與微型化是推動CIS發展的核心動力。搭載TSV的3D CMOS圖像傳感器,其發展歷程先后經歷了正面成像(FSI)、背面成像(BSI),再到混合3D堆疊BSI的階段。目前,CIS是TSV技術最大的應用市場。

2. MEMS領域應用

20世紀末,深反應離子刻蝕技術開始應用于MEMS領域,用于制造多晶硅TSV(如微懸臂梁、微機械超聲換能器陣列所用),以及單晶硅TSV(如微引擎的二氧化硅溝槽隔離結構)。進入21世紀后,多家MEMS制造商與代工廠陸續將慣性傳感器產品及相關制造服務推向商業化,其中就包含用于晶圓級真空封裝(WLVP)的氣隙隔離式硅TSV。與此同時,采用空心金屬TSV與WLVP技術的薄膜體聲波諧振器(FBAR)也實現商業化,廣泛應用于無線通信領域。將TSV與WLVP技術整合到MEMS中后,封裝尺寸與成本可降至原來的1/10到1/5,這大大加速了近十年來MEMS在消費電子與移動電子領域的普及。2014年,博世公司開發出基于正面中間通孔TSV的集成MEMS傳感器并投入市場,該產品所用TSV為10μm×100μm的通孔(深徑比10:1),通過銅電鍍制成,相比其他主流MEMS TSV集成封裝方案,顯著縮小了封裝的表面積與厚度。目前,MEMS已成為TSV技術的重要應用領域。 3. 存儲器領域應用

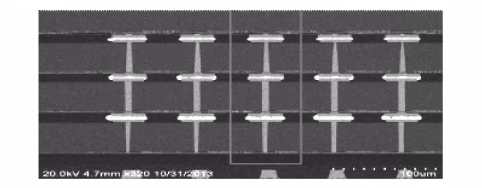

TSV技術能有效提升存儲器的容量與帶寬——借助高密度TSV垂直互連技術堆疊多個芯片,可顯著增強存儲器的容量與性能。主流存儲器制造商均已采用TSV 3D堆疊技術開發相關產品。2009年,三星公司推出基于TSV 3D封裝的8Gb 3D DDR3 DRAM,將待機功耗與工作功耗分別降低50%和25%,并通過300個TSV將I/O速率提升至1600Mb/s以上。2014年,該公司又發布采用TSV技術的16Gb 3D DDR4 SDRAM,其I/O速率達到2.4Gb/s,由4個芯片堆疊而成。

TSV技術在高帶寬存儲器(HBM)中也有重要應用。HBM堆疊并未與CPU或GPU進行物理集成,而是通過小間距高密度TSV轉接板實現互連。由于HBM具備接近芯片集成RAM的特性,因此擁有更快的速度與更高的帶寬,適用于對存儲器帶寬需求較高的場景。在高性能CPU/GPU應用中,2.5D TSV轉接板作為平臺型技術發揮著關鍵作用。存儲器(尤其是HBM產品)借助TSV技術,帶寬得到大幅提升。2014年,海力士公司發布了采用29nm工藝與TSV技術的1.2V 8Gb 8通道高帶寬存儲器堆疊DRAM,帶寬達128GB/s。目前,存儲器是TSV技術的主要應用市場之一。

三星3D DDR4 DRAM封裝

4. 其他領域應用

功率電子、模擬電子及通信等領域同樣是TSV技術的重要應用陣地。2021年,西安理工大學、西安電子科技大學與曼徹斯特大學的Fengjuan Wang團隊,針對6G移動通信需求,提出并研制出基于TSV技術的三種五階超小型發夾式帶通濾波器。

TSV技術展望

隨著TSV技術的持續演進,通孔尺寸不斷縮減,疊層中每層芯片的厚度也將進一步減小。研究表明,當硅片厚度減至5μm以下時,電路性能并不會出現明顯衰減。可以預見,未來十幾年內,傳統器件的發展將逐步觸及自身物理極限,后續突破難度可能大幅增加;而一維材料器件等新型器件目前仍停留在實驗室階段,難以實現大規模商業化落地。因此,在封裝層面持續提升集成度成為當前關鍵,未來幾年硅通孔技術仍將是微電子行業的研究熱點。存儲器、邏輯電路、CMOS圖像傳感器等快速發展的芯片應用領域對TSV的需求,將持續推動該技術的完善與升級。

此外,TSV技術還能實現不同類型芯片的異質集成——例如,手機功率放大器多采用GaAs工藝,通過TSV技術可將GaAs電路鍵合在CMOS電路上,形成完整功能電路。不過,在快速發展的同時,3D封裝目前仍面臨諸多挑戰,可靠性、散熱、材料匹配、芯片測試等方面的問題仍需深入研究,以推動硅通孔技術的商業化進程。

-

封裝技術

+關注

關注

12文章

605瀏覽量

69344 -

TSV

+關注

關注

4文章

138瀏覽量

82739 -

先進封裝

+關注

關注

2文章

557瀏覽量

1053

原文標題:TSV工藝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TSV工藝流程與電學特性研究

Linux技術的應用領域

3D封裝與硅通孔(TSV)工藝技術

深度解讀TSV 的工藝流程和關鍵技術

什么是TSV封裝?TSV封裝有哪些應用領域?

TSV關鍵工藝設備及特點

TSV的工藝流程和關鍵技術綜述

IGBT應用領域和IGBT燒結銀工藝

TSV 制程關鍵工藝設備技術及發展

TSV技術的關鍵工藝和應用領域

TSV技術的關鍵工藝和應用領域

評論