使用直接晶圓到晶圓鍵合來(lái)垂直堆疊芯片,可以將信號(hào)延遲降到可忽略的水平,從而實(shí)現(xiàn)更小、更薄的封裝,同時(shí)有助于提高內(nèi)存/處理器的速度并降低功耗。目前,晶圓堆疊和芯片到晶圓混合鍵合的實(shí)施競(jìng)爭(zhēng)異常激烈,這被

2025-05-22 11:24:18 1405

1405

3D堆疊像素探測(cè)器芯片技術(shù)詳解

2024-11-01 11:08:07 4435

4435

芯片堆疊封裝技術(shù)實(shí)用教程

2024-11-01 11:08:07 4273

4273

3D堆疊將不斷發(fā)展,以實(shí)現(xiàn)更復(fù)雜和集成的設(shè)備——從平面到立方體

2024-09-19 18:27:41 2348

2348

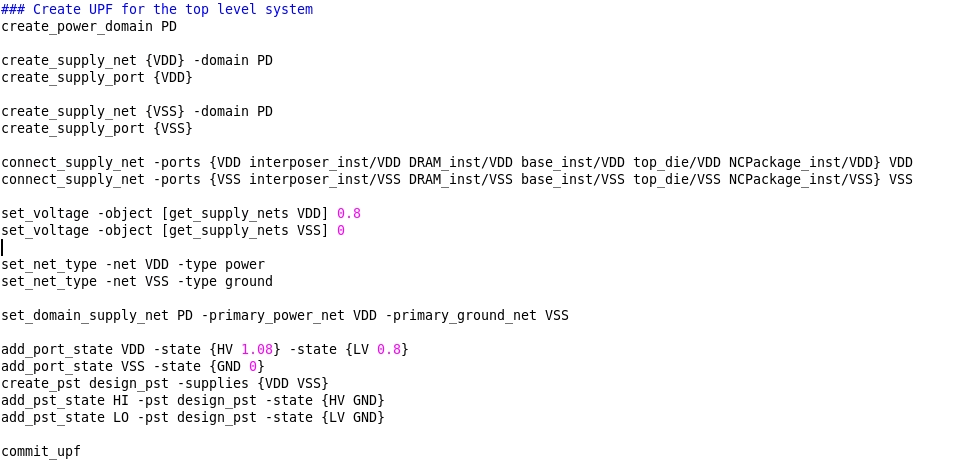

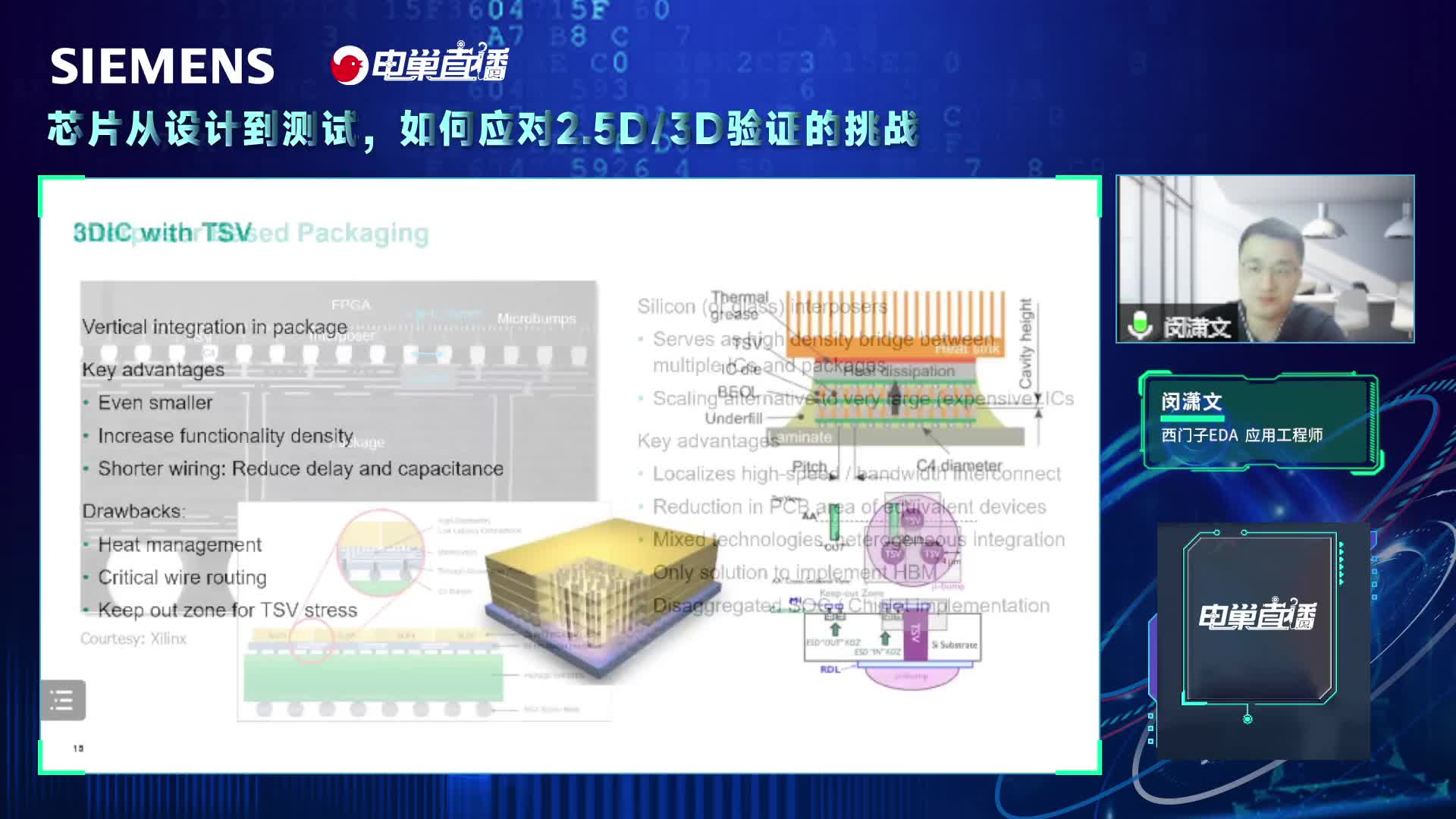

、性能更高,也因此成了新的設(shè)計(jì)主流,席卷了AI、服務(wù)器與汽車(chē)芯片等市場(chǎng)。但新的設(shè)計(jì)方案除了需要新一代的die-to-die的接口IP、2.5D/3D的封裝技術(shù)外,也需要在EDA工具與工作流上做出創(chuàng)新。 ? 西門(mén)子3D IC設(shè)計(jì)流工具 ? 為了解決3DIC集成在設(shè)計(jì)工具上

2023-11-09 00:22:00 2672

2672 3DIC Compiler協(xié)同設(shè)計(jì)與分析解決方案結(jié)合新思科技IP,加速英特爾代工EMIB技術(shù)的異構(gòu)集成 摘要: 新思科技人工智能(AI)驅(qū)動(dòng)型多裸晶芯片(Multi-die)設(shè)計(jì)參考流程已擴(kuò)展至

2024-07-09 13:42:31 1308

1308 芯片堆疊技術(shù)在SiP中應(yīng)用的非常普遍,通過(guò)芯片堆疊可以有效降低SiP基板的面積,縮小封裝體積。 芯片堆疊的主要形式有四種: 金字塔型堆疊 懸臂型堆疊 并排型堆疊 硅通孔TSV型堆疊

2020-11-27 16:39:05

和3DIC技術(shù)的發(fā)展,F(xiàn)PGA不斷在加速取代ASSP和ASIC,但這還需要更多的突破,其中最大的障礙就是互聯(lián)問(wèn)題,需在縱向架構(gòu)上“守正出奇”。

2019-09-23 07:50:27

labview中能實(shí)現(xiàn)將一個(gè)個(gè)圓堆疊成圓柱嗎? 類(lèi)似下圖

2022-05-03 15:05:25

1、什么是堆疊設(shè)計(jì)也稱(chēng)作系統(tǒng)設(shè)計(jì),根據(jù)產(chǎn)品規(guī)劃,產(chǎn)品定義的要求,為實(shí)現(xiàn)一定的功能,設(shè)計(jì)出合理可靠的具備可量產(chǎn)性的PCB及其周邊元器件擺放的一種方案。2、堆疊工程師一般由結(jié)構(gòu)工程師進(jìn)行堆疊,有些公司

2021-11-12 08:17:17

元器件內(nèi)芯片的堆疊大部分是采用金線鍵合的方式(Wire Bonding),堆疊層數(shù)可以從2~8層)。 STMICRO聲稱(chēng),誨今厚度到40μm的芯片可以從2個(gè)堆疊到8個(gè)(SRAM,Hash

2018-09-07 15:28:20

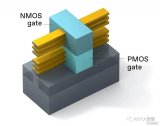

串聯(lián)堆疊,可創(chuàng)建一個(gè)溝道長(zhǎng)度為3μm的有效器件(圖1)。 圖1:將三個(gè)MOSFET串聯(lián)堆疊,可提供3μm的溝道長(zhǎng)度。 堆疊MOSFET在現(xiàn)代模擬設(shè)計(jì)中非常常見(jiàn),但并不是沒(méi)有問(wèn)題。其主要問(wèn)題是電容

2021-10-12 16:11:28

沒(méi)有讀者認(rèn)識(shí)到發(fā)生在3DIC集成中的技術(shù)進(jìn)步,他們認(rèn)為該技術(shù)只是疊層和引線鍵合,是一種后端封裝技術(shù)。而我們?cè)撊绾稳フ?b class="flag-6" style="color: red">3DIC集成技術(shù)?

2021-04-07 06:23:51

有兩個(gè)主要組成部分 - 一個(gè)是為整個(gè)3DIC設(shè)備構(gòu)建一個(gè)精確的電源模型,可以在詳細(xì)的瞬態(tài)和AC Spice分析中使用,另一個(gè)是確保模型有效地反映了非常寬的響應(yīng)范圍,包括從板級(jí)/封裝級(jí)的MHz到芯片

2017-09-25 10:14:10

各位高手。我想用labview實(shí)現(xiàn)多個(gè)2維數(shù)組的堆疊顯示,比如將10個(gè)二維數(shù)組堆疊顯示在三位空間里,且依然保留每一層的強(qiáng)度信息,效果類(lèi)似圖:

2016-10-01 14:29:49

`華爾街日?qǐng)?bào)發(fā)布文章稱(chēng),科技產(chǎn)品下一個(gè)重大突破將在芯片堆疊領(lǐng)域出現(xiàn)。Apple Watch采用了先進(jìn)的的3D芯片堆疊封裝技術(shù)作為幾乎所有日常電子產(chǎn)品最基礎(chǔ)的一個(gè)組件,微芯片正出現(xiàn)一種很有意思的現(xiàn)象

2017-11-23 08:51:12

Viterbi Compiler MegaCore Function User Guide

好東西哦。網(wǎng)上搜集,希望對(duì)你有用。

2006-03-25 15:40:49 32

32 Reed-Solomon Compiler

2006-03-25 15:42:49 26

26 Altera viterbi compiler

2006-03-25 15:45:58 18

18 MATLAB Compiler The Language of Technical Computing:This chapter describes the MATLAB Compiler

2010-02-10 11:19:36 0

0 當(dāng)大部份芯片廠商都感覺(jué)到遵循摩爾定律之途愈來(lái)愈難以為繼時(shí),3DIC成為了該產(chǎn)業(yè)尋求持續(xù)發(fā)展的出路之一。然而,整個(gè)半導(dǎo)體產(chǎn)業(yè)目前也仍在為這種必須跨越工具、制程、設(shè)計(jì)端并加

2011-06-22 08:51:53 420

420 據(jù)臺(tái)灣對(duì)外貿(mào)易發(fā)展協(xié)會(huì)(TAITRA)透露,芯片代工巨頭臺(tái)積電(TSMC)有望超過(guò)intel,在2011年底推出業(yè)內(nèi)首款采用3-D芯片堆疊技術(shù)的半導(dǎo)體芯片產(chǎn)品。

2011-07-07 09:19:07 1168

1168 芯片堆疊封裝是提高存儲(chǔ)卡類(lèi)產(chǎn)品存儲(chǔ)容量的主流技術(shù)之一,采用不同的芯片堆疊方案,可能會(huì)產(chǎn)生不同的堆疊效果。針對(duì)三種芯片堆疊的初始設(shè)計(jì)方案進(jìn)行了分析,指出了堆疊方案失

2012-01-09 16:14:14 42

42 Altera公司藉助TSMC的CoWoS整合生產(chǎn)及封裝技術(shù)開(kāi)發(fā)下一世代3DIC芯片

2012-03-23 08:31:27 1397

1397 2012年4月27日訊 - GLOBALFOUNDRIES今天宣布,在為新一代移動(dòng)和消費(fèi)電子應(yīng)用實(shí)現(xiàn)3D芯片堆疊的道路上,公司達(dá)到了一個(gè)重要的里程碑。在其位于美國(guó)紐約薩拉托加郡的Fab 8,GLOBALFOUNDRIES已開(kāi)始

2012-04-28 09:15:03 1772

1772 因應(yīng)臺(tái)積電明年積極布建?? 20nm制程產(chǎn)能并跨及3DIC封測(cè),國(guó)內(nèi)封測(cè)雙雄日月光、矽品及記憶體封測(cè)龍頭力成,下半年起也積極搶進(jìn)3DIC封測(cè),布建3DIC封測(cè)產(chǎn)能。

2012-07-30 09:08:04 1368

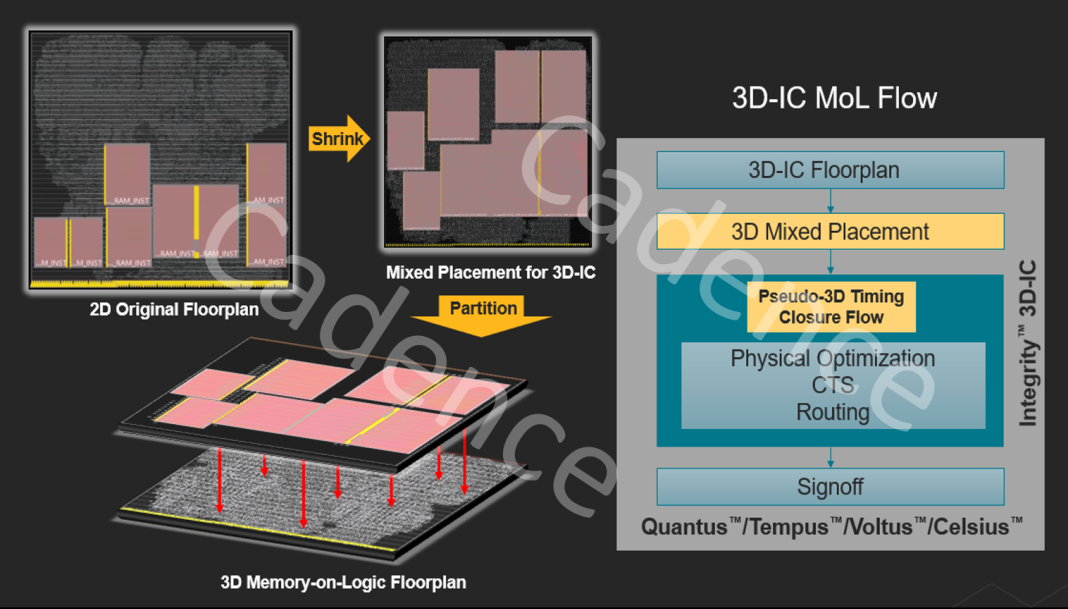

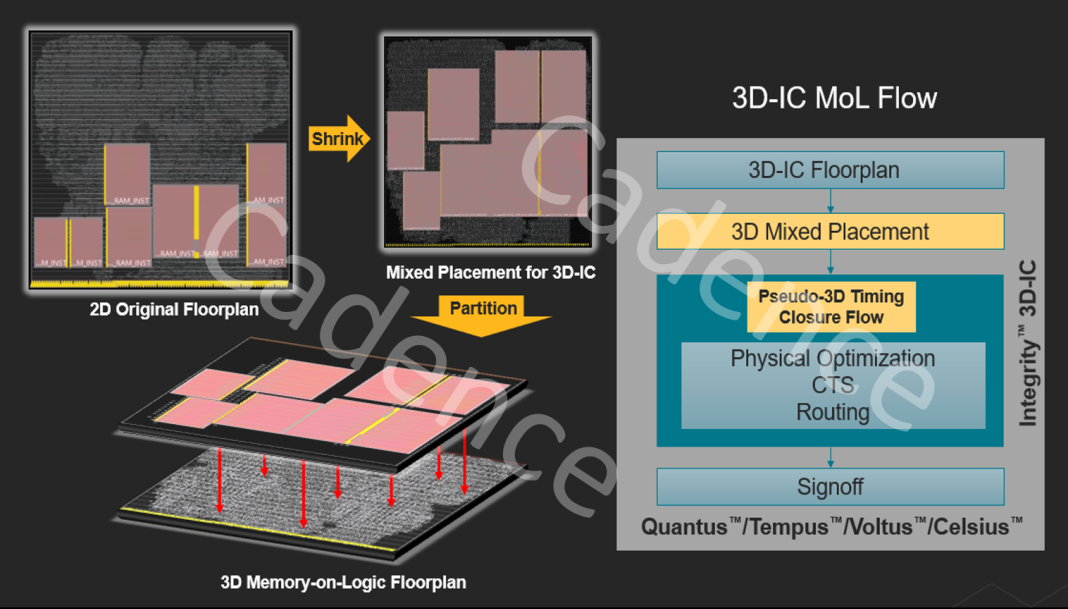

1368 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲(chǔ)器設(shè)計(jì)上進(jìn)行了驗(yàn)證 ,可實(shí)現(xiàn)多塊模的整合。它將臺(tái)積電的3D堆疊技術(shù)和Cadence?3D-IC解決方案相結(jié)合,包括了集成的設(shè)計(jì)工具、靈活的實(shí)現(xiàn)平臺(tái),以及最終的時(shí)序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1717

1717 TCL圖紙PDP42U3A_DIC

2017-02-28 22:21:46 2

2 在不同的芯片或技術(shù)組合中,TSV技術(shù)還能提供更高水平的靈活度,例如采用45奈米制程的數(shù)字芯片中的芯片至芯片堆棧,以及在模擬晶圓(例如180nm)中,微機(jī)電(MEMS)組件或光傳感器和光電二極管數(shù)組的堆棧,這只是其中的幾個(gè)例子。

2017-04-26 11:34:40 4613

4613 3D IC- 將3D模塊和內(nèi)插器集成能成為產(chǎn)業(yè)潮流,這就是最大的原因。當(dāng)前,一個(gè)流行的應(yīng)用案例是將高帶寬存儲(chǔ)器與處理器并排結(jié)合在一起,在DRAM堆棧和主存儲(chǔ)器之間直接通過(guò)低阻抗/高度并行連接實(shí)現(xiàn)更高帶寬的通信。

2017-09-22 17:26:50 1580

1580 來(lái)縮減晶方尺寸,同時(shí)也能使用先進(jìn)的封裝技術(shù)來(lái)實(shí)現(xiàn)系統(tǒng)小型化。 3DIC成為縮小傳感器IC新解方 對(duì)于更高系統(tǒng)整合度的需求持續(xù)增加,這不只促使傳統(tǒng)的組裝服務(wù)供貨商,也推動(dòng)半導(dǎo)體公司開(kāi)發(fā)更創(chuàng)新和更先進(jìn)的封裝技術(shù)。 最具前景且

2017-11-22 11:26:42 3

3 在近日舉行的英特爾“架構(gòu)日”活動(dòng)中,英特爾不僅展示了基于10納米的PC、數(shù)據(jù)中心和網(wǎng)絡(luò)系統(tǒng),支持人工智能和加密加速功能的下一代“Sunny Cove”架構(gòu),還推出了業(yè)界首創(chuàng)的3D邏輯芯片封裝技術(shù)——Foveros。這一全新的3D封裝技術(shù)首次引入了3D堆疊的優(yōu)勢(shì),可實(shí)現(xiàn)在邏輯芯片上堆疊邏輯芯片。

2018-12-14 15:35:32 8854

8854 英特爾近日向業(yè)界推出了首款3D邏輯芯片封裝技術(shù)“Foveros”,據(jù)悉這是在原來(lái)的3D封裝技術(shù)第一次利用3D堆疊的優(yōu)點(diǎn)在邏輯芯片上進(jìn)行邏輯芯片堆疊。也是繼多芯片互連橋接2D封裝技術(shù)之后的又一個(gè)顛覆技術(shù)。

2018-12-14 16:16:45 3316

3316 近日,武漢新芯研發(fā)成功的三片晶圓堆疊技術(shù)備受關(guān)注。有人說(shuō),該技術(shù)在國(guó)際上都處于先進(jìn)水平,還有人說(shuō)能夠“延續(xù)”摩爾定律。既然3D芯片堆疊技術(shù)有如此大的作用,那今天芯師爺就跟大家一起揭開(kāi)它的面紗。

2018-12-31 09:14:00 34067

34067 臺(tái)積電此次揭露 3D IC 封裝技術(shù)成功,正揭開(kāi)半導(dǎo)體制程的新世代。目前業(yè)界認(rèn)為,此技術(shù)主要為是為了應(yīng)用在 5 納米以下先進(jìn)制程,并為客制化異質(zhì)芯片鋪路,當(dāng)然也更加鞏固蘋(píng)果訂單。

2019-04-22 17:09:08 3026

3026 對(duì)全新芯片堆疊技術(shù)的全面支持確保實(shí)現(xiàn)最高性能的3D-IC解決方案

2019-05-18 11:28:01 4231

4231 日前,麻省理工學(xué)院助理教授Max Shulaker在DARPA電子復(fù)興倡議(ERI)峰會(huì)上展示了一塊碳納米管+RRAM通過(guò)ILV技術(shù)堆疊的3DIC晶圓。

2019-08-05 15:08:16 3728

3728 對(duì)于我國(guó)的半導(dǎo)體行業(yè)來(lái)說(shuō),碳納米管+RRAM+ILV 3DIC是一個(gè)值得關(guān)注的領(lǐng)域。目前碳納米管+RRAM+ILV 3DIC是否能真正成為下一代標(biāo)準(zhǔn)半導(dǎo)體工藝還存在很大的不確定因素,因此在適當(dāng)

2019-09-09 17:00:42 7575

7575 困于10nm的Intel也在這方面尋找新的機(jī)會(huì),其在去年年底的“架構(gòu)日”活動(dòng)中,推出其業(yè)界首創(chuàng)的3D邏輯芯片封裝技術(shù)——Foveros,F(xiàn)overos首次引入3D堆疊的優(yōu)勢(shì),可實(shí)現(xiàn)在邏輯芯片上堆疊

2020-01-28 16:10:00 4118

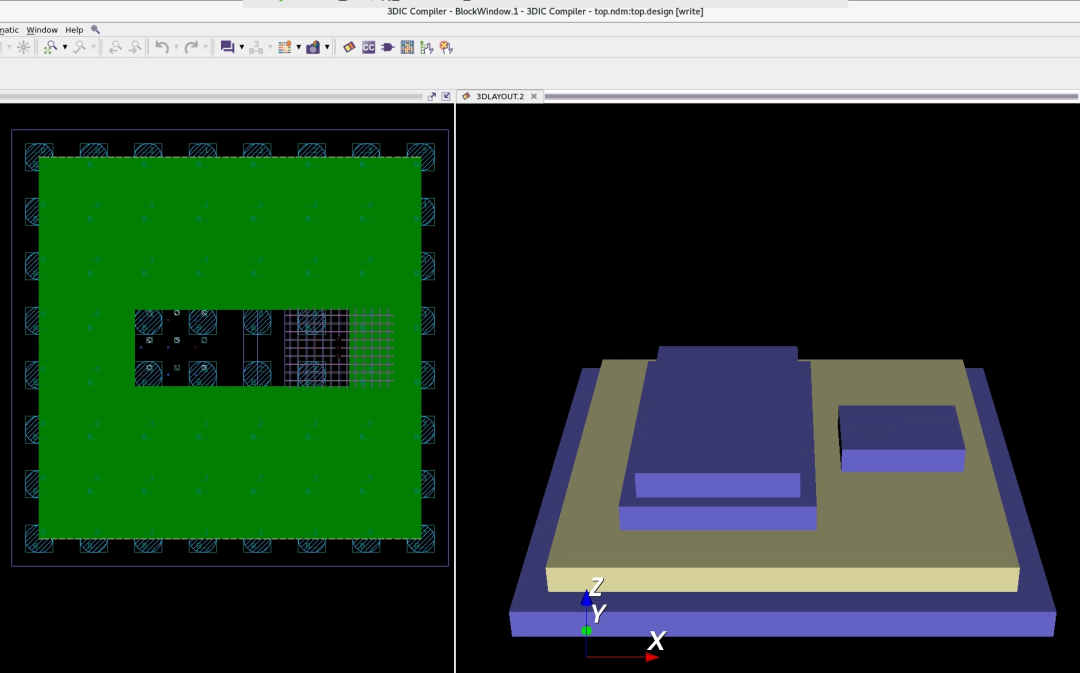

4118 新思科技的3DIC Compiler建立在一個(gè)IC設(shè)計(jì)數(shù)據(jù)模型的基礎(chǔ)上,通過(guò)更加現(xiàn)代化的3DIC結(jié)構(gòu),實(shí)現(xiàn)了容量和性能的可擴(kuò)展性。該平臺(tái)提供了一個(gè)集規(guī)劃、架構(gòu)探究、設(shè)計(jì)、實(shí)現(xiàn)、分析和signoff于一體的環(huán)境。

2020-08-28 15:43:55 3786

3786 何種方式和程序才能過(guò)渡到一種新范式以繼續(xù)滿足廣大客戶的需求。這就是GSA3DIC計(jì)劃為何如此關(guān)注強(qiáng)化客戶對(duì)該技術(shù)的優(yōu)勢(shì)和重要性認(rèn)知度的原因。”

2020-09-08 14:02:00 1947

1947 重點(diǎn) ● TSMC認(rèn)證基于新思科技3DIC Compiler統(tǒng)一平臺(tái)的CoWoS和InFO設(shè)計(jì)流程 ● 3DIC Compiler可提高先進(jìn)封裝設(shè)計(jì)生產(chǎn)率 ● 集成Ansys芯片封裝協(xié)同分析解決方案

2020-10-14 11:11:21 2814

2814 AD2009:3個(gè)半的DIC線DPM過(guò)時(shí)的數(shù)據(jù)Sheet

2021-05-14 12:28:34 8

8 隨著摩爾定律的逐漸失效,縮小芯片尺寸的挑戰(zhàn)日益艱巨。但隨著新工藝和技術(shù)接連涌現(xiàn),芯片設(shè)計(jì)規(guī)模仍在持續(xù)拓展。其中一種方式就是采用3DIC,它將硅晶圓或裸晶垂直堆疊到同一個(gè)封裝器件中,從而帶來(lái)性能、功耗

2021-06-09 17:46:17 2972

2972 芯片系統(tǒng)設(shè)計(jì)分析的統(tǒng)一平臺(tái),為客戶構(gòu)建了一個(gè)完全集成、性能卓著且易于使用的環(huán)境,提供了從開(kāi)發(fā)、設(shè)計(jì)、驗(yàn)證、信號(hào)完整性仿真、電源完整性仿真到最終簽核的3DIC全流程解決方案。 隨著芯片制造工藝不斷接近物理極限,芯片的布局設(shè)計(jì)——異構(gòu)集成的3DIC先進(jìn)

2021-08-30 13:32:23 2431

2431 隨著芯片制造工藝不斷接近物理極限,芯片的布局設(shè)計(jì)——異構(gòu)集成的3DIC先進(jìn)封裝(以下簡(jiǎn)稱(chēng)“3DIC”)已經(jīng)成為延續(xù)摩爾定律的最佳途徑之一。

2021-08-30 14:12:17 1968

1968 3DIC架構(gòu)并非新事物,但因其在性能、成本方面的優(yōu)勢(shì)及其將異構(gòu)技術(shù)和節(jié)點(diǎn)整合到單一封裝中的能力,這種架構(gòu)越來(lái)越受歡迎。隨著開(kāi)發(fā)者希望突破傳統(tǒng)二維平面IC架構(gòu)的復(fù)雜度和密度限制,3D集成提供了引入更多

2021-09-03 10:17:53 7383

7383 H3CS3100-SIStack堆疊的典型配置(安徽理士電源技術(shù))-H3CS3100-SIStack堆疊的典型配置? ? ? ? ? ? ? ?

2021-09-15 12:09:09 2

2 盛合晶微原名中芯長(zhǎng)電半導(dǎo)體有限公司,是中國(guó)大陸第一家致力于12英寸中段凸塊和硅片級(jí)先進(jìn)封裝的企業(yè),也是大陸最早宣布以3DIC多芯片集成封裝為發(fā)展方向的企業(yè)。

2021-10-11 14:14:51 2506

2506 新思科技3DIC Compiler是統(tǒng)一的多裸晶芯片設(shè)計(jì)實(shí)現(xiàn)平臺(tái),無(wú)縫集成了基于臺(tái)積公司3DFabric技術(shù)的設(shè)計(jì)方法,提供完整的“探索到簽核”的設(shè)計(jì)平臺(tái)

2021-11-01 16:29:14 703

703 雙方拓展戰(zhàn)略合作,提供全面的3D系統(tǒng)集成功能,支持在單一封裝中集成數(shù)千億個(gè)晶體管 新思科技3DIC Compiler是統(tǒng)一的多裸晶芯片設(shè)計(jì)實(shí)現(xiàn)平臺(tái),無(wú)縫集成了基于臺(tái)積公司3DFabric技術(shù)

2021-11-05 15:17:19 6382

6382 新思科技和三星晶圓廠(以下簡(jiǎn)稱(chēng)為“三星”)著力提升先進(jìn)節(jié)點(diǎn)和多裸晶芯片封裝的創(chuàng)新和效率,滿足HPC、AI、汽車(chē)和5G等應(yīng)用的大量需求

2021-12-08 11:08:36 1713

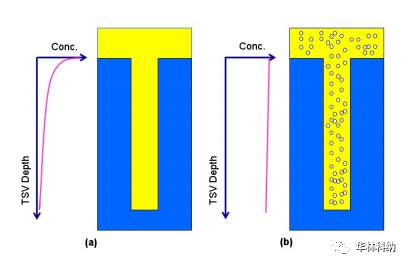

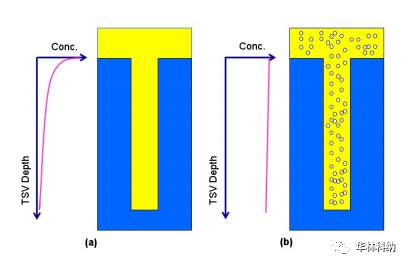

1713 直通硅通孔(TSV)器件是3D芯片封裝的關(guān)鍵推動(dòng)者,可提高封裝密度和器件性能。要實(shí)現(xiàn)3DIC對(duì)下一代器件的優(yōu)勢(shì),TSV縮放至關(guān)重要。

2022-04-12 15:32:46 1788

1788

,華為這次公布的芯片堆疊專(zhuān)利是2019年10月3日申請(qǐng)的,涉及電子技術(shù)領(lǐng)域,用于解決如何將多個(gè)副芯片堆疊單元可靠的鍵合在同一主芯片堆疊單元上的問(wèn)題。 在美國(guó)將華為列入芯片制裁名單后,華為的芯片技術(shù)遭到了前所未有的限制,許多全球知名的半導(dǎo)體企

2022-05-07 15:59:43 101144

101144 電子發(fā)燒友網(wǎng)報(bào)道(文/黃山明)近日,華為密集公布了多項(xiàng)技術(shù)專(zhuān)利,其中引人注意的是華為再次公布了兩項(xiàng)與芯片堆疊有關(guān)的專(zhuān)利。為何說(shuō)再次,因?yàn)榫驮谝粋€(gè)月前,華為同樣公開(kāi)了“一種芯片堆疊封裝及終端設(shè)備”的專(zhuān)利。多項(xiàng)與芯片堆疊相關(guān)專(zhuān)利的公開(kāi),或許也揭露了華為未來(lái)在芯片技術(shù)上的一個(gè)發(fā)展方向。

2022-05-09 09:50:20 6384

6384 堆疊技術(shù)也可以叫做3D堆疊技術(shù),是利用堆疊技術(shù)或通過(guò)互連和其他微加工技術(shù)在芯片或結(jié)構(gòu)的Z軸方向上形成三維集成,信號(hào)連接以及晶圓級(jí),芯片級(jí)和硅蓋封裝具有不同的功能,針對(duì)包裝和可靠性技術(shù)的三維堆疊處理技術(shù)。

2022-05-10 15:58:13 4946

4946

“芯片堆疊”技術(shù)近段時(shí)間經(jīng)常聽(tīng)到,在前段時(shí)間蘋(píng)果舉行線上發(fā)布會(huì)時(shí),推出了號(hào)稱(chēng)“史上最強(qiáng)”的Apple M1 ultra,這就是一種采用堆疊思路設(shè)計(jì)的芯片。

2022-08-11 15:39:02 10366

10366

目前有多種基于 3D 堆疊方法, 主要包括: 芯片與芯片的堆疊( D2D) 、芯片與圓片的堆疊( D2W ) 以及圓片與圓片的堆疊( W2W) 。

2022-11-01 09:52:51 2487

2487 ? 芯和半導(dǎo)體2.5D/3D多芯片Chiplets解決方案

2022-11-24 16:54:08 1284

1284 在沒(méi)有bump library cells的情況下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速實(shí)現(xiàn)Bump Planning,流程包括: 定義bump

2022-11-24 16:58:19 2112

2112 目前階段開(kāi)始有同構(gòu)集成。國(guó)際上已經(jīng)有異構(gòu)集成CPU+GPU+NPU的Chiplet,其他功能芯片則采用次先進(jìn)工藝制程的芯粒,感存算一體屬于3DIC的Chiplet這樣的方案可以靈活堆出算力高達(dá)200tops。

2023-02-14 15:00:00 3269

3269 HPC、AI、數(shù)據(jù)中心以及汽車(chē)自動(dòng)化等應(yīng)用對(duì)于高效能和高性能算力需求持續(xù)增長(zhǎng),單芯片系統(tǒng)實(shí)現(xiàn)方案從設(shè)計(jì)、實(shí)現(xiàn)、生產(chǎn)制造、可靠性等各個(gè)方面都遇到了嚴(yán)峻的技術(shù)挑戰(zhàn)。

2023-02-15 16:01:39 4478

4478 的“存儲(chǔ)墻”、“功耗墻”問(wèn)題。存算一體將存儲(chǔ)與計(jì)算有機(jī)融合以其巨大的能效比提升潛力,有望成為數(shù)字經(jīng)濟(jì)時(shí)代的先進(jìn)生產(chǎn)力。存算一體芯片設(shè)計(jì)迭代和投產(chǎn)的效率至關(guān)重要,如何能夠設(shè)計(jì)出更低損耗、更低噪聲、更低能耗,并符合信號(hào)完整性、電源完整性指標(biāo)性能的存算一體芯片,從而提高存算一體芯片的設(shè)計(jì)效率呢?

2023-02-24 09:34:28 8040

8040 M3T-NC30WA V.5.45 C Compiler 用戶手冊(cè) (C Compiler Package for M16C Series and R8C Family)

2023-04-18 18:36:56 0

0 R32C/100 Series C Compiler Package V.1.02 C Compiler 用戶手冊(cè)

2023-04-19 19:24:26 0

0 M3T-NC308WA V.5.42 C Compiler 用戶手冊(cè) (C Compiler Package for M32C Series)

2023-04-19 19:25:01 0

0 ?? 原文標(biāo)題:誰(shuí)說(shuō)3DIC系統(tǒng)設(shè)計(jì)難?最佳PPAC目標(biāo)輕松實(shí)現(xiàn) 文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

2023-04-21 02:05:04 851

851

? ? 原文標(biāo)題:仿真分析:3DIC全流程解決方案的第一步 文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

2023-05-11 20:16:30 1096

1096

? ? 原文標(biāo)題:本周五|仿真分析:3DIC全流程解決方案的第一步 文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

2023-05-11 20:16:38 891

891

原文標(biāo)題:1+1>2?3DIC+Metis助力實(shí)現(xiàn)協(xié)同設(shè)計(jì)和仿真分析 文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

2023-05-11 20:16:40 806

806

原文標(biāo)題:下周五|1+1>2?3DIC+Metis助力實(shí)現(xiàn)協(xié)同設(shè)計(jì)和仿真分析 文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

2023-05-11 20:17:25 774

774

做到多顆芯片靈活堆疊,芯片設(shè)計(jì)團(tuán)隊(duì)要實(shí)現(xiàn)質(zhì)量最佳、滿足工期要求、具有成本效益的設(shè)計(jì),面臨著如何建立正確的3D-IC設(shè)計(jì)實(shí)現(xiàn)流程和如何實(shí)現(xiàn)設(shè)計(jì)數(shù)據(jù)&項(xiàng)目的高效管理的

2022-07-24 16:25:41 1590

1590

原文標(biāo)題:Design Compiler再進(jìn)化:助力開(kāi)發(fā)者更快實(shí)現(xiàn)終極KPI 文章出處:【微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

2023-06-26 18:40:02 681

681

3DIC設(shè)計(jì)的重要性日益凸顯。當(dāng)今市場(chǎng)對(duì)AI應(yīng)用的需求在不斷增加,而摩爾定律的步伐卻在放緩,這使得芯片開(kāi)發(fā)者不得不尋求其他類(lèi)型的芯片架構(gòu),以滿足消費(fèi)者和領(lǐng)先服務(wù)提供商的預(yù)期。3DIC設(shè)計(jì)并不是簡(jiǎn)單

2023-06-27 17:35:01 2230

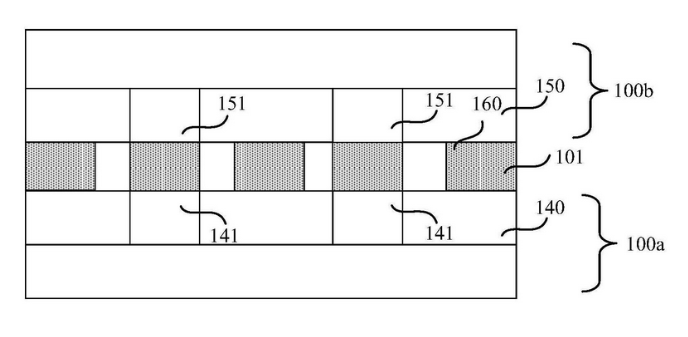

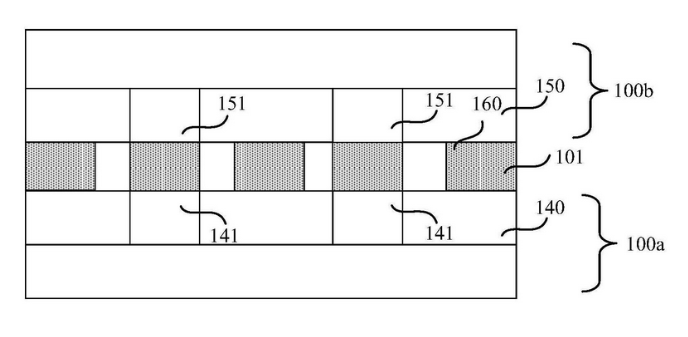

2230 芯片技術(shù)領(lǐng)域的應(yīng)用概要,用于簡(jiǎn)化芯片堆疊結(jié)構(gòu)及其形成方法、芯片封裝結(jié)構(gòu)、電子設(shè)備、芯片堆棧結(jié)構(gòu)的制造技術(shù)。該芯片的堆疊結(jié)構(gòu)至少包括兩個(gè)堆疊的芯片,每一個(gè)芯片包括電線層,電線層設(shè)有電具組。

2023-08-09 10:13:42 2753

2753

新思科技經(jīng)認(rèn)證的多裸晶芯片系統(tǒng)設(shè)計(jì)參考流程和安全的Die-to-Die IP解決方案,加速了三星SF 5/4/3工藝和I-Cube及X-Cube技術(shù)的設(shè)計(jì)和流片成功。 新思科技3DIC

2023-09-14 09:38:28 1999

1999 長(zhǎng)期以來(lái),個(gè)人計(jì)算機(jī)都可以選擇增加內(nèi)存,以便提高處理超大應(yīng)用和大數(shù)據(jù)量工作的速度。由于3D芯片堆疊的出現(xiàn),CPU芯粒也有了這個(gè)選擇,但如果你想打造一臺(tái)更具魅力的計(jì)算機(jī),那么訂購(gòu)一款有超大緩存的處理器可能是正確的選擇。

2023-10-15 10:24:23 2733

2733

作為全球領(lǐng)先的互聯(lián)產(chǎn)品和解決方案公司,奇異摩爾期待以自身 Chiplet 互聯(lián)芯粒、網(wǎng)絡(luò)加速芯粒產(chǎn)品及全鏈路解決方案,結(jié)合智原全面的先進(jìn)封裝一站式服務(wù),通力協(xié)作,深耕 2.5D interposer 與 3DIC 領(lǐng)域,攜手開(kāi)啟 Chiplet 時(shí)代的新篇章。

2023-11-12 10:06:25 1900

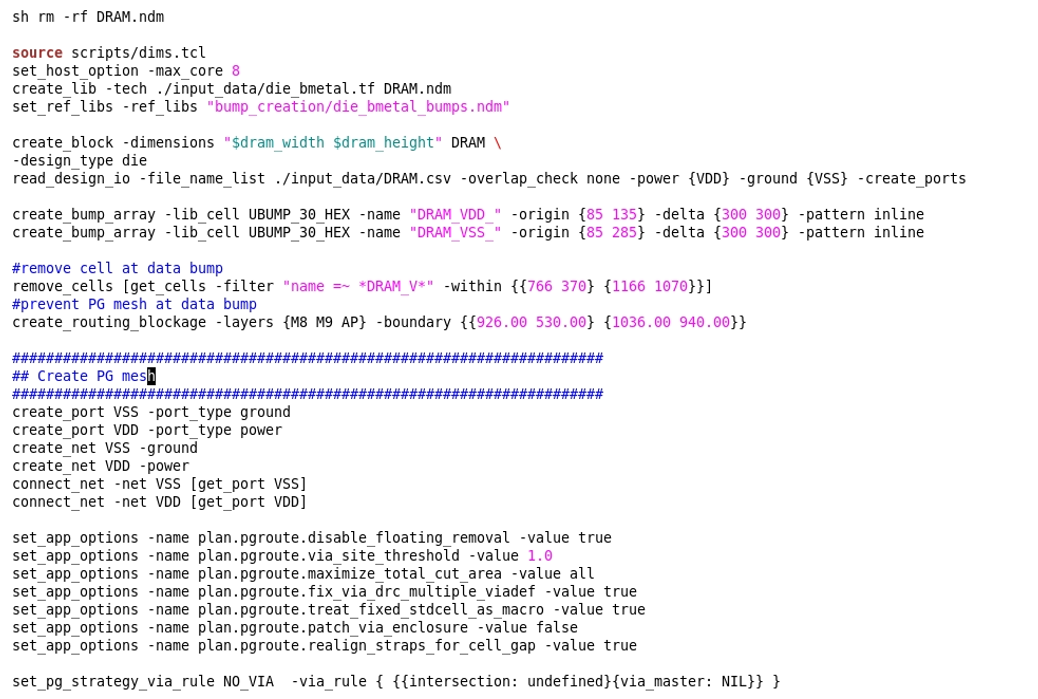

1900 3D-IC 設(shè)計(jì)之 Memory-on-Logic 堆疊實(shí)現(xiàn)流程

2023-12-01 16:53:37 1455

1455

TSV是2.5D和3D集成電路封裝技術(shù)中的關(guān)鍵實(shí)現(xiàn)技術(shù)。半導(dǎo)體行業(yè)一直在使用HBM技術(shù)將DRAM封裝在3DIC中。

2023-11-27 11:40:20 1762

1762

利用Multi-Die系統(tǒng)能實(shí)現(xiàn)異構(gòu)集成,并且利用較小Chiplet實(shí)現(xiàn)更高良率,更小的外形尺寸和緊湊的封裝,降低系統(tǒng)的功耗和成本。Ansys半導(dǎo)體產(chǎn)品研發(fā)主管Murat Becer指出:“3DIC正在經(jīng)歷爆炸性增長(zhǎng),我們預(yù)計(jì)今年3DIC設(shè)計(jì)的數(shù)量將是去年的3倍左右。”

2023-11-29 16:35:48 1360

1360 新思科技3DIC Compiler集成了3Dblox 2.0標(biāo)準(zhǔn),可用于異構(gòu)集成和“從架構(gòu)探索到簽核”的完整解決方案。

2024-01-12 13:40:50 973

973

什么是交換機(jī)堆疊?有哪些設(shè)備可以堆疊?如何建立堆疊? 交換機(jī)堆疊是指將多個(gè)交換機(jī)通過(guò)特定的方法連接在一起,形成一個(gè)邏輯上的單一設(shè)備。堆疊可以實(shí)現(xiàn)多交換機(jī)的集中管理和統(tǒng)一配置,提供更高的可靠性和性能

2024-02-04 11:21:47 3698

3698 ; 新思科技廣泛的高質(zhì)量 IP組合降低集成風(fēng)險(xiǎn)并加快產(chǎn)品上市時(shí)間,為采用Intel 18A 工藝的開(kāi)發(fā)者提供了競(jìng)爭(zhēng)優(yōu)勢(shì); 新思科技 3DIC Compiler提供了覆蓋架構(gòu)探索到簽收的統(tǒng)一平臺(tái),可實(shí)現(xiàn)采用

2024-03-05 10:16:59 1014

1014 報(bào)道指出,此次訂單主要由蘋(píng)果的功率放大器供應(yīng)商威訊聯(lián)合半導(dǎo)體(Qorvo)下達(dá)。威訊方面主要負(fù)責(zé)設(shè)計(jì)iPhone天線組件,并集成新芯片以及提供Qorvo功率放大器。這些新芯片采用聯(lián)電的3DIC先進(jìn)工藝進(jìn)行制造。

2024-04-02 11:26:16 1071

1071 套件賦能可投產(chǎn)的數(shù)字和模擬設(shè)計(jì)流程能夠針對(duì)臺(tái)積公司N3/N3P和N2工藝,助力實(shí)現(xiàn)芯片設(shè)計(jì)成功,并加速模擬設(shè)計(jì)遷移。 新思科技物理驗(yàn)證解決方案已獲得臺(tái)積公司N3P和N2工藝技術(shù)認(rèn)證,可加速全芯片物理簽核。 新思科技3DIC Compiler和光子集成電路(PIC)解決方案與臺(tái)

2024-05-11 11:03:49 695

695

新思科技EDA事業(yè)部戰(zhàn)略與產(chǎn)品管理副總裁Sanjay Bali表示:“新思科技在可投產(chǎn)的EDA流程和支持3Dblox標(biāo)準(zhǔn)的3DIC Compiler光子集成方面的先進(jìn)成果,結(jié)合我們廣泛的IP產(chǎn)品組合,使得我們與臺(tái)積公司能夠助力開(kāi)發(fā)者基于臺(tái)積公司先進(jìn)工藝加速下一代芯片設(shè)計(jì)創(chuàng)新。

2024-05-11 16:25:42 1016

1016 提供了一個(gè)統(tǒng)一的協(xié)同設(shè)計(jì)與分析解決方案,通過(guò)新思科技3DIC Compiler加速?gòu)?b class="flag-6" style="color: red">芯片到系統(tǒng)的各個(gè)階段的多裸晶芯片設(shè)計(jì)的探索和開(kāi)發(fā)。此外,新思科技3DSO.ai與新思科技3DIC Compiler原生集成,實(shí)現(xiàn)了信號(hào)、電源和熱完整性的優(yōu)化,極大程度地提高了生產(chǎn)力并優(yōu)化系統(tǒng)性能。

2024-07-16 09:42:16 1291

1291 新思科技宣布推出面向英特爾代工EMIB先進(jìn)封裝技術(shù)的可量產(chǎn)多裸晶芯片設(shè)計(jì)參考流程,該流程采用了Synopsys.ai EDA全面解決方案和新思科技IP。此外,新思科技3DSO.ai與新思科技3DIC

2024-08-12 09:50:30 1133

1133 電子發(fā)燒友網(wǎng)站提供《BQ77915的堆疊實(shí)現(xiàn).pdf》資料免費(fèi)下載

2024-09-24 10:51:24 2

2 (InFO) 封裝這樣的 3D 扇出封裝方法,則更側(cè)重于手機(jī)等大規(guī)模消費(fèi)應(yīng)用。此外,所有主流設(shè)計(jì)公司、晶圓代工廠和封測(cè)代工廠 (OSAT) 都在投資新一代技術(shù)——使用硅通孔 (TSV) 和混合鍵合的真正裸片堆疊。

2025-02-20 11:36:56 1272

1272

在當(dāng)下3DIC技術(shù)作為提升芯片性能和集成度的重要路徑,正面臨著諸多挑戰(zhàn),尤其是Signoff環(huán)節(jié)的復(fù)雜性問(wèn)題尤為突出。此前,6月6日至8日,由中國(guó)科學(xué)院空天信息創(chuàng)新研究院主辦的“第四屆電子與信息前沿

2025-06-12 14:22:07 1025

1025 此前,2025年6月20日-22日,全球半導(dǎo)體行業(yè)盛會(huì)——世界半導(dǎo)體博覽會(huì)在南京國(guó)際博覽中心盛大開(kāi)幕。行芯科技受邀參與EDA/IP核產(chǎn)業(yè)發(fā)展高峰論壇,面對(duì)摩爾定律破局關(guān)鍵的3DIC技術(shù),作為“守門(mén)員

2025-06-26 15:05:24 1076

1076 在剛剛于無(wú)錫圓滿落幕的第三屆芯粒開(kāi)發(fā)者大會(huì)——這場(chǎng)匯聚全球頂尖芯片企業(yè)、科研機(jī)構(gòu)及產(chǎn)業(yè)鏈專(zhuān)家的盛會(huì)上,行芯科技作為國(guó)內(nèi)Signoff領(lǐng)域的領(lǐng)軍企業(yè),受邀發(fā)表了主題演講《面向3DIC的Signoff挑戰(zhàn)與行芯創(chuàng)新性策略》,為行業(yè)破解3DIC Signoff難題提供了全新路徑。

2025-07-18 10:22:17 840

840 半導(dǎo)體產(chǎn)業(yè)正在駛?cè)隒hiplet時(shí)代。多芯片合封雖顯著釋放性能紅利,卻讓成本控制與良率測(cè)試成為新的挑戰(zhàn):一顆芯片失效即可導(dǎo)致整顆先進(jìn)封裝報(bào)廢,傳統(tǒng)“測(cè)后補(bǔ)救”模式在時(shí)間與資金兩端均顯吃力。普迪飛

2025-08-19 13:45:41 783

783

隨著3D堆疊方案憑借低功耗、高帶寬特性,有望成為下一代移動(dòng)端高端熱門(mén)技術(shù)。芯動(dòng)科技瞄準(zhǔn)3DIC市場(chǎng),與全球領(lǐng)先的存算一體芯片企業(yè)知存科技達(dá)成深度合作,正式量產(chǎn)面向Face2Face鍵合(F2F)系列高速接口IP解決方案。

2025-08-27 17:05:25 1142

1142 9月9日,半導(dǎo)體行業(yè)迎來(lái)重磅消息,3DIC 先進(jìn)封裝制造聯(lián)盟(3DIC Advanced Manufacturing Alliance,簡(jiǎn)稱(chēng) 3DIC AMA)正式宣告成立,該聯(lián)盟由行業(yè)巨頭臺(tái)積電

2025-09-15 17:30:17 836

836 Socionext Inc.(以下簡(jiǎn)稱(chēng)“Socionext”)宣布,其3DIC設(shè)計(jì)現(xiàn)已支持面向消費(fèi)電子、人工智能(AI)和高性能計(jì)算(HPC)數(shù)據(jù)中心等多種應(yīng)用。通過(guò)結(jié)合涵蓋Chiplet、2.5D

2025-09-24 11:09:54 2350

2350

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論