在最近舉辦的GSA存儲大會上,芯片制造業的四大聯盟組織-IMEC, ITRI, Sematech以及SEMI都展示了他們各自在基于TSV的3D芯片技術方面的最新進展

2011-04-14 18:38:31 7492

7492

據IC Insights發布的最新2020 McClean報告顯示,半導體行業研發的投入將在2024年出現明顯成效包括轉向EUV光刻,低于3納米制程技術,3D芯片堆疊技術和先進封裝在內的技術挑戰有望

2020-01-31 09:20:34 7042

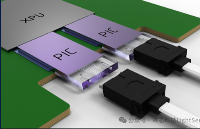

7042 3D堆疊、多芯片封裝大家想必都不陌生了,這年頭制造工藝已經沒有太多噱頭,有時甚至性能提升也有限,廠商只好從架構上入手。像蘋果的Ultra?Fusion拼接、Graphcore的3D WoW,都是在

2022-04-13 01:06:00 7527

7527 視為堆疊邏輯與內存、3D NAND,甚至可能在高帶寬存儲(HBM)中的多層DRAM堆疊的關鍵技術。垂直堆疊使得芯片制造商能夠將互連間距從35μm的銅微凸點提升到10μm甚至更小。

2025-05-22 11:24:18 1405

1405

20nm硅片技術可支持高密度設計和高功效系統的同時實現。它可以在單片管芯以及多芯片3D硅片器件中集成規模更大、更復雜的硅片功能。 多種系統功能,一種架構 您經過優化的數字系

2012-09-07 10:43:09 730

730 電子發燒友網訊【編譯/Triquinne】 :賽靈思公司(Xilinx)今天發布公告,宣布其20nm產品系列發展戰略,包括下一代8系列All Programmable FPGA以及第二代3D IC和SoC。20nm產品系列建立在業經驗證

2012-11-14 15:32:29 1450

1450 20nm能讓我們超越什么?對于像賽靈思(Xilinx)這樣剛剛在28nm上花了巨資量產的公司,為什么又要去追20nm呢?20nm FPGA會帶給我們什么樣的科技進步?20nm FPGA背后到底蘊藏了哪些巨大能量?

2013-01-22 08:36:34 1820

1820 臺積電(TSMC)的高管對即將來臨的20nm芯片生產與銷售信心滿滿,臺積電CEO張忠謀上周就曾做過一個預測,他說最新的20nm工藝芯片2014年的成績會比先前28nm芯片頭兩年賣得還要好。

2013-01-23 08:57:45 1495

1495 臺積電的20nm芯片生產設施或將與本月20日開始安裝,有可能在今年第2季度末期拿出20nm SoC產品樣品,正常情況下將在2014年進入量產。

2013-04-07 09:41:26 1214

1214 Altera公司今天宣布,公司展出了業界首款具有32-Gbps收發器功能的可編程器件,在收發器技術上樹立了另一關鍵里程碑。此次展示使用了基于TSMC 20SoC工藝技術的20 nm器件,該成果證實了20nm硅片的性能。

2013-04-09 10:38:43 2988

2988 截至2013年會計年度,賽靈思不僅囊括七成28納米FPGA的Design Win,整體市占率也沖破50.9%。Robert表示,賽靈思表現亮眼的關鍵因素在于制程往往領先對手一個世代,今年在搶先跨入20納米、3D IC制程的優勢帶動下,領導地位將更趨穩固。

2013-05-29 10:11:35 1324

1324 Mentor CEO認為:進入20nm、14/16nm及10nm工藝時代后,摩爾定律可能會失效,每個晶體管成本每年的下降速度不到30%,這導致企業面臨的成本挑戰會更加嚴峻。

2013-09-20 10:06:00 2125

2125 All Programmable FPGA、SoC和3D IC的全球領先企業賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX) )今天宣布推出其20nm All Programmable UltraScale?產品系列,并提供相關產品技術文檔和Vivado?設計套件支持。

2013-12-10 22:50:33 1372

1372 有消息稱,這款蘋果A8芯片將會采用臺積電的20nm制程工藝。出于貨源穩定性的考慮,不會采用年底更為超前的16nm。盡管16nm的芯片會在明年正式量產,但是產能和技術上仍不慎穩定。

2013-12-16 08:56:43 2381

2381 蘋果A7處理器推出后,高通也迅速推出了64位移動處理器驍龍410,由于該處理器定位中低端,因此,它的風頭反被NVIDIA推出的Tegra K1所搶去。對此,外媒傳來消息稱,高通將在2014年下半年推出高端產品驍龍810,其將采用20nm工藝制造,GPU也升級為Adreno 430。

2014-01-23 09:35:18 3038

3038 據報道AMD明年代號“北極群島”的GPU家族將完全跳過有問題的20nm工藝節點,北極群島系列GPU將直接采用14nm FinFE工藝生產,希望實現更高的效率。

2015-04-24 11:15:50 1352

1352 在歷經16nm/14nm閘極成本持續增加后,可望在10nm時降低。雖然IBS并未預期工藝技術停止微縮,但預計試錯成本(cost penalty)將出現在采用20nm bulk CMOS HKMG和16/14nm FinFET之際。

2015-06-23 10:39:27 1563

1563 半導體協會理事長盧超群指出,未來半導體將要做3D垂直堆疊,全球半導體產業未來會朝向類摩爾定律成長。

2016-06-10 00:14:00 2696

2696 著稱,三星為了趕超臺積電選擇直接跳過20nm工藝而直接開發14nmFinFET工藝,臺積電雖然首先開發出16nm工藝不過由于能效不佳甚至不如20nm工藝只好進行改進引入FinFET工藝,就此三星成功實現了領先。

2017-03-02 01:04:49 2107

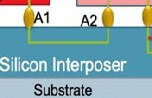

2107 先進封裝從MCM發展到2.5D/3D堆疊封裝,目前發展最快的制造商是TSMC。TSMC從Foundry端延伸入2.5D/3D先進封裝,稱為3D Fabric。近十年來TSMC的2.5D先進封裝技術

2022-10-26 10:21:37 5940

5940 3D堆疊像素探測器芯片技術詳解

2024-11-01 11:08:07 4435

4435

3D堆疊將不斷發展,以實現更復雜和集成的設備——從平面到立方體

2024-09-19 18:27:41 2348

2348

3D閃存有著更大容量、更低成本和更高性能的優勢,本文介紹了3D閃存的制造工藝與挑戰。

2025-04-08 14:38:39 2048

2048

此前曾經報道ARM的下一代架構Cortex A15將提供雙倍于Cortex A9的性能,產品采用TSMC的28nm工藝,不過就在今天ARM和TSMC聯合宣布已經成功流片20nm ARM Cortex-A15 MPCore芯片。

2011-10-19 09:10:40 1873

1873 什么是3D圖形芯片?3D圖像生成算法的原理是什么?

2021-06-04 06:29:06

快速制造優勢。采用3D打印技術制造的原型產品大大縮短了研發和實驗時間,加快了企業研發生產進度,同時還避免了許多創意想法受限于傳統制造工藝無法實現的窘境。在這方面,研發了中國首臺自產噴頭砂型3D打印機風暴

2018-08-11 11:25:58

浩辰3D作為由浩辰CAD公司研發的高端3D設計軟件,能夠提供更完備的2D+3D一體化解決方案,基于人們的實際應用需求,幫助設計師更智能高效地進行創新設計,以高精確、強交互的設計數據來銜接工藝制造等

2021-06-04 14:11:29

10nm、7nm等到底是指什么?芯片工藝從目前的7nm升級到3nm后,到底有多大提升呢?

2021-06-18 06:43:04

正在從二維走向三維世界——芯片設計、芯片封裝等環節都在向3D結構靠攏。晶體管架構發生了改變當先進工藝從28nm向22nm發展的過程中,晶體管的結構發生了變化——傳統的平面型晶體管技術(包括體硅技術

2020-03-19 14:04:57

功耗。 o 新一代布線技術支持快速時序收斂。 o 增強型邏輯基礎架構最大化性能和器件的利用率。 其他系列特有的功能包括: o 多達440萬個邏輯單元、采用20nm工藝以及第二代3D IC技術

2013-12-17 11:18:00

。

叉行片:連接并集成兩個晶體管NFET和PFET,它們之間同時被放置一層不到10nm的絕緣膜,放置缺陷的發生。

CFET:屬于下一代晶體管結構,采用3D堆疊式GAAFET,面積可縮小至原來的50

2025-09-15 14:50:58

三星電子近日在國際學會“IEDM 2015”上就20nm工藝的DRAM開發發表了演講。演講中稱,三星此次試制出了20nm工藝的DRAM,并表示可以“采用同樣的方法,達到10nm工藝”。 國際電子器件

2015-12-14 13:45:01

:“BeSang創立于三年前,是家專門做3D IC技術的公司, BeSang即將實現單芯片3D IC工藝的商業化應用。通過在邏輯器件頂部使用低溫工藝和縱向存儲設備,每個晶圓可以制造更多的裸片,這就是裸片

2008-08-18 16:37:37

如何使用新款TI DLP Pico芯片組實現高精度臺式3D打印和便攜式3D掃描?

2021-06-02 06:34:48

達到300億美元的規模,2014年更可望成長10%-20%。對此,趙甘鳴預測,2014年將是晶圓代工產業20納米技術與3D NAND起飛量產的一年,3D存儲器的發展將導致芯片代工企業的主要支出由光刻向

2014-07-12 17:17:04

像我們看到的Xilinx 28nm Virtex 7 28mm或者20nm 的UltraScale啊。nm在FPGA里面具體指什么呢

2018-10-08 17:18:18

本帖最后由 eehome 于 2013-1-5 10:10 編輯

高清圖詳解英特爾最新22nm 3D晶體管

2012-08-05 21:48:28

臺積電又跳過22nm工藝 改而直上20nm

為了在競爭激烈的半導體代工行業中提供最先進的制造技術,臺積電已經決定跳過22nm工藝的研

2010-04-15 09:52:16 1210

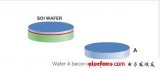

1210 單片型3D技術實現的關鍵在于如何將各層功能單元轉換到單片3D堆疊結構之中去,其采用的方法非常類似于Soitec在制作SOI晶圓時所采用的SMARTCUT技術

2011-05-04 11:27:21 2198

2198

據臺灣對外貿易發展協會(TAITRA)透露,芯片代工巨頭臺積電(TSMC)有望超過intel,在2011年底推出業內首款采用3-D芯片堆疊技術的半導體芯片產品。

2011-07-07 09:19:07 1168

1168 GlobalFoundries日前試產了20nm測試芯片,該芯片采用Cadence,Magma,Mentor Graphics和Synopsys的設計工具。此次試制的測試芯片使用了雙重圖形(Double Patterning),每家EDA合作伙伴都提供了大量的布局

2011-09-01 09:53:11 1660

1660 Sondrel公司近日將在IIC-China 2012現場展示20nm的模擬和數碼設計技術。Sondrel在歐洲不同國家,以及以色列和中國有強大的設計服務團隊,包括前端,驗證,DFT等全套設計服務。

2012-02-23 09:49:46 1301

1301 GlobalFoundries 已開始在紐約的 Fab 8 廠房中安裝硅穿孔(TSV)設備。如果一切順利,該公司希望在2013下半年開始採用 20nm 及 28nm 製程技術製造3D堆疊晶片。

2012-05-01 10:13:12 1435

1435 據報道,2012年臺積電準備為其R&D投入13億美元,作為本年度資本支出預算中的一部分。去年,臺積電的R&D預算首次突破10億美元。而今年多出的30%將會用于20nm和14nm工藝研發。20nm工藝預計

2012-05-15 10:18:21 942

942 3D已經成為半導體微細加工技術到達物理極限之后的必然趨勢,目前正處于3D工藝的探索期。在這一過程中,以及今后在實現3D工藝的發展趨勢中,半導體產業發展模式到底如何演義,會

2012-05-15 10:43:25 1295

1295 據臺灣媒體報道,臺積電(TSMC)預計會在下月試產20nm芯片制程,即將成為全球首家進入20nm技術的半導體公司。若該芯片試產成功,將超越英特爾(Intel)的22nm制程,拉開與三星電子(

2012-07-18 09:44:33 1159

1159 本文通過高清圖詳解Intel最新22nm 3D 晶體管 。業界一直傳說3D三柵級晶體管技術將會用于下下代14nm的半導體制造,沒想到英特爾竟提前將之用于22nm工藝,并且于上周四向全世界表示將在

2012-08-03 17:09:18 0

0 8月14日消息,ARM和芯片工廠Globalfoundries日前宣布,雙方將聯手研發20nm工藝節點和FinFET技術。 ARM之前和臺積電進行了緊密合作,在最近發布了若干使用臺積電28nm工藝節點制作的硬宏處理

2012-08-14 08:48:11 877

877 Altera公司昨日公開了在其下一代20nm產品中規劃的幾項關鍵創新技術。延續在硅片融合上的承諾,Altera向客戶提供終極系統集成平臺,以結合FPGA的硬件可編程功能、數字信號處理器和微

2012-09-07 09:25:04 881

881 每一代硅片新技術既帶來了新機遇,也意味著挑戰,因此,當我們設計系統時,需要重新審視最初所作出的成本和功耗決定。20 nm以及今后的硅片技術亦是如此。 Altera在 20nm 制造節點的

2012-09-07 09:41:08 703

703 Mentor Graphics公司日前宣布Calibre LFD(光刻友好設計)光刻檢查工具已獲得TSMC的20nm IC制造工藝認證。 Calibre LFD可對熱點進行識別,還可對設計工藝空間是否充足進行檢查。光學臨近校正法

2012-09-29 10:30:46 2224

2224 電子發燒友網核心提示 :Mentor Graphics公司日前宣布Calibre LFD(光刻友好設計)光刻檢查工具已獲得TSMC的20nm IC制造工藝認證。 Calibre LFD可對熱點進行識別,還可對設計工藝空間是否充足進

2012-10-08 16:00:14 1264

1264 近期,Altera發布其下一代20nm產品中規劃的幾項關鍵創新技術,延續在硅片融合上的承諾,克服了20nm設計五大挑戰,實現了系統集成、串行帶寬、DSP性能三大突破。

2012-10-16 11:29:10 1517

1517 電子發燒友網核心提示: 本文就可編程邏輯廠商阿爾特拉(Altera)公司首次公開的20nm創新技術展開調查以及深入的分析;深入闡述了FPGA邁向20nm工藝,Altera憑借其異構3D IC、高速收發器

2012-11-01 13:48:58 2580

2580 電子發燒友網訊:關于摩爾定律的經濟活力問題,有很多的討論。在過去的一年中,20nm節點進入到這個辯論的前沿和中心。無論說辭如何,包括賽靈思在內的行業領導在20nm研發上的積極

2012-11-14 11:19:52 1661

1661 Xilinx公布其在20nm產品的表現上還將保持領先一代的優勢,究竟在20 nm制程上,Xilinx的產品有哪些演進使其保持領先競爭對手一代的優勢?詳見本文

2013-01-10 09:33:43 1314

1314 臺灣半導體制造公司(TSMC)將為蘋果提供AP/ GPU集成的解決方案,并且采用20nm Soc片上系統工藝為蘋果代工。

2013-01-17 20:58:17 1766

1766 本月25日,2013年3D打印技術產業化論壇將于東莞南城天安數碼城舉行,屆時,全球頂尖3D打印機制造商美國Stratasys公司將展出當今世界最尖端的3D打印機及相關設備。

2013-04-22 11:37:11 1488

1488 Programmable器件;發布行業第一個ASIC級可編程架構UltraScale?。這些具有里程碑意義的行業第一發布,延續了賽靈思在28nm領域投片首款器件以及在All Programmable SoC、All Programmable 3D IC和SoC增強型設計套件上所實現的一系列行業第一的優勢。

2013-07-09 20:01:50 4286

4286 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲器設計上進行了驗證 ,可實現多塊模的整合。它將臺積電的3D堆疊技術和Cadence?3D-IC解決方案相結合,包括了集成的設計工具、靈活的實現平臺,以及最終的時序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1717

1717 017年20nm、16nm及以下的先進工藝將成為主流,這對我們設計業、制造業是一個很大的啟示:我們怎么樣適應全球先進工藝。

2013-12-16 09:40:21 2411

2411 在絕大部分使用電池供電和插座供電的系統中,功耗成為需要考慮的第一設計要素。Xilinx決定使用20nm工藝的UltraScale器件來直面功耗設計的挑戰,本文描述了在未來的系統設計中,使用Xilinx 20nm工藝的UltraScale FPGA來降低功耗的19種途徑。

2018-07-14 07:21:00 6608

6608 intel的22nm 3D工藝牛,到底牛到什么程度,到底對業界有神馬影響,俺也搞不太清楚。這不,一封email全搞定了。

2017-02-11 10:47:11 1694

1694 20nm會延續摩爾定律在集成上發展趨勢,但是要付出成本代價。2.5D封裝技術的發展,進一步提高了集成度,但是也增大了成本,部分解決了DRAM總線電源和帶寬問題,在一個封裝中集成了種類更多的IC。隨著系統性能的提高,這一節點也增加了體系結構的復雜度。目前為止,它也是功耗管理最復雜的節點。

2017-09-15 09:54:30 10

10 在28nm技術突破的基礎上,賽靈思又宣布推出基于20nm節點的兩款業界首創產品。賽靈思是首家推出20nm商用芯片產品的公司。此外,該新型器件也是賽靈思將向市場推出的首款采用UltraScale技術

2018-01-12 05:49:45 1061

1061 層數的增加也就意味著對工藝、材料的要求會提高,要想達到140層堆疊就必須使用新的基礎材料。而且在堆疊層數增加的時候,存儲堆棧的高度也在增大,然而每層的厚度卻在縮小,以前的32/36層3D NAND

2018-05-28 16:25:48 51340

51340 而且在堆疊層數增加的時候,存儲堆棧的高度也在增大,然而每層的厚度卻在縮小,以前的32/36層3D NAND的堆棧厚度為2.5μm,層厚度大約70nm,48層的閃存堆棧厚度為3.5μm,層厚度減少到

2018-06-03 09:50:55 6262

6262 三維單片堆疊基本上是多芯片堆疊,先將需要高溫工藝的芯片做好,然后將其它已半制造好的芯片以離子切割(ion cut,基本上是氫離子)方式打薄,粘著于原來的芯片之上,繼續后面的低溫工藝。由于芯片內各模塊

2018-08-17 14:54:44 4930

4930 在近日舉行的英特爾“架構日”活動中,英特爾不僅展示了基于10納米的PC、數據中心和網絡系統,支持人工智能和加密加速功能的下一代“Sunny Cove”架構,還推出了業界首創的3D邏輯芯片封裝技術——Foveros。這一全新的3D封裝技術首次引入了3D堆疊的優勢,可實現在邏輯芯片上堆疊邏輯芯片。

2018-12-14 16:03:40 9951

9951 在近日舉行的英特爾“架構日”活動中,英特爾不僅展示了基于10納米的PC、數據中心和網絡系統,支持人工智能和加密加速功能的下一代“Sunny Cove”架構,還推出了業界首創的3D邏輯芯片封裝技術——Foveros。這一全新的3D封裝技術首次引入了3D堆疊的優勢,可實現在邏輯芯片上堆疊邏輯芯片。

2018-12-14 15:35:32 8854

8854 英特爾近日向業界推出了首款3D邏輯芯片封裝技術“Foveros”,據悉這是在原來的3D封裝技術第一次利用3D堆疊的優點在邏輯芯片上進行邏輯芯片堆疊。也是繼多芯片互連橋接2D封裝技術之后的又一個顛覆技術。

2018-12-14 16:16:45 3316

3316 近日,武漢新芯研發成功的三片晶圓堆疊技術備受關注。有人說,該技術在國際上都處于先進水平,還有人說能夠“延續”摩爾定律。既然3D芯片堆疊技術有如此大的作用,那今天芯師爺就跟大家一起揭開它的面紗。

2018-12-31 09:14:00 34067

34067 關鍵詞:UltraScale+ , MPSoC , 3D IC 引言 在賽靈思 20nm UltraScale MT 系列成功基礎上,賽靈思現又推出了全新的 16nm UltraScale+ 系列

2018-12-28 00:02:02 1503

1503 對于目前的高端市場,市場上最流行的2.5D和3D集成技術為3D堆疊存儲TSV,以及異構堆疊TSV中介層。Chip-on-Wafer-on-Substrate(CoWos)技術已經廣泛用于高性能計算

2019-02-15 10:42:19 8043

8043

“臺積公司是我們在 28nm、20nm 和 16nm 實現‘三連冠(3 Peat)’成功的堅實基礎。其出色的工藝技術、3D 堆疊技術和代工廠服務,讓賽靈思在出色的產品、優異的品質、強大的執行力以及領先的市場地位上享有了無與倫比的聲譽。

2019-08-01 09:24:52 2912

2912 對于3D封裝技術,英特爾去年宣布了其對3D芯片堆疊的研究,AMD也談到了在其芯片上疊加3D DRAM和SRAM的方案。

2019-08-13 10:27:53 3414

3414 年初,Intel推出了全新的Foveros 3D立體芯片封裝技術,首款產品為Lakefield,基于英特爾最新的10nm工藝制造,集成了一個大核心CPU和四個小核心CPU,其中大核心

2019-09-03 11:23:00 4487

4487 困于10nm的Intel也在這方面尋找新的機會,其在去年年底的“架構日”活動中,推出其業界首創的3D邏輯芯片封裝技術——Foveros,Foveros首次引入3D堆疊的優勢,可實現在邏輯芯片上堆疊

2020-01-28 16:10:00 4118

4118 賽靈思UltraScale架構:行業第一個ASIC級可編程架構,可從20nm平面晶體管結構 (planar)工藝向16nm乃至FinFET晶體管技術擴展,從單芯片(monolithic)到3D IC擴展。

2019-12-18 15:30:23 1310

1310 SIP有多種定義和解釋,其中一說是多芯片堆疊的3D封裝內系統集成,在芯片的正方向堆疊2片以上互連的裸芯片的封裝。SIP是強調封裝內包含了某種系統的功能封裝,3D封裝僅強調在芯片方向上的多芯片堆疊

2020-05-28 14:51:44 7076

7076 他們未來的3nm工廠,預計2022年下半年臺積電3nm工藝就會投產。 當然隨著半導體工藝的逐漸發展,工藝的升級也逐漸困難,所需的投入也越來越大,報團合作也越來越多,臺積電拉了Google和AMD過來合作。 臺積電正在和Google合作,以推動3D芯片制

2020-11-30 15:50:10 1146

1146 在Intel、臺積電各自推出自家的3D芯片封裝技術之后,三星也宣布新一代3D芯片技術——X-Cube,基于TSV硅穿孔技術,可以將不同芯片搭積木一樣堆疊起來,目前已經可以用于7nm及5nm工藝。

2020-10-10 15:22:58 2004

2004 根據報道,華為將在國內建設一家45nm制程工藝起步的芯片工廠,計劃在2021年底為物聯網設備制造28nm的芯片,并在2022年底之前為5G設備供應20nm的芯片。

2020-11-02 17:41:30 3542

3542 Integrity 3D-IC 是 Cadence 新一代多芯片設計解決方案,它將硅和封裝的規劃和實現,與系統分析和簽核結合起來,以實現系統級驅動的 PPA 優化。 原生 3D 分區流程可自動智能

2021-11-19 11:02:24 4231

4231 三星3nm芯片量產 2nm芯片還遠嗎 全球第一款正式量產的3nm芯片即將出自三星半導體了,根據三星半導體官方的宣布,4D(GAA)架構制程技術芯片正式開始生產。 4D(GAA)架構制程是3D

2022-06-30 20:21:52 2069

2069 目前有多種基于 3D 堆疊方法, 主要包括: 芯片與芯片的堆疊( D2D) 、芯片與圓片的堆疊( D2W ) 以及圓片與圓片的堆疊( W2W) 。

2022-11-01 09:52:51 2488

2488 在20nm 工藝節點之后,傳統的平面浮柵 NAND 閃速存儲器因受到鄰近浮柵 -浮柵的耦合電容干擾而達到了微縮的極限。為了實現更高的存儲容量,NAND集成工藝開始向三維堆疊方向發展。在三維NAND

2023-02-03 09:16:57 17470

17470 當裸片尺寸無法繼續擴大時,開發者開始考慮投入對 3D 堆疊裸片方法的研究。考慮用于 3D 封裝的高端器件已經將當前的可測試性設計 (DFT) 解決方案推向了極限。

2023-02-28 11:39:26 2362

2362 UltraScale是基于20nm工藝制程的FPGA,而UltraScale+則是基于16nm工藝制程的FPGA。

2023-03-09 14:12:54 8669

8669 我們之前見過的閃存多屬于Planar NAND平面閃存,也叫有2D NAND或者直接不提2D的,而3D 閃存,顧名思義,就是它是立體堆疊的,Intel之前用蓋樓為例介紹了3D NAND,普通NAND是平房,那么3D NAND就是高樓大廈,建筑面積一下子就多起來了,理論上可以無線堆疊。

2023-03-30 14:02:39 4222

4222 3D NAND閃存是一種把內存顆粒堆疊在一起解決2D或平面NAND閃存限制的技術。這種技術垂直堆疊了多層數據存儲單元,具備卓越的精度,可支持在更小的空間內,容納更高的存儲容量,從而有效節約成本、降低能耗,以及大幅度地提升性能。

2023-06-15 09:37:56 3209

3209

有許多外行人認為3D打印就是從熱噴嘴中擠出材料并堆疊成形狀,但其實3D打印遠不止于此!今天南極熊將介紹七大類3D打印工藝,即使是3D打印小白也能清晰地區分不同的3D打印工藝。 事實上,3D 打印也

2023-06-29 15:36:27 4381

4381 隨著摩爾定律接近物理界限,在3納米以下的先進工藝中,能夠負擔較高費用的顧客受到限制,晶片sip和邏輯芯片的3D堆疊概念正在成為重要的新一代趨勢。

2023-09-11 11:09:58 2010

2010 Cadence員工MohamedNaeim博士曾在CadenceLIVE歐洲用戶大會上做過一場題為《2D/3D熱分析和三裸片堆疊設計實現》的演講,本文將詳細講述該演講內容。實驗:兩個裸片是否優于一個

2023-09-16 08:28:05 2057

2057

長期以來,個人計算機都可以選擇增加內存,以便提高處理超大應用和大數據量工作的速度。由于3D芯片堆疊的出現,CPU芯粒也有了這個選擇,但如果你想打造一臺更具魅力的計算機,那么訂購一款有超大緩存的處理器可能是正確的選擇。

2023-10-15 10:24:23 2733

2733

當芯片變身 3D 系統,3D 異構集成面臨哪些挑戰

2023-11-24 17:51:07 1969

1969

在3D實現方面,存儲器比邏輯更早進入實用階段。NAND閃存率先邁向3D 。隨著目前量產的20-15nm工藝,所有公司都放棄了小型化,轉而轉向存儲單元的三維堆疊,以提高每芯片面積的位密度。它被稱為“ 3D(三維)NAND ” 。

2023-12-02 16:38:40 2967

2967

在半導體行業的快速發展歷程中,芯片封裝技術始終扮演著至關重要的角色。隨著集成電路設計復雜度的不斷提升和終端應用對性能、功耗、尺寸等多方面要求的日益嚴苛,傳統的2D封裝技術已經難以滿足市場的需求。在此背景下,芯片3D堆疊封裝技術應運而生,成為半導體技術發展的新里程碑。

2025-02-11 10:53:45 2819

2819

電子發燒友App

電子發燒友App

評論