新思科技3DIC Compiler集成了3Dblox 2.0標準,可用于異構集成和“從架構探索到簽核”的完整解決方案。

新思科技 UCIe PHY IP在臺積公司N3E工藝上實現了首次通過硅片的成功(first-pass silicon success),可提供低延遲、低功耗和高帶寬的芯片間連接。

UCIe PHY IP與3DIC Compiler的結合將有效優化多裸晶系統設計,能夠以更低的集成風險實現更高的結果質量。

新思科技(Synopsys)兩月前宣布進一步擴大與臺積公司的合作,雙方攜手通過可支持最新3Dblox 2.0標準和臺積公司3DFabric技術的全面解決方案不斷優化多裸晶系統(Multi-Die)設計。新思科技多裸晶系統解決方案包括 “從架構探索到簽核”統一設計平臺3DIC Compiler,可提供行業領先的設計效率,來實現芯片的容量和性能要求。此外,新思科技UCIe IP也已在臺積公司領先的N3E先進工藝上取得了首次通過硅片的成功,實現了die-to-die高速無縫互連。

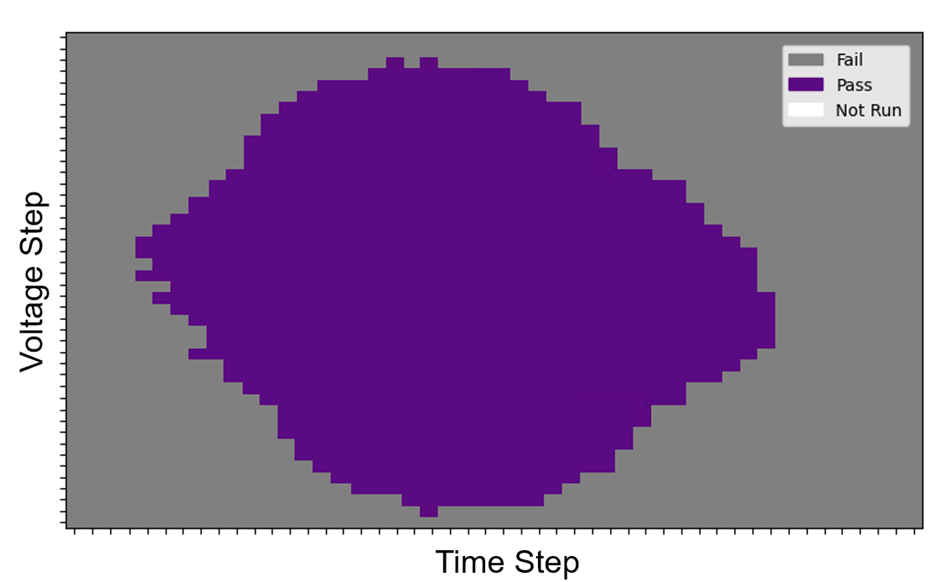

▲新思科技UCIe PHY IP在臺積公司N3E工藝上首次通過硅片的成功,展示了充足的鏈路裕量

“臺積公司長期與新思科技緊密合作,為芯片開發者提供差異化的解決方案,幫助他們解決從早期架構到制造過程中面臨的高度復雜的挑戰。我們與新思科技的長期合作,讓我們的共同客戶能夠采取針對性能和功耗效率優化的解決方案,以應對高性能計算、數據中心和汽車應用領域的多裸晶系統設計要求。”

Dan Kochpatcharin

設計基礎設施管理部負責人

臺積公司

“我們與臺積公司強強聯合,為多裸晶系統提供了全面、可擴展的解決方案,實現了前所未有的芯片性能和設計效率。采用3Dblox 2.0等通用標準在統一設計平臺上進行多裸晶系統設計的架構探索、分析和簽核,并結合在臺積公司N3E工藝上已實現首次通過硅片成功的新思科技UCIe PHY IP,客戶能夠進一步加速從早期架構探索到制造的系統設計全流程。”

Sanjay Bali

EDA事業部戰略與產品管理副總裁

審核編輯:劉清

-

新思科技

+關注

關注

5文章

957瀏覽量

52894 -

PHY

+關注

關注

2文章

335瀏覽量

54079 -

電源完整性

+關注

關注

9文章

226瀏覽量

21961

原文標題:新思科技攜手臺積公司推出“從架構探索到簽核” 統一設計平臺,簡化Multi-Die系統復雜性

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技攜手臺積公司推出“從架構探索到簽核” 統一設計平臺

新思科技攜手臺積公司推出“從架構探索到簽核” 統一設計平臺

評論