3DIC架構并非新事物,但因其在性能、成本方面的優勢及其將異構技術和節點整合到單一封裝中的能力,這種架構越來越受歡迎。隨著開發者希望突破傳統二維平面IC架構的復雜度和密度限制,3D集成提供了引入更多功能和增強性能的機會,同時可滿足尺寸限制與成本要求。

3D結構有許多優點,例如性能通常由訪問內存所需的時間和功耗決定。通過3D集成,存儲器和邏輯電路可以集成到單個3D堆棧中。這種方法通過微間距互連大大增加了內存總線的寬度,同時通過縮短互連線路減少了傳播延遲。這種連接可以使3D設計的內存訪問帶寬達到幾十Tbps,而領先的2D設計帶寬僅能達到數百Gbps。

從成本角度講,配有不同部件的大型系統在芯片實現方面有多種優點。異構集成并不是將整個芯片放置在最復雜或最昂貴的技術節點上,而是針對系統的不同部分使用“恰當”節點。例如,先進節點僅用于系統的關鍵部分,而成本較低的節點則用于不太關鍵的部分。

增加垂直維度改變了集成電路設計策略

由于設計必須從3D角度考慮,而不是僅考慮典型2D平面設計的x、y,因此,必須增加z維度進行全面管理——從架構設計到邏輯驗證和路由連接——包括凸塊和通硅孔(TSV)、熱量和電源分配網絡(PDN)的新權衡(例如基于中介層與3D堆棧、邏輯內存與內存邏輯,以及混合鍵合與凸塊),優化PPA仍然是一個關鍵指導因素。然而,由于3DIC的出現實現了立方毫米優化,因為不僅僅考慮兩個方向,而且在所有的權衡決策中還必須考慮垂直維度。

更為復雜的是,3DIC的集成度更高,傳統電路板和手工封裝技術已經不合時宜,例如高速互連的凸塊布局和定制布局,這導致了額外的瓶頸出現。最重要的是,以前不同學科之間的相互依賴性現在則需要在聯合設計方法(人員和工具)中予以考慮,這涉及到設計IP、芯片封裝、架構、實現和系統分析等所有階段。

采取芯片優先的方法

盡管采用與印刷電路板(PCB)設計類似的方式考慮3D架構似乎是一種顯而易見的選擇,但3DIC最好采用芯片優先的方法——即優化(整個芯片的)設計IP并共同設計芯片系統和封裝方法。在3DIC方法中,新思科技正在將IC設計的關鍵概念和創新成果引入3DIC領域。這需要考察3DIC的各個方面,例如架構設計、將高度自動化能力引入手動任務中、擴展解決方案以支持高級封裝的高集成度,以及將簽核分析集成到設計流程中。

3DIC將封裝(過去采用類似PCB的工具進行管理)與芯片集成在一起。PCB工具沒有連接在一起,無法適應規模和工藝的復雜性。典型的PCB中可能有10,000個接點。但在復雜的3DIC中,接點數量很快會達到數十億,規模遠遠超出了過去以PCB為中心的方法所能管理的范圍。對于以IP優化方式堆疊的裸晶,現有的PCB工具無法提供幫助。此外,PCB工具不能利用RTL或系統設計決策。現實情況是,單一的設計工具不可能處理3DIC的所有方面(IP、芯片、中介層、封裝),這對完整堆棧的組裝和可視化提出了迫切的需求。

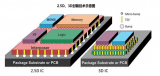

新思科技3DIC Compiler作為一個為3DIC系統集成和優化而構建的平臺可以做到這些。該解決方案專注于多芯片系統,如硅片上芯片中介層(2.5D)、晶片上芯片、晶片上晶片、芯片上芯片和3D SoC。

PPA三要素

通常,在想到大型的復雜SoC時,首先考慮優化的是面積。芯片開發者希望在芯片中集成盡可能多的功能,并提供盡可能高的性能。但隨后,所需的功耗和熱量始終要符合要求,特別是在移動、可穿戴AR和物聯網等應用領域(在數據中心的高性能計算等領域也越來越重要,因為總體能耗也是優先考慮的事項)。實現3D結構使開發者能夠持續增加產品的功能,而不會超過占位面積和高度的限制,同時還降低芯片成本。

但是,單獨的工具只能解決設計3DIC時的部分復雜挑戰。這就形成了巨大的設計反饋回路,無法及時將這些反饋整合在一起,形成每立方毫米最佳PPA的最佳解決方案。在多裸晶環境中,必須對整個系統進行分析和優化。孤立地對單個裸晶進行功耗和熱量分析是不夠的。更有效的解決方案是采用統一的平臺,將整個系統的信號、功耗和熱量分析整合到單個緊密耦合的解決方案中。

這正是3DIC Compiler的用武之地——通過一套完整的功耗和熱量分析能力實現早期分析。該解決方案通過全面的自動化功能減少了迭代次數,同時提供功耗完整性、熱量和噪聲感知優化。這有助于開發者更好地了解系統性能,并圍繞系統架構、在何處插入TSV以及最高效的裸晶堆疊方法進行探索。另外,它還有助于更有效地了解如何將各種設計要素組合在一起,甚至以某些方式將設計工程師與傳統的2D設計技術聯系起來。

3DIC是實現每立方毫米最佳PPA的理想平臺

通過將硅片垂直堆疊到單個封裝器件中,3DIC不斷證明其在性能、功耗和面積方面能夠持續支持摩爾定律。

盡管使用集成設計平臺設計3D架構時會出現新的細微差異,但以最低功耗實現最高性能的可能性使3D架構成為極具吸引力的選擇。隨著芯片開發者努力實現每立方毫米的最佳PPA,3DIC必將得到更廣泛的應用。

編輯:jq

-

芯片

+關注

關注

462文章

53623瀏覽量

460226 -

存儲器

+關注

關注

39文章

7716瀏覽量

170994 -

3DIC

+關注

關注

3文章

89瀏覽量

20072 -

PPA

+關注

關注

0文章

21瀏覽量

7782

原文標題:3DIC為后摩爾時代追求最佳PPA提供理想平臺

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

首創3D-CIM架構!微納核芯定義后摩爾時代AI算力新范式

Socionext推出3D芯片堆疊與5.5D封裝技術

臺積電日月光主導,3DIC先進封裝聯盟正式成立

華大九天新一代全定制IC設計平臺Empyrean Aether介紹

3DIC 測試革新:AI 驅動的 ModelOps 如何重構半導體制造效率?

先進封裝轉接板的典型結構和分類

后摩爾時代破局者:物元半導體領航中國3D集成制造產業

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

行芯科技亮相第三屆芯粒開發者大會

后摩爾時代:芯片不是越來越涼,而是越來越燙

行芯科技亮相2025世界半導體博覽會

行芯科技揭示先進工藝3DIC Signoff破局之道

廣電計量受邀參加后摩爾器件研討會 攜半導體綜合技術解決方案亮相

3DIC提供理想平臺為后摩爾時代追求最佳PPA

3DIC提供理想平臺為后摩爾時代追求最佳PPA

評論