來源:睞芯科技LightSense

原文作者:LIG

本文簡單介紹3D堆疊發(fā)展過程中面臨的挑戰(zhàn)。

3D堆疊將不斷發(fā)展,以實現(xiàn)更復(fù)雜和集成的設(shè)備——從平面到立方體

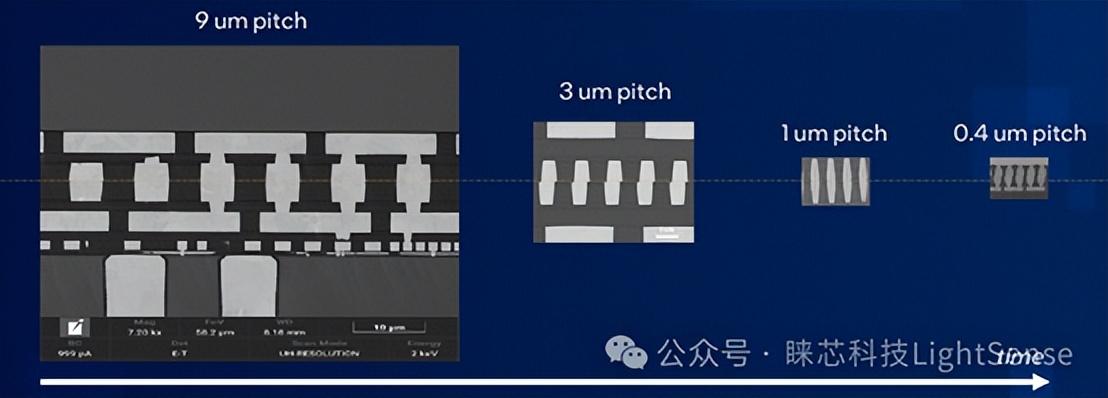

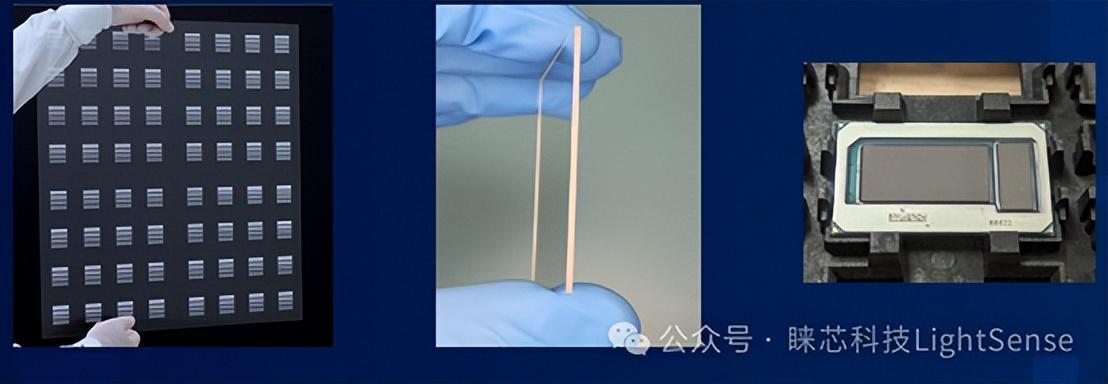

挑戰(zhàn)1:間距縮小

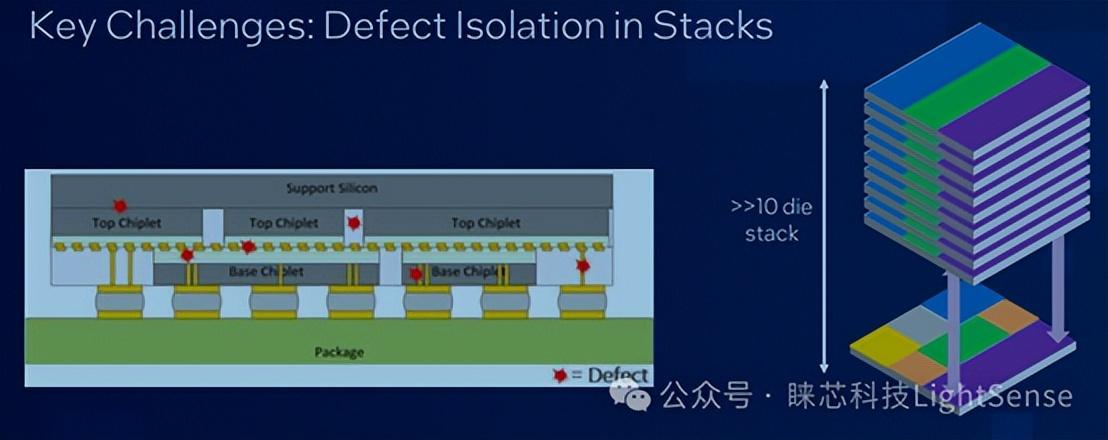

挑戰(zhàn)2:缺陷

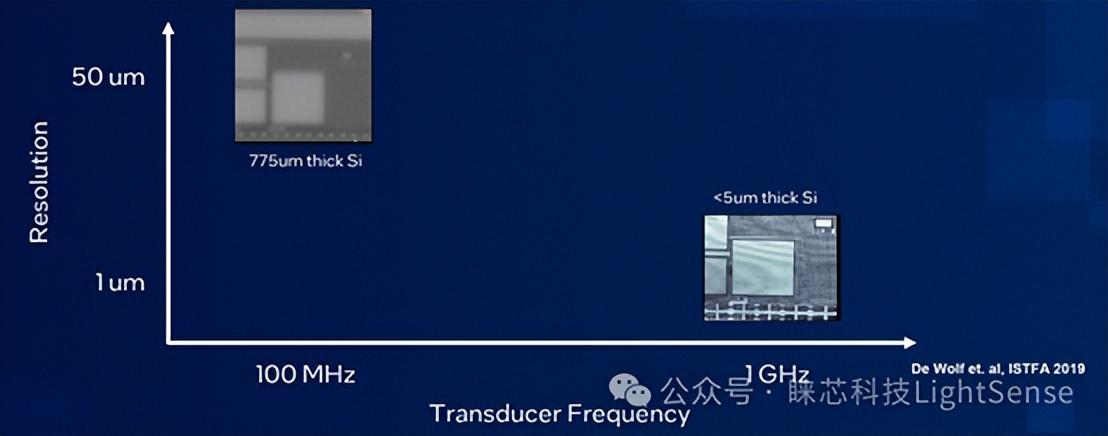

挑戰(zhàn)3:高分辨率的CSAM(超聲掃描顯微鏡C-mode Scanning Acoustic Microscope)。CSAM是一種關(guān)鍵的計量學(xué),但更高的分辨率需要樣品制備/管芯薄化,而3D堆疊結(jié)構(gòu)并不總是能夠做到這一點。

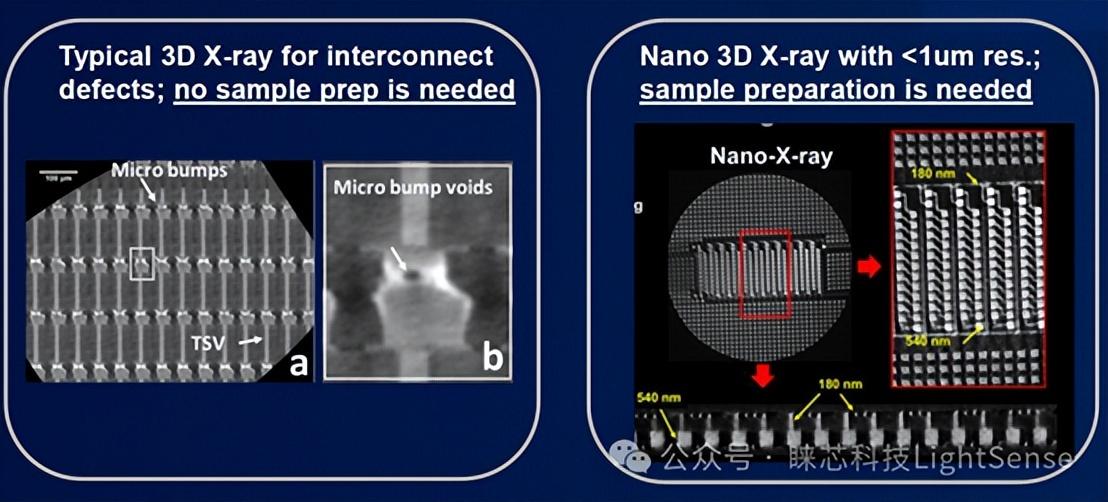

挑戰(zhàn)4:高分辨率成像。需要在成像方面進行創(chuàng)新,以非破壞性地快速檢測埋在多個界面下的細(xì)微缺陷。達到精細(xì)間距特征的高分辨率所需的樣品準(zhǔn)備和長掃描時間將減緩產(chǎn)量學(xué)習(xí)并影響上市時間。

挑戰(zhàn)5:玻璃基板。玻璃提供了改進的材料性能,從而提高了尺寸穩(wěn)定性和縮放能力。

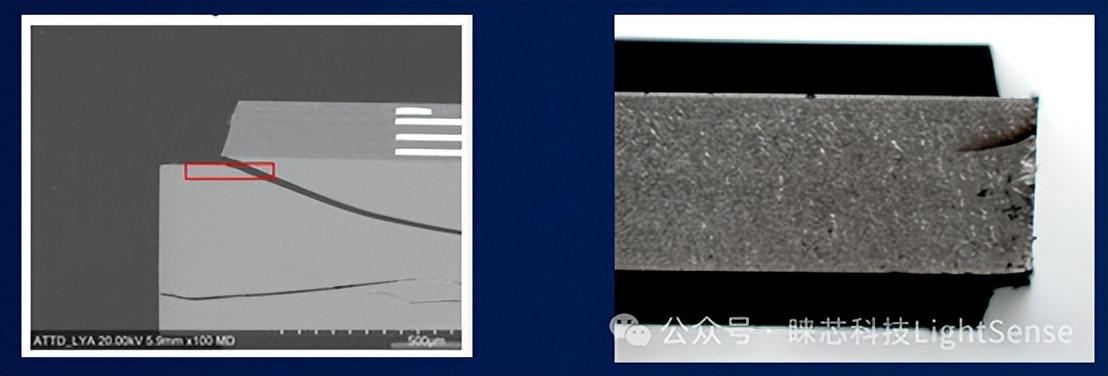

挑戰(zhàn)6:裂痕檢查。需要新的在線計量來快速檢測玻璃基板中的微米級裂紋。左圖:分片時導(dǎo)致的邊緣缺陷;右圖:如果未被發(fā)現(xiàn),可能會變得嚴(yán)重的裂縫會失效。

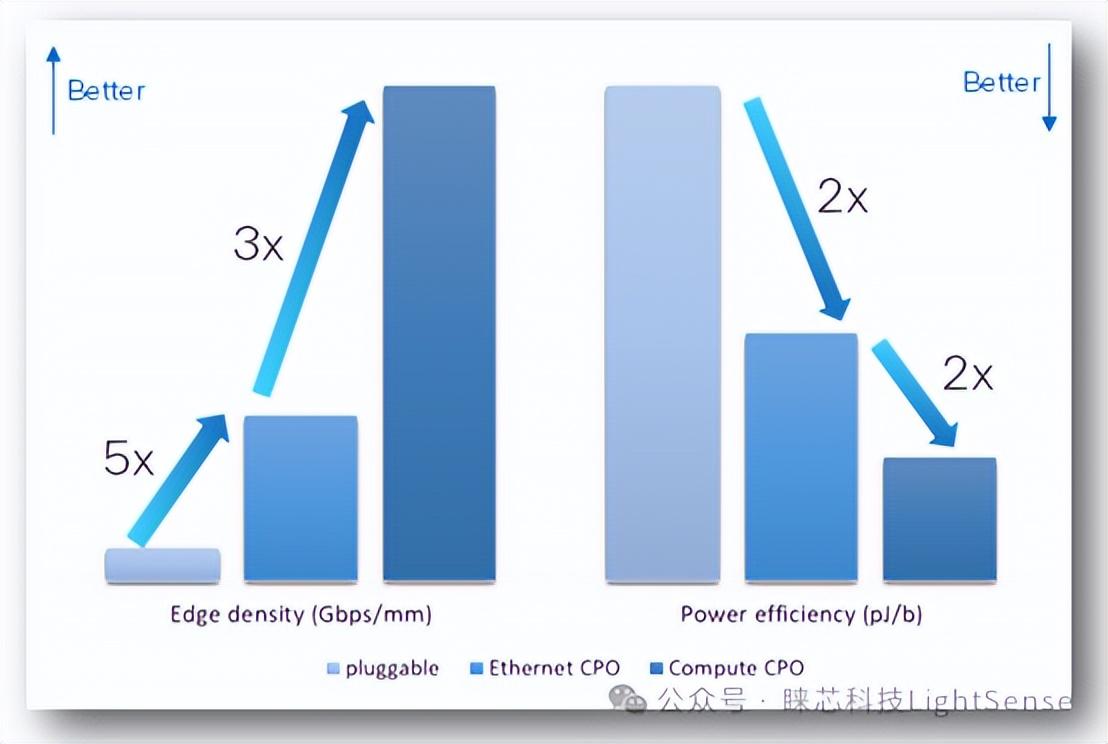

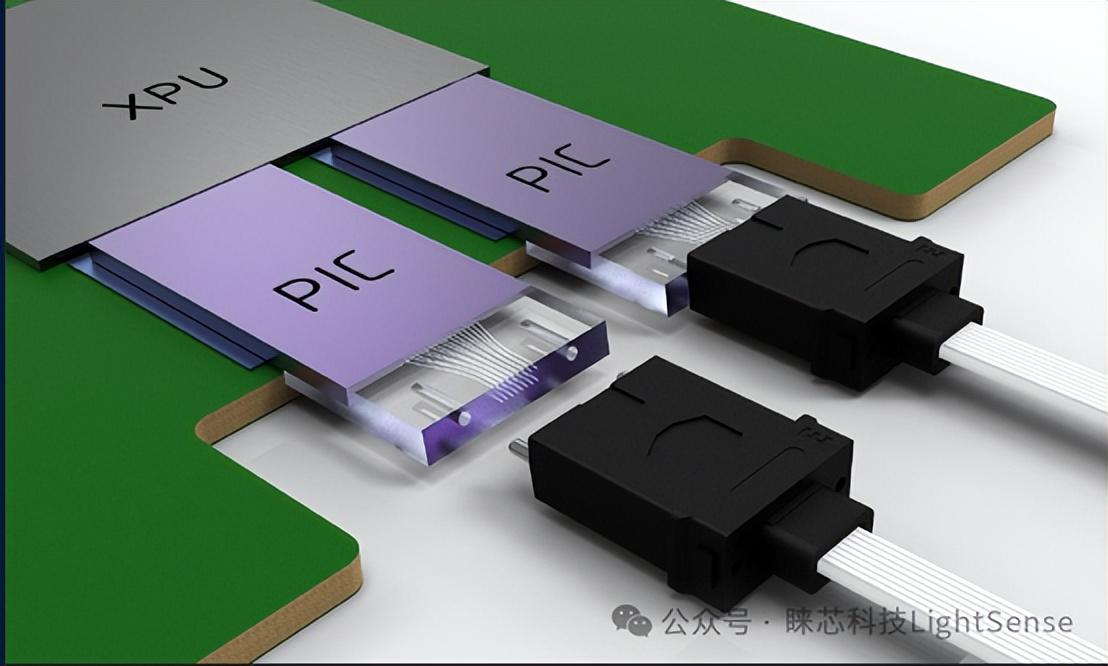

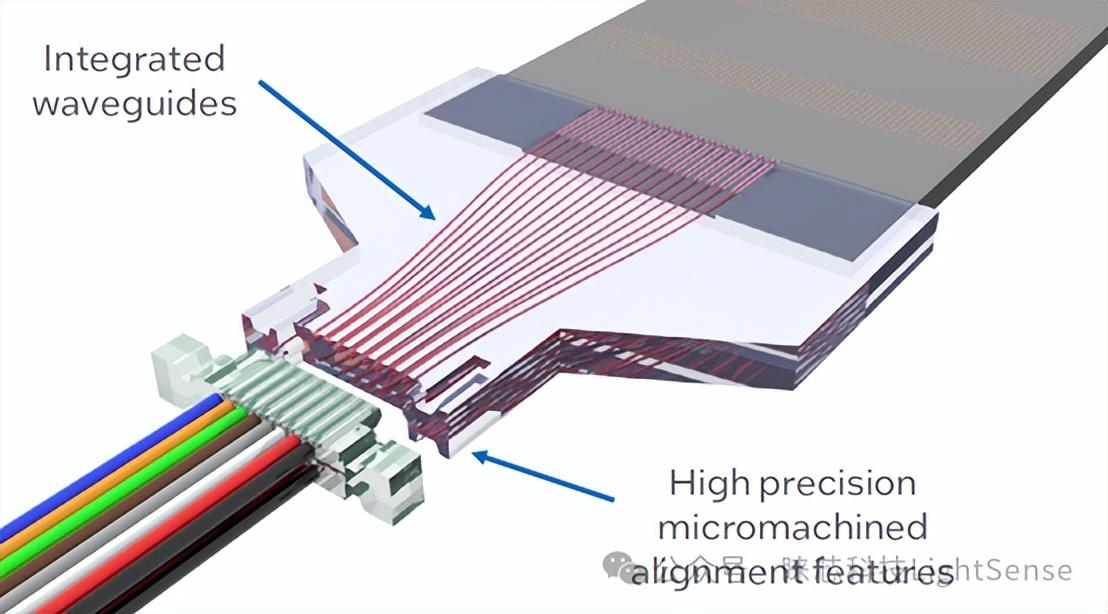

挑戰(zhàn)7:Co-Packaged Optics共封裝光學(xué)器件。集成波導(dǎo)的玻璃橋是實現(xiàn)大容量兼容可插拔解決方案的關(guān)鍵。玻璃中光波導(dǎo)三維映射的無損方法+透明基板上精細(xì)特征的高精度測量。

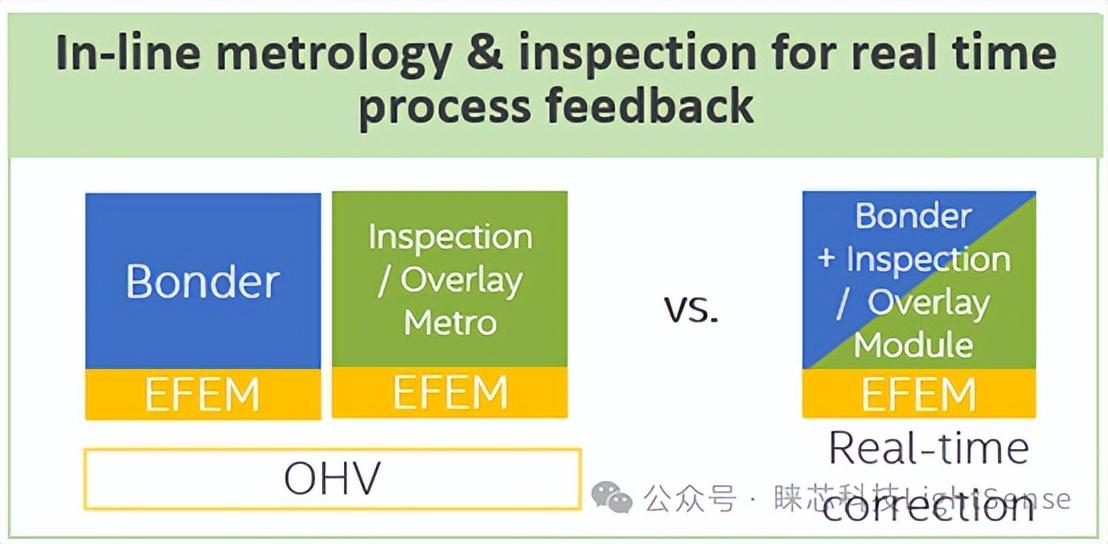

挑戰(zhàn)8:計量。需要在過程工具內(nèi)實現(xiàn)更高水平的計量集成,以實現(xiàn)實時過程反饋和控制。

-

3D堆疊封裝

+關(guān)注

關(guān)注

0文章

18瀏覽量

7603

發(fā)布評論請先 登錄

先進封裝時代,芯片測試面臨哪些新挑戰(zhàn)?

從3D堆疊到二維材料:2026年芯片技術(shù)全面突破物理極限

簡單認(rèn)識3D SOI集成電路技術(shù)

一文掌握3D IC設(shè)計中的多物理場效應(yīng)

iDS iToF Nion 3D相機,開啟高性價比3D視覺新紀(jì)元!

西門子V90伺服,為3D打印企業(yè)降本增效“加足馬力”

技術(shù)深潛:超聲波切割技術(shù)如何破解3D打印后處理瓶頸

西門子EDA重塑3D IC設(shè)計:突破高效協(xié)同、可靠驗證、散熱及應(yīng)力管理多重門

玩轉(zhuǎn) KiCad 3D模型的使用

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導(dǎo)體芯片產(chǎn)業(yè)的前沿技術(shù)

TechWiz LCD 3D應(yīng)用:局部液晶配向

TechWiz LCD 3D應(yīng)用:微液晶分子摩擦排布

芯片晶圓堆疊過程中的邊緣缺陷修整

3D堆疊發(fā)展過程中面臨的挑戰(zhàn)

3D堆疊發(fā)展過程中面臨的挑戰(zhàn)

評論