Socionext推出先進的3D芯片堆疊與5.5D封裝技術全面擴展3DIC的產品組合

實現面向緊湊、低功耗的消費品類應用以及高性能AI、HPC產品的3DIC技術的量產適用

Socionext Inc.(以下簡稱“Socionext”)宣布,其3DIC設計現已支持面向消費電子、人工智能(AI)和高性能計算(HPC)數據中心等多種應用。通過結合涵蓋Chiplet、2.5D、3D及5.5D的先進封裝技術組合與強大的SoC設計能力,Socionext將提供高性能、高品質的解決方案,助力客戶實現創新并推動其業務增長。

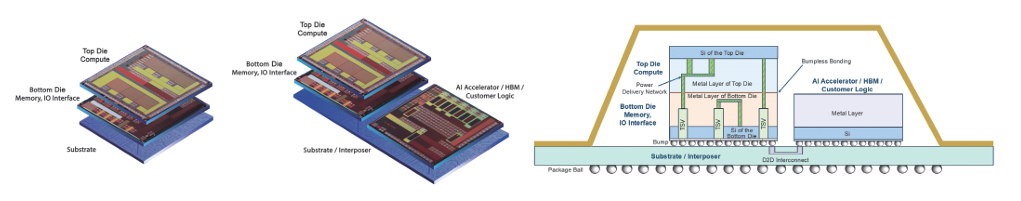

作為一項關鍵里程碑, Socionext基于TSMC SoIC-X 3D堆疊技術,成功完成了一款完整封裝芯片的流片。該設計采用面對面(F2F)堆疊架構,將3納米制程的計算芯片與5納米制程的I/O芯片集成于一體。相較于傳統2D和2.5D設計方案,這種F2F 3D堆疊技術極大縮短了互連距離,顯著降低了信號延遲與功耗。

垂直堆疊:釋放3DIC設計的無限潛能

憑借在2.5D設計領域積累的豐富經驗,Socionext將成熟的設計經驗與方法論應用于3DIC技術,通過垂直堆疊晶粒的方式充分發揮關鍵性能優勢。

3DIC F2F與5.5D結構

? 異構集成

3D IC可將不同工藝節點(3nm、5nm、7nm)及功能模塊(邏輯單元、存儲單元、接口單元等)集成于同一封裝內,實現性能、密度與成本的最優平衡。

? 高集成密度賦能廣泛應用場景

垂直堆疊技術能夠在更小尺寸內實現更強大的功能——這一優勢在傳統制程微縮逼近物理極限的當下顯得尤為重要,對于空間受限的消費類電子設備具有顯著價值。

? 性能提升

芯片間更短更寬的互聯路徑顯著降低延遲并提升帶寬。

? 功耗優化

緊湊型互連結構通過降低阻抗特性,顯著減少驅動功耗需求。

未來愿景

3DIC及5.5D技術的推進體現了Socionext對推動異構集成技術的高度重視。通過將多元功能整合于統一的半導體與封裝系統中,為未來技術發展奠定基礎。隨著市場對可擴展、高密度與高能效平臺需求的持續增長,尤其在消費電子、人工智能(AI)及數據中心領域,3DIC技術將在塑造半導體行業未來創新格局中發揮關鍵作用。

Socionext首席技術官兼執行副總裁Rajinder Cheema表示:"依托在SoC設計領域的豐富經驗以及與TSMC的緊密合作,使我們始終處于下一代SoC開發的前沿。此次里程碑正是我們不斷提供能夠滿足客戶日益增長需求之尖端解決方案的最佳體現。"

關于Socionext

Socionext是全球領先的SoC供應商,也是“Solution SoC”商業模式的開拓者。這種創新模式整合了Socionext的“Entire Design”能力并提供了“Complete Service”。作為值得信賴的芯片合作伙伴,Socionext 推動全球創新,提供卓越的功能、性能和質量,使客戶的產品和服務在汽車、數據中心、網絡、智能設備和工業設備等不同領域脫穎而出。Socionext Inc.總部位于橫濱,在日本、亞洲、美國和歐洲均設有辦事處,負責開發和銷售。

-

封裝

+關注

關注

128文章

9305瀏覽量

148946 -

3DIC

+關注

關注

3文章

92瀏覽量

20157 -

Socionext

+關注

關注

2文章

78瀏覽量

17259

原文標題:Socionext推出先進的3D芯片堆疊與5.5D封裝技術全面擴展3DIC的產品組合

文章出處:【微信號:Socionext,微信公眾號:Socionext】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

從3D堆疊到二維材料:2026年芯片技術全面突破物理極限

淺談2D封裝,2.5D封裝,3D封裝各有什么區別?

【海翔科技】玻璃晶圓 TTV 厚度對 3D 集成封裝可靠性的影響評估

iTOF技術,多樣化的3D視覺應用

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

Socionext推出3D芯片堆疊與5.5D封裝技術

Socionext推出3D芯片堆疊與5.5D封裝技術

評論