簡(jiǎn)介

3DIC Compiler具有強(qiáng)大的Bump Planning功能。它可在系統(tǒng)設(shè)計(jì)初期階段沒(méi)有bump library cells的情況下,通過(guò)定義pseudo bump region patterns、創(chuàng)建bump regions以及填充pseudo bumps、創(chuàng)建Bumps的連接關(guān)系、為不同net的Bumps著色等操作,快速實(shí)現(xiàn)bump原型創(chuàng)建以及復(fù)雜bump規(guī)劃設(shè)計(jì)。

本視頻將展示在沒(méi)有bump library cells的情況下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速實(shí)現(xiàn)Bump Planning,流程包括:

定義bump region patterns

創(chuàng)建bump regions以及填充pseudo bumps

快速assign nets到對(duì)應(yīng)的Bumps

為不同net的Bumps著色

-

3DIC

+關(guān)注

關(guān)注

3文章

89瀏覽量

20072 -

芯和半導(dǎo)體

+關(guān)注

關(guān)注

0文章

124瀏覽量

32153

原文標(biāo)題:【芯和設(shè)計(jì)訣竅視頻】如何使用3DIC Compiler實(shí)現(xiàn)Bump Planning

文章出處:【微信號(hào):Xpeedic,微信公眾號(hào):Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

晶圓級(jí)封裝Bump制作中錫膏和助焊劑的應(yīng)用解析

晶圓級(jí)封裝(WLP)中Bump凸點(diǎn)工藝:4大實(shí)現(xiàn)方式的技術(shù)細(xì)節(jié)與場(chǎng)景適配

Socionext推出3D芯片堆疊與5.5D封裝技術(shù)

創(chuàng)造歷史,芯和半導(dǎo)體成為首家獲得工博會(huì)CIIF大獎(jiǎng)的國(guó)產(chǎn)EDA

臺(tái)積電日月光主導(dǎo),3DIC先進(jìn)封裝聯(lián)盟正式成立

芯動(dòng)科技與知存科技達(dá)成深度合作

3DIC 測(cè)試革新:AI 驅(qū)動(dòng)的 ModelOps 如何重構(gòu)半導(dǎo)體制造效率?

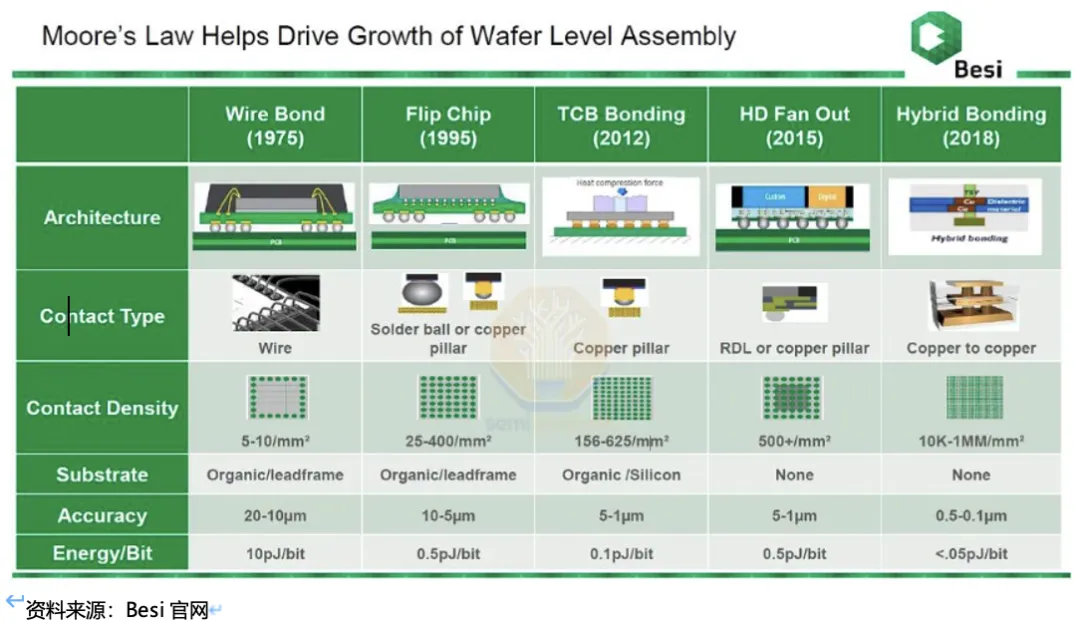

聊聊倒裝芯片凸點(diǎn)(Bump)制作的發(fā)展史

上海立芯亮相第五屆RISC-V中國(guó)峰會(huì)

行芯科技亮相第三屆芯粒開(kāi)發(fā)者大會(huì)

混合鍵合(Hybrid Bonding)工藝介紹

行芯科技亮相2025世界半導(dǎo)體博覽會(huì)

行芯科技揭示先進(jìn)工藝3DIC Signoff破局之道

深入探索:晶圓級(jí)封裝Bump工藝的關(guān)鍵點(diǎn)

將2.5D/3DIC物理驗(yàn)證提升到更高水平

芯和設(shè)計(jì)訣竅概述 如何使用3DIC Compiler實(shí)現(xiàn)Bump Planning

芯和設(shè)計(jì)訣竅概述 如何使用3DIC Compiler實(shí)現(xiàn)Bump Planning

評(píng)論