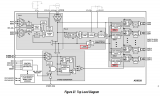

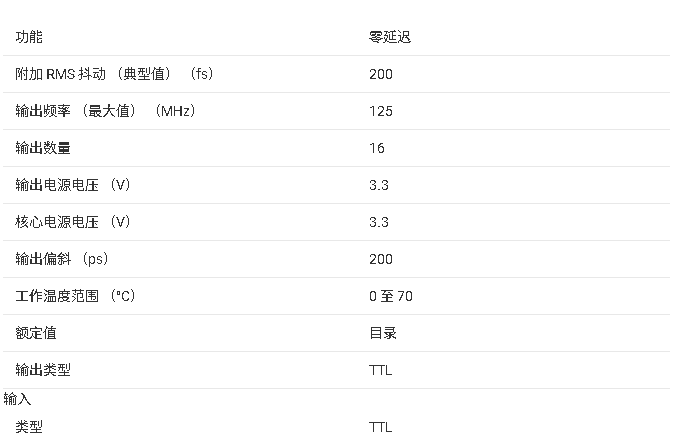

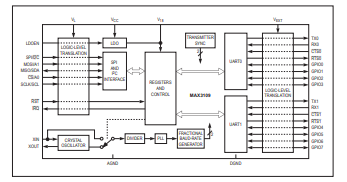

麥瑞半導體公司(Micrel Inc.)發佈了新型可高度配置的雙鎖相環(PLL)時脈產發生器系列產品,優化了超低抖動、超強串擾隔離和增強型電源雜訊抑制。SM803xxx系列產品有12個提供高達850MHz頻率的差分或單端輸出,這些輸出的RMS相位抖動均小于200飛秒(fs)。FLEX2可支援那些需要用單一IC實現多頻率、高扇出和超低抖動的高要求應用,包括10/40/100Gb乙太網、SONET/SDH、CPRI/OBSAI、光纖通道、SAS/SATA,以及FPGA和SerDes的高速時脈等。FLEX2可以通過基于熔絲的一次性可程式設計(OTP)記憶體進行工廠配置,提供了一個自訂、快速轉變和高性能的時脈解決方案,縮短了產品成型時間和終端系統設計週期。

麥瑞半導體時脈管理和通信產品事業部副總裁Rami Kanama表示:“我們堅持貫徹麥瑞半導體以高性能和高靈活性的產品豐富時脈和時脈管理產品的戰略,推出了Clockworks FLEX2系列產品。作為業界抖動最小的可定制配置的雙鎖相環時脈合成器,SM803xxx增強了頻率的靈活性,快速形成了一個全定制化的時脈解決方案。憑藉其超低抖動和集成扇出性能,FLEX2增強了系統性能,改善了誤碼率(BER)和信噪比(SNR),為用戶的高速應用提供了最急需的抖動容許量。”

SM803xxx產品現在已經開始批量生產,并向用戶提供樣品。

電子發燒友App

電子發燒友App

評論