概述

AD9576具有多路輸出時鐘發(fā)生器功能,內(nèi)置兩個具有靈活頻率轉(zhuǎn)換功能的專用鎖相環(huán)(PLL)內(nèi)核,經(jīng)過優(yōu)化可用作整個系統(tǒng)的穩(wěn)定異步時鐘源,通過監(jiān)控冗余晶體(XTAL)輸入并實現(xiàn)這些輸入之間的自動切換,可在頻率容差范圍內(nèi)延長工作壽命,同時將開關(guān)感應瞬變降至低點。小數(shù)N分頻PLL設(shè)計基于ADI公司成熟的高性能、低抖動頻率合成器產(chǎn)品系列,確保實現(xiàn)較高的網(wǎng)絡性能,而整數(shù)N分頻PLL提供通用型時鐘,可用作CPU和現(xiàn)場可編程門陣列(FPGA)參考時鐘。

數(shù)據(jù)表:*附件:AD9576雙通道PLL、異步時鐘發(fā)生器技術(shù)手冊.pdf

AD9576利用引腳短接為其11路輸出時鐘在眾多可用上電就緒配置中進行選擇,只需將外部上拉或下拉電阻連接到適當?shù)囊_編程讀取器引腳(PPRx)即可。通過這些引腳可以控制內(nèi)部分頻器,以建立所需的頻率轉(zhuǎn)換、時鐘輸出功能和輸入?yún)⒖脊δ堋_@些參數(shù)還可以通過串行端口接口(SPI)進行手動配置。

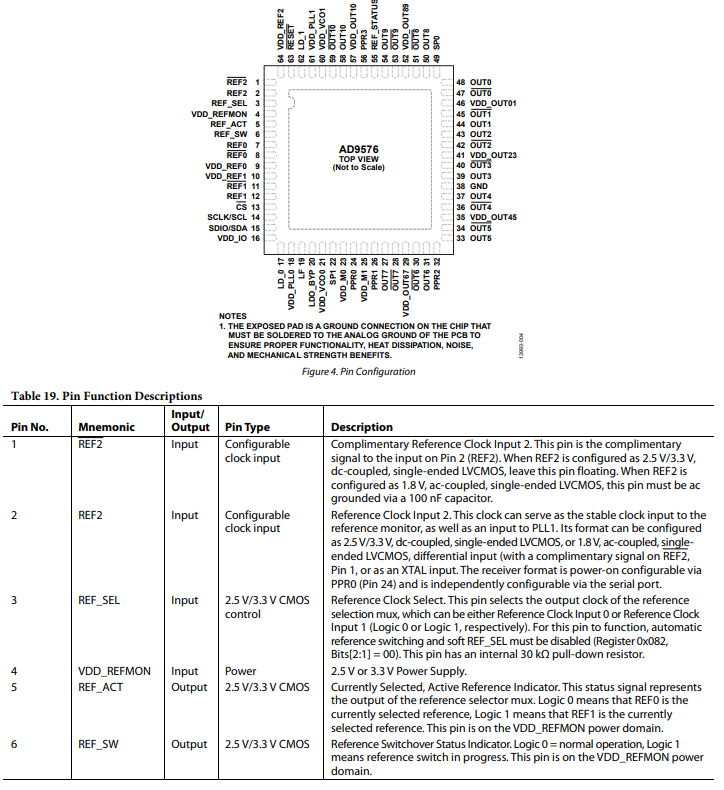

AD9576采用64引腳、9 mm × 9 mm LFCSP封裝,只需2.5 V或3.3 V單電源供電。工作溫度范圍為?40°C至+85°C。

每個OUTx輸出都是差分輸出,并包含兩個引腳:OUTx和OUTx。為簡單起見,術(shù)語OUTx是指包含這兩個引腳的功能輸出模塊。

應用

- 以太網(wǎng)線路卡、交換機和路由器

- 基帶單元

- SATA和PCI Express

- 低抖動、低相位噪聲時鐘產(chǎn)生

- 異步時鐘產(chǎn)生

特性 - 單通道、低相位噪聲、完全集成的VCO/小數(shù)N分頻PLL內(nèi)核

- VCO范圍:2375 MHz至2725 MHz

- 集成環(huán)路濾波器(需要單個外部電容)

- 2路差分、XTAL或單端參考輸入

- 參考監(jiān)控功能

- 自動冗余XTAL切換

- 最小瞬態(tài)、平滑切換

- 典型RMS抖動

- <0.3 ps(12 kHz至20 MHz,整數(shù)N分頻轉(zhuǎn)換)

- <0.5 ps(12 kHz至20 MHz,小數(shù)N分頻轉(zhuǎn)換)

- 輸入頻率

- 8 kHz、1.544 MHz、2.048 MHz和10 MHz至325 MHz

- 通過引腳短接實現(xiàn)預設(shè)頻率轉(zhuǎn)換(PPRx)

- 采用25 MHz輸入?yún)⒖?

- 24.576 MHz、25 MHz、33.33 MHz、50 MHz、70.656 MHz、100 MHz、125 MHz、148.5 MHz、156.25 MHz、161.1328 MHz、312.5 MHz、322.2656 MHz、625 MHz或644.5313 MHz

- 采用19.44 MHz輸入?yún)⒖?

- 50 MHz、100 MHz、125 MHz、156.25 MHz、161.1328 MHz或644.5313 MHz

- 采用30.72 MHz輸入?yún)⒖?

- 25 MHz、50 MHz、100 MHz、125 MHz或156.25 MHz

- 采用25 MHz輸入?yún)⒖?

- 單通道、完全集成的通用型VCO/整數(shù)N分頻PLL內(nèi)核

- VCO范圍:750 MHz至825 MHz

- 集成環(huán)路濾波器

- 獨立重復參考輸入或采用小數(shù)N分頻PLL有效參考輸入工作

- 輸入頻率:25 MHz

- 通過引腳短接實現(xiàn)預設(shè)頻率轉(zhuǎn)換(PPRx)

- 25 MHz、33.33 MHz、50 MHz、66.67 MHz、100 MHz、133.33 MHz、200 MHz或400 MHz

- 多達3路基準時鐘輸出

- 11對可配置差分輸出

- 輸出驅(qū)動格式

- 3路輸出:HSTL、LVDS、HCSL、1.8 V CMOS、2.5 V/3.3 V CMOS

- 8路輸出:HSTL、LVDS或1.8 V CMOS

- 輸出驅(qū)動格式

- 2.5 V或3.3 V單電源供電

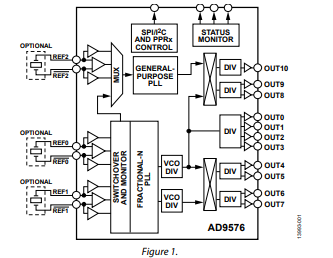

框圖

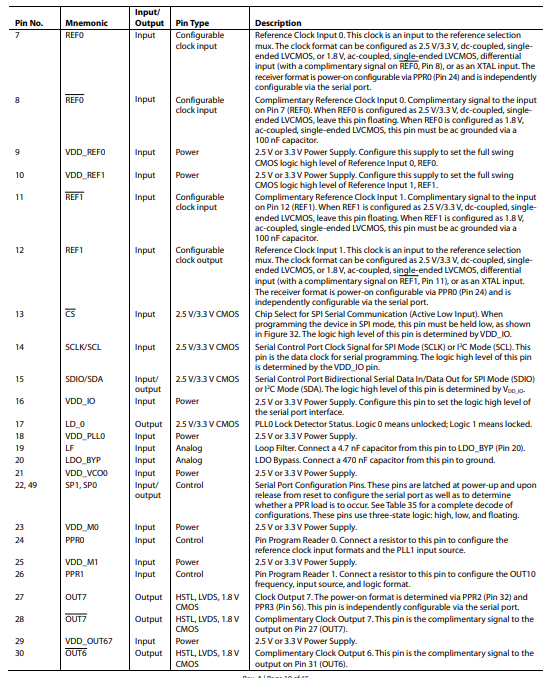

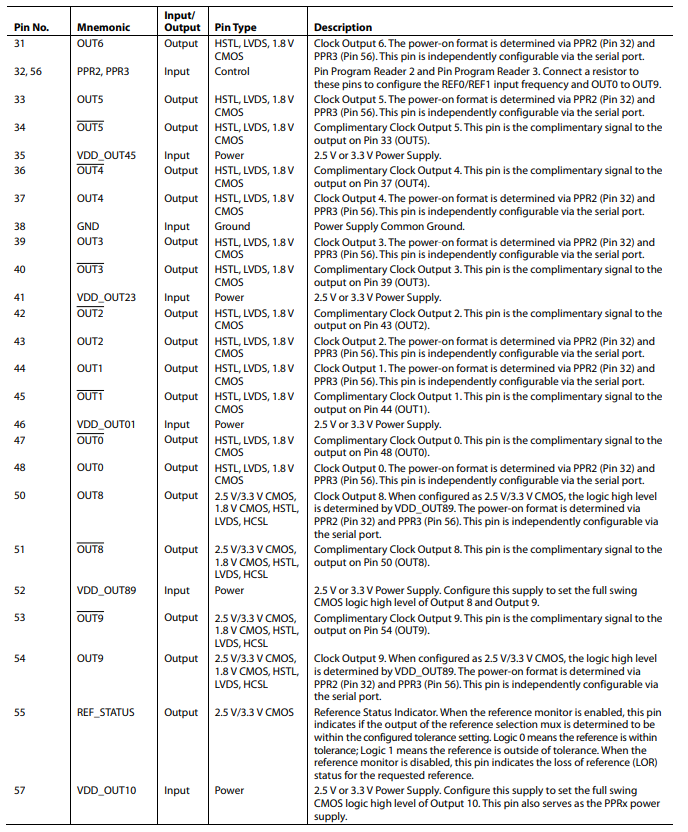

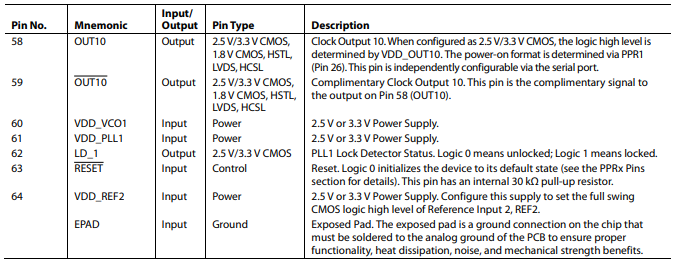

引腳配置描述

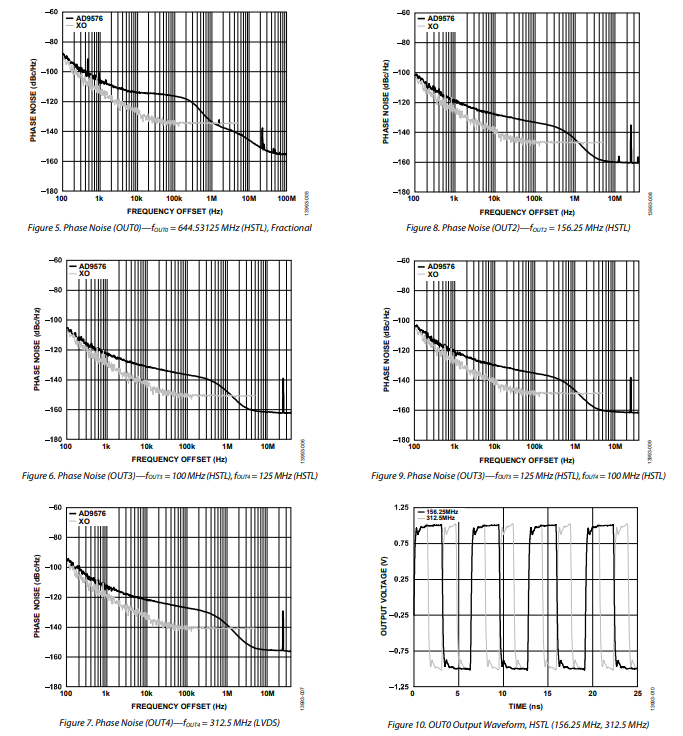

典型性能特征

操作理論

概述

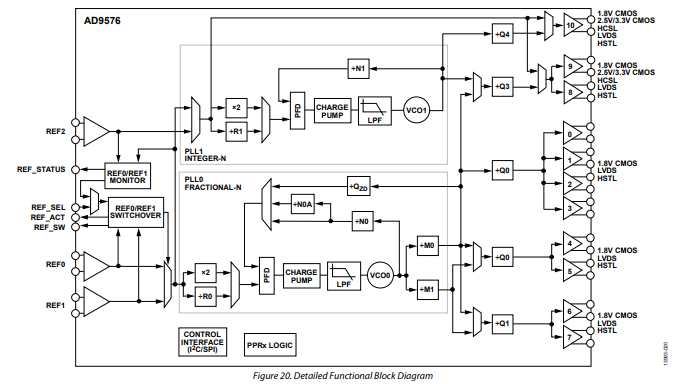

圖20展示了AD9576的框圖。AD9576采用2.5V或3.3V單電源供電,是一款完全可編程、隨時可用的雙輸出時鐘芯片,通過串行端口接口(SPI)進行控制。兩個并行通道分別由一個高性能分數(shù)N型鎖相環(huán)(PLL0)和一個通用整數(shù)N型鎖相環(huán)(PLL1)構(gòu)成。

AD9576有三個參考輸入(REF0至REF2)。每個輸入接收器都支持差分或單端輸入配置。REF0和REF1驅(qū)動參考切換多路復用器(mux)。輸出多路復用器的輸出選擇REF0或REF1來驅(qū)動PLL0的輸入,并作為PLL1參考選擇多路復用器的監(jiān)控時鐘,同時監(jiān)控參考切換多路復用器的輸出時鐘頻率。REF2支持8kHz、10MHz、19.44MHz、25MHz和38.88MHz的頻率,而REF0和REF1支持8kHz、1.544MHz、2.048MHz、10MHz至325MHz的頻率。不過,PLL1相位和PFD頻率限制為25MHz,50MHz是唯一允許作為PLL1輸入的參考頻率。

AD9576提供多達11個輸出通道時鐘(OUT0至OUT10)。OUT0至OUT7由PLL0驅(qū)動,分為三組:OUT0至OUT3、OUT4和OUT5、OUT6和OUT7 。每組中的每個輸出可單獨配置,但會生成相同的輸出頻率。這些輸出支持LVDS、HSTL或1.8V LVCMOS輸出格式。

OUT8和OUT9有三個潛在的時鐘源:PLL1參考選擇多路復用器的輸出、PLL0的輸出或PLL1的輸出。這些輸出可單獨配置,但必須共享相同的時鐘源,因此也具有相同的輸出頻率。OUT10由PLL1的輸出或參考選擇多路復用器的輸出驅(qū)動。這三個輸出支持LVDS、HSTL、HCSL、1.8V CMOS和2.5V/3.3V CMOS(擺幅由電源電平?jīng)Q定)輸出格式。

參考輸入

AD9576具有靈活的PLL參考輸入電路,提供三種工作模式:單端輸入、完全差分輸入或外接晶體輸入。REF0、REF1和REF2輸入接收器的工作模式可通過PPR0引腳或寄存器0x080和寄存器0x081(見表45)進行選擇和控制。寄存器0x080和寄存器0x081允許REF0和REF1的工作模式完全獨立于參考輸入。

-

發(fā)生器

+關(guān)注

關(guān)注

4文章

1429瀏覽量

64587 -

pll

+關(guān)注

關(guān)注

6文章

981瀏覽量

138153 -

時鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

306瀏覽量

70052

發(fā)布評論請先 登錄

用于評估AD9576時鐘倍頻器異步時鐘發(fā)生器的評估板AD9576/PCBZ

評估低抖動PLL時鐘發(fā)生器的電源噪聲抑制性能

AD9576 雙通道PLL、異步時鐘發(fā)生器

AD9576:雙鎖相環(huán)異步時鐘發(fā)生器數(shù)據(jù)表

時鐘發(fā)生器由哪些部分組成?鎖相環(huán)pll的特點是什么?

PLL1705/PLL1706雙通道PLL多時鐘發(fā)生器數(shù)據(jù)表

PLL1707/PLL1708 3.3V雙通道PLL多時鐘發(fā)生器數(shù)據(jù)表

CDCM9102低噪聲雙通道100MHz時鐘發(fā)生器數(shù)據(jù)表

AD9576雙通道PLL、異步時鐘發(fā)生器技術(shù)手冊

AD9576雙通道PLL、異步時鐘發(fā)生器技術(shù)手冊

評論