在 2.5D 和 3D-IC 中,準(zhǔn)確預(yù)測(cè)熱完整性變得越來(lái)越困難,從而產(chǎn)生了一連串的問(wèn)題,這些問(wèn)題可能會(huì)影響從系統(tǒng)行為到現(xiàn)場(chǎng)可靠性的方方面面。

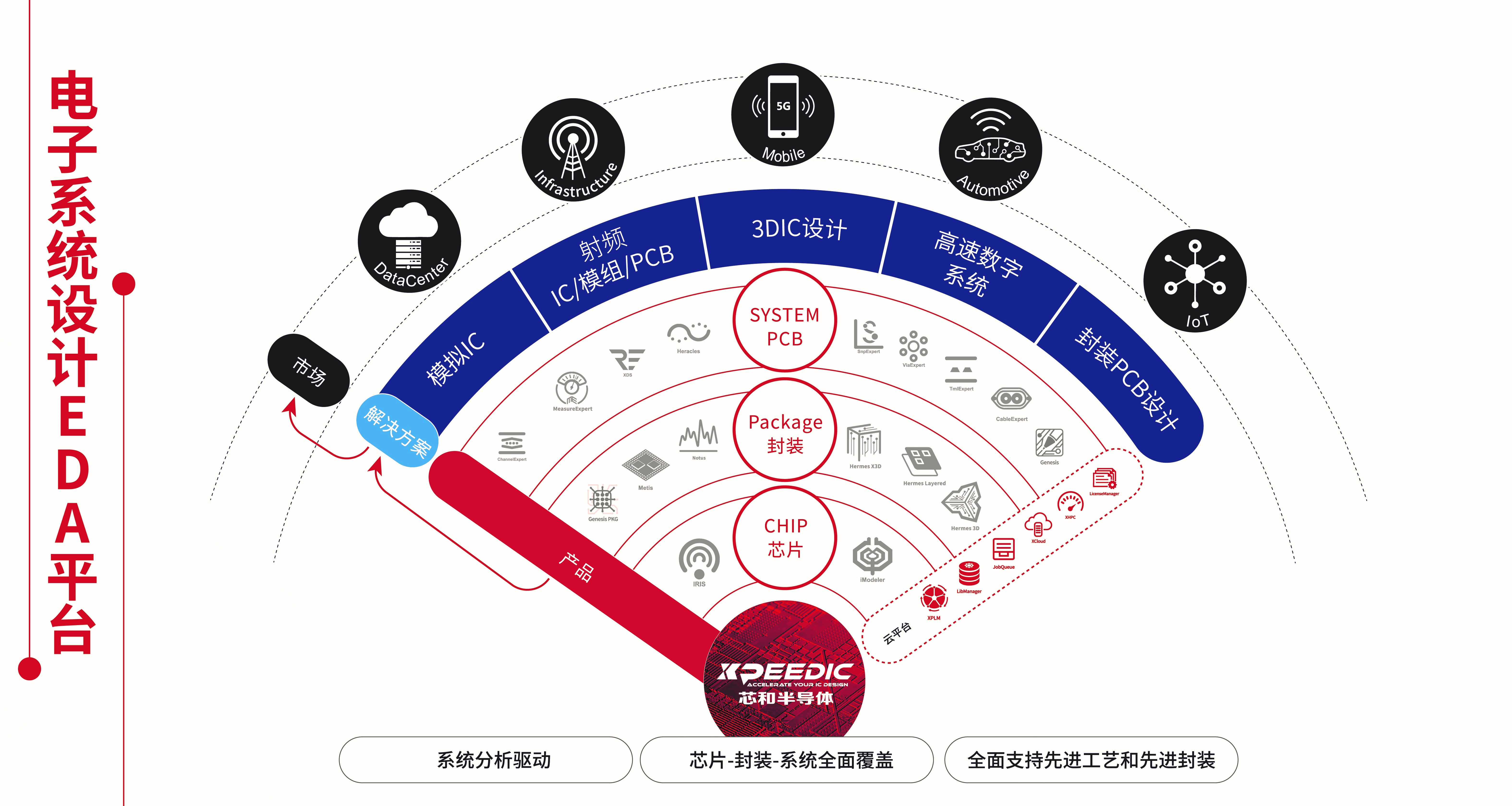

在過(guò)去的十年中,硅中介層技術(shù)已經(jīng)從簡(jiǎn)單的互連發(fā)展成為異構(gòu)集成的關(guān)鍵推動(dòng)因素。如今的中介層可能包含數(shù)十個(gè)芯片或小芯片,具有數(shù)百萬(wàn)個(gè)連接,并且對(duì)性能、功耗和面積的要求不斷提高。事實(shí)上,在面積大于 2,000 mm2 的中介層上看到異構(gòu)集成設(shè)計(jì)的情況并不少見(jiàn),系統(tǒng)功耗為 600 瓦,并且需要非常高的 I/O 帶寬。有了這種能力,熱完整性現(xiàn)在是一個(gè)首要問(wèn)題,這使得高信心地按計(jì)劃簽字變得更加困難。

有許多工具可用于理解和模擬異質(zhì)硅中介層設(shè)計(jì)中的熱效應(yīng),但目前大多數(shù)工具都是互不關(guān)聯(lián)的。這里的工作正在進(jìn)行中,但這不是一個(gè)簡(jiǎn)單的解決方案。并不總是很清楚這些工具應(yīng)該做什么,以及所有部分如何組合在一起。

“人們面臨的普遍挑戰(zhàn)是從這樣一種想法開(kāi)始的,‘讓我們假設(shè)這些東西是小板子。我們將永遠(yuǎn)應(yīng)用我們?cè)诎寮?jí)和封裝級(jí)應(yīng)用的相同技術(shù),我們只需縮小規(guī)模,它們就會(huì)起作用,“Synopsys 杰出架構(gòu)師 Rob Aitken 說(shuō)。“這是真的,但它有幾個(gè)新的維度。首先,現(xiàn)在做這件事的人與過(guò)去不同。以前,封裝和電路板工程師會(huì)這樣做。現(xiàn)在,芯片人員也在研究它。

還有其他重大轉(zhuǎn)變。“當(dāng)我們進(jìn)行這些 3D 裝配時(shí),重要的是要記住,我們正在跨越過(guò)去的領(lǐng)域,”Siemens Digital Industries Software 的 Calibre 接口和 EM/IR 產(chǎn)品管理高級(jí)總監(jiān) Joseph Davis 說(shuō)。“曾經(jīng)有芯片人會(huì)把芯片放在一個(gè)包裝里。然后我們有系統(tǒng)級(jí)封裝和 MCM 選項(xiàng)。其中很多界限已經(jīng)模糊不清。那么誰(shuí)擁有什么呢?有些包裝人員正在做包裝和系統(tǒng)仿真。對(duì)他們來(lái)說(shuō),整個(gè)芯片都有一個(gè)溫度,所以分辨率是厘米大小的,用于觀(guān)察電路板上或外殼內(nèi)部的散熱情況。然后是 IC 團(tuán)隊(duì),他們現(xiàn)在不再只有一張 IC。有一堆IC粘在一起。這個(gè) IC 團(tuán)隊(duì)以微米的分辨率來(lái)研究事物。他們需要知道整個(gè)事情的分布情況,等等。解決方案存在挑戰(zhàn)。但實(shí)際上,物理和技術(shù)問(wèn)題是這里最容易解決的部分。真正的問(wèn)題是,每當(dāng)你跨越組織邊界時(shí),你就會(huì)遇到一個(gè)真正的問(wèn)題。我們現(xiàn)在將多個(gè)芯片組合在一起,有時(shí)來(lái)自不同的技術(shù),有時(shí)來(lái)自不同的鑄造廠(chǎng)。即使在單個(gè)晶圓代工廠(chǎng)內(nèi),每個(gè)芯片組都是獨(dú)一無(wú)二的。沒(méi)有一個(gè)過(guò)程可以將所有這些信息都導(dǎo)入到工具中。

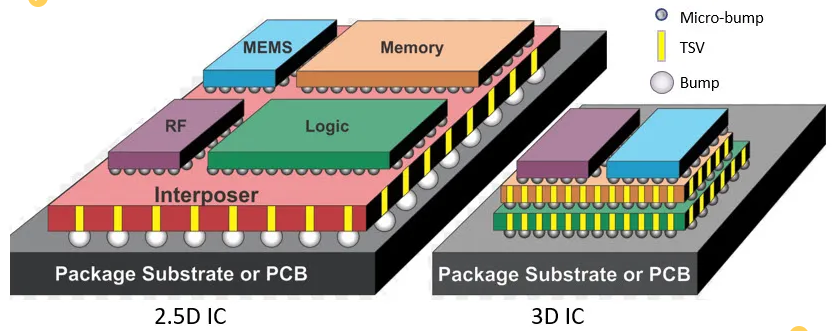

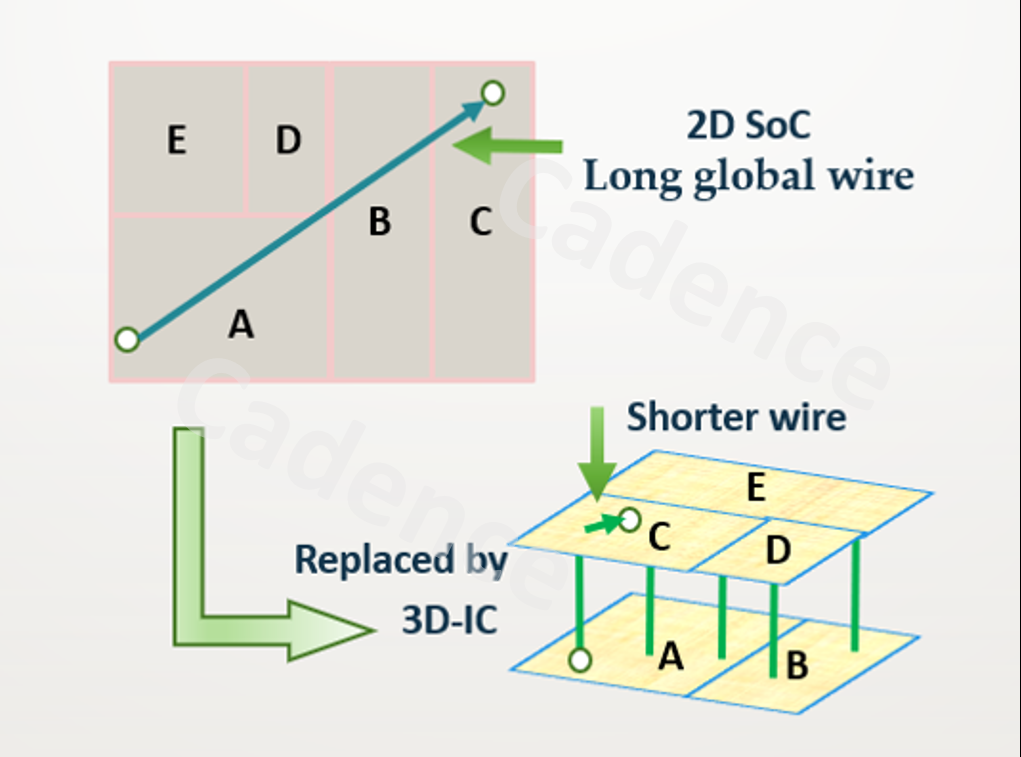

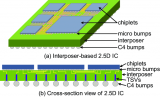

圖 1:使用中介層、凸塊、微凸塊和硅通孔的高級(jí)封裝。來(lái)源:西門(mén)子

為了實(shí)現(xiàn)這一目標(biāo),各方之間必須進(jìn)行溝通——芯片設(shè)計(jì)公司、EDA工具供應(yīng)商、代工廠(chǎng)和封裝公司。

“即使是一家鑄造廠(chǎng),我們也必須弄清楚所有需要進(jìn)來(lái)的東西,并準(zhǔn)備好所有的東西來(lái)完成工作,”戴維斯說(shuō)。“然后是包裝和系統(tǒng)人員,他們以毫米為單位思考。因此,有兩個(gè)截然不同的用戶(hù)群,每個(gè)用戶(hù)群都有不同的分辨率。

并且有不同的間距和互連。“特別是對(duì)于硅中介層,你正在處理一種不同的材料,”Synopsys的Aitken說(shuō)。“電路板或有機(jī)基板在材料上是相似的,因此人們過(guò)去在電路板中擁有的所有做法都是保持一切平衡并構(gòu)建測(cè)試車(chē)輛來(lái)測(cè)試該系統(tǒng)的極限。如果這些都有效,那就太好了,但沒(méi)有人能確定它們?cè)诙啻蟪潭壬掀鹱饔谩N锢韺W(xué)就是物理學(xué),但它會(huì)改變。如果你不小心,曾經(jīng)是二階效果的東西可能會(huì)變成一階效果。了解它的工作方式和地點(diǎn)很重要,即使你談?wù)摰氖菙?shù)學(xué)模型。

改變起點(diǎn)

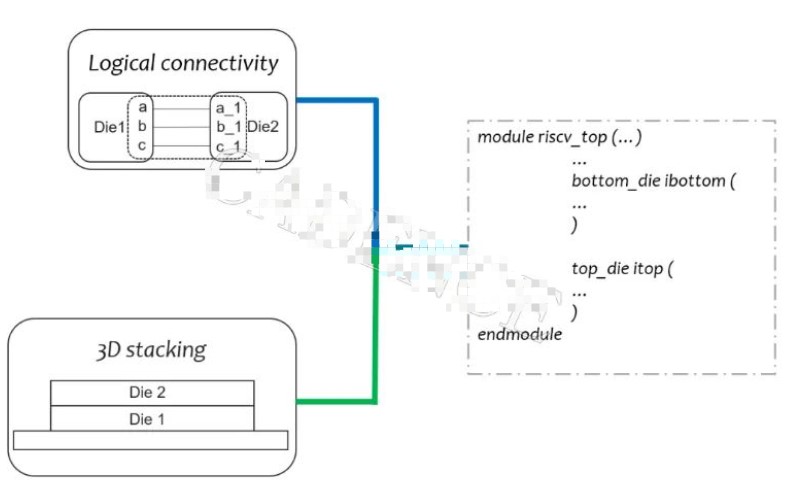

一個(gè)典型的異構(gòu)集成系統(tǒng)是一步一步建立起來(lái)的。

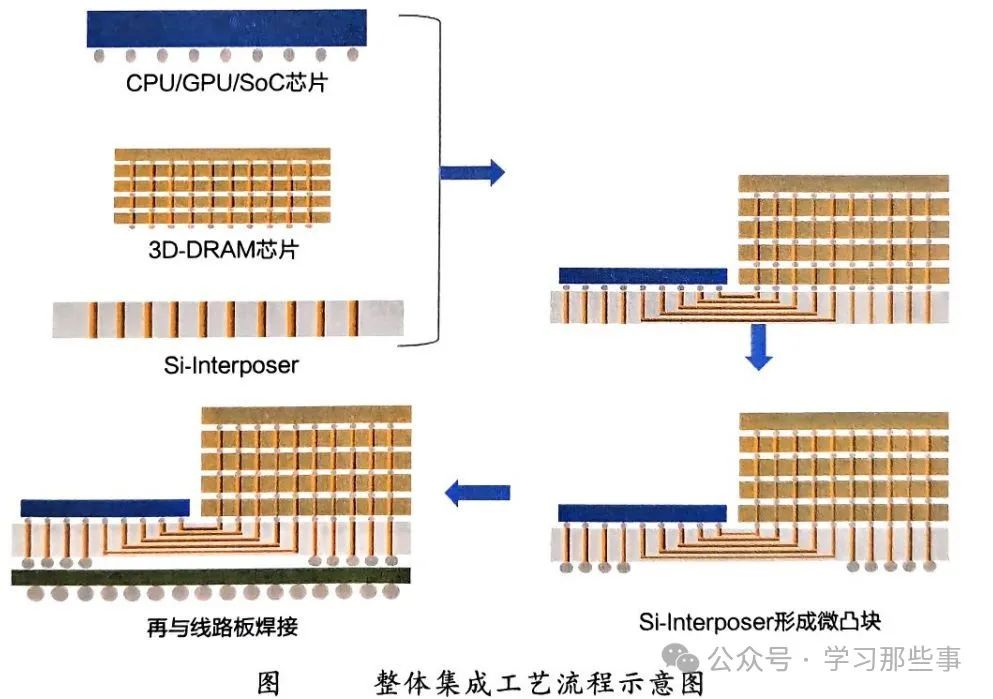

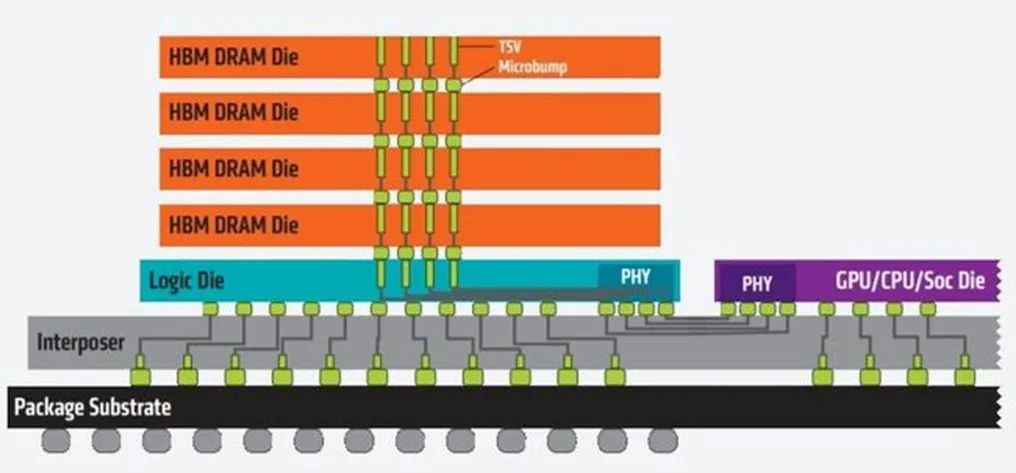

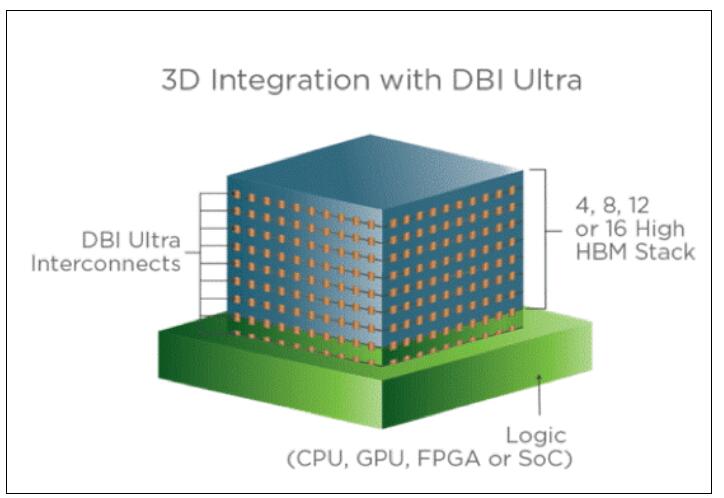

Ansys首席產(chǎn)品經(jīng)理Lang Lin表示:“從系統(tǒng)的封裝基板開(kāi)始,我們實(shí)際上將中介層安裝在其頂部,并連接數(shù)十萬(wàn)個(gè)凸塊。“根據(jù)設(shè)計(jì)集成計(jì)劃,設(shè)計(jì)人員會(huì)直接在中介層頂部添加幾個(gè)芯片或小芯片。一些芯片通過(guò)微凸塊或銅對(duì)銅連接連接,而其他一些芯片可以以 3D 方式進(jìn)一步堆疊。由于這種集成,中介層的作用是可靠地連接數(shù)百萬(wàn)個(gè)這樣的微凸塊或銅對(duì)銅連接,以便整個(gè)系統(tǒng)能夠在現(xiàn)場(chǎng)生存。

這通常被稱(chēng)為芯片封裝系統(tǒng)。中介層是一個(gè)橋梁,包含所有這些組件的供電網(wǎng)絡(luò)。“它還為所有芯片和芯片提供電源,并承載整個(gè)芯片和芯片,”Lin說(shuō)。“但現(xiàn)在安裝在頂部的小芯片消耗大量功率,這可能會(huì)導(dǎo)致電源完整性問(wèn)題。在現(xiàn)場(chǎng)工作時(shí),這些也會(huì)產(chǎn)生大量的熱量,因此現(xiàn)在 IC 有可能由于熱完整性問(wèn)題而燒毀相鄰的 IC。

簡(jiǎn)而言之,異構(gòu)集成會(huì)導(dǎo)致電源和熱完整性問(wèn)題,甚至更多。

“如果你有具有高帶寬內(nèi)存的3D堆疊芯片,電源和熱量問(wèn)題也可能導(dǎo)致嚴(yán)重的信號(hào)完整性問(wèn)題,”他說(shuō)。“這意味著所有這些問(wèn)題都在異構(gòu)集成系統(tǒng)中匯集在一起。設(shè)計(jì)人員在確保成功供電、成功散熱以及信號(hào)完整性不受影響方面發(fā)揮著重要作用。

對(duì)基于中介層的異構(gòu)設(shè)計(jì)進(jìn)行建模會(huì)引發(fā)有關(guān)模型完整性的問(wèn)題,因?yàn)樯婕暗淖兞刻嗔恕!澳慵僭O(shè)在某些條件下,例如,’一種材料相對(duì)于另一種材料的偏轉(zhuǎn)是線(xiàn)性的。然后你會(huì)說(shuō),‘嗯,實(shí)際上,在其他一些條件下,它是二次的。但二次模型要復(fù)雜得多。哪一個(gè)是正確的選擇?人們?nèi)栽谠噲D弄清楚答案是什么,以及你需要關(guān)心多少。

這很大程度上是抽象級(jí)別的函數(shù)。Davis指出,所有這些熱方面都可以通過(guò)非常粗略的建模和平均值來(lái)解決。“隨著新技術(shù)的出現(xiàn)以及這些技術(shù)的混合,我們?cè)谙到y(tǒng)中有很多非常好的絕緣體,”他說(shuō)。“當(dāng)我們轉(zhuǎn)向finFET時(shí),情況變得更糟。人們開(kāi)始說(shuō),’供暖問(wèn)題要嚴(yán)重得多。這是為什么呢?這是因?yàn)槭褂闷矫?a target="_blank">晶體管時(shí),所有的熱量都是在硅中產(chǎn)生的。塊狀硅是一種相當(dāng)不錯(cuò)的熱導(dǎo)體。它的導(dǎo)熱系數(shù)約為150。使用鰭片,你把晶體管放在上面,它被二氧化硅隔離,這是一種非常好的絕緣體。在那里,導(dǎo)熱系數(shù)為 1.4,因此為 100 倍。但是等一下。我剛剛把我的熱晶體管包在玻璃枕頭里?我該怎么處理這些熱量?我必須有辦法把它弄出來(lái)。這是通過(guò) TSV 等完成的。此外,我們可以對(duì)這些東西進(jìn)行建模。我們每天通過(guò)模擬和 EM/IR 對(duì)比熱成像更復(fù)雜的事情進(jìn)行建模。我們有能力,是的。但是,將所有數(shù)據(jù)放在一起是一個(gè)真正的問(wèn)題。系統(tǒng)和系統(tǒng)分辨率不是電子產(chǎn)品,而是工業(yè),是最大的問(wèn)題。

艾特肯說(shuō),這有兩個(gè)方面。“有一個(gè)方面是,‘我有一個(gè)系統(tǒng),我有一堆方程,我將用于對(duì)系統(tǒng)進(jìn)行建模,我有實(shí)現(xiàn)這些方程的工具。然后我得到輸出。輸入部分也非常重要,因?yàn)樗械镊蛔佣疾灰粯印K胁牧峡赡苈杂胁煌4送猓ぷ髫?fù)載是不同的,有時(shí)是未知的,所以你要處理的是我們一直在封裝上考慮的散熱問(wèn)題,以及我們一直在芯片上考慮的散熱問(wèn)題,但現(xiàn)在它們都合并在一起,不能被視為獨(dú)立的。這導(dǎo)致當(dāng)你把這些東西放在一起時(shí),你需要去做盡可能多的分析,但也需要監(jiān)控你在構(gòu)建它時(shí)發(fā)生了什么,以確保你的假設(shè)繼續(xù)成立。所以你有一些東西說(shuō),’哦,我們?cè)谶@里升溫。這很糟糕。讓我們放慢腳步。

了解熱流至關(guān)重要。熱量從物體較熱的一端移動(dòng)到較冷的一端,但并不總是一致的。“熱傳導(dǎo)的概念相當(dāng)容易理解,”Ansys的Lin說(shuō),“如果你從工程101中了解歐姆定律,你就知道你可以為系統(tǒng)的熱傳導(dǎo)路徑模擬具有等效熱阻的物體。給定一個(gè)特定的功率耗散值作為該系統(tǒng)的散熱器,你可以很容易地求解傳導(dǎo)路徑兩端之間的溫差。傅立葉熱傳導(dǎo)定律描述了系統(tǒng)如何散熱,以及散熱器如何影響整個(gè)系統(tǒng)的溫差。

通過(guò)硅中介層映射傅里葉定律更為復(fù)雜。“假設(shè)一個(gè)小芯片中有兩個(gè)熱源,”Lin說(shuō)。“小芯片消耗了這個(gè)硅系統(tǒng)的功率,而中介層安裝在封裝的頂部。系統(tǒng)中總共可能有四個(gè)不同的組件或?qū)ο蟆N覀兛梢詫?duì)四個(gè)分量的熱阻進(jìn)行建模。鑒于兩種小芯片正在加熱系統(tǒng),我們有兩個(gè)Q(熱流)源,它們將熱量注入熱傳導(dǎo)路徑。

解決這個(gè)問(wèn)題可以幫助設(shè)計(jì)人員了解系統(tǒng)各組件之間的溫差,進(jìn)而更好地了解溫度分布。但Lin說(shuō),這個(gè)模型不夠準(zhǔn)確,因?yàn)槊總€(gè)組件只有一個(gè)等效的熱阻。“熱阻實(shí)際上很大程度上取決于整個(gè)物體的材料特性。有限元分析方法可用于以數(shù)學(xué)方式表示具有自身材料屬性的物理組件或系統(tǒng),以及所有表面的邊界條件。網(wǎng)格劃分技術(shù)用于將此 IC 布局幾何形狀或?qū)ο筠D(zhuǎn)換為可識(shí)別的元素。可以使用兩種不同的網(wǎng)格方法對(duì)整個(gè)IC布局進(jìn)行建模,并且使用所有網(wǎng)格單元,我們可以以3D方式求解系統(tǒng)所有單元之間的傳熱規(guī)律。

這也有助于解決溫度分布問(wèn)題,這是一個(gè)更準(zhǔn)確的熱模型的現(xiàn)實(shí)問(wèn)題。

在談到這種網(wǎng)格劃分如何影響求解熱傳導(dǎo)的準(zhǔn)確性時(shí),Lin表示,網(wǎng)格劃分技術(shù)需要不斷改進(jìn),這是具有挑戰(zhàn)性的,因?yàn)閺呐f的SoC技術(shù)到最新的2.5D或3D-IC技術(shù),系統(tǒng)已經(jīng)變得更大。這些復(fù)雜的系統(tǒng)中包含數(shù)以萬(wàn)計(jì)的熱源。因此,網(wǎng)格劃分分辨率必須從厘米提高到微米,甚至可能達(dá)到納米。“我們需要一個(gè)更精細(xì)的解決方案,精確到集成芯片的子模塊級(jí)別,以便我們可以準(zhǔn)確地模擬熱傳導(dǎo)路徑。這是非常具有挑戰(zhàn)性的,但它是解決這種系統(tǒng)的熱節(jié)流問(wèn)題并確保沒(méi)有可靠性或熱完整性問(wèn)題的必要條件。

這使得整個(gè)分而治之的方法變得更加困難。Siemens Digital Industries Software 產(chǎn)品管理總監(jiān) John Ferguson 指出,從歷史上看,熱能是用電網(wǎng)方法完成的。“你把事情分成小方塊,然后你能走多少取決于你擁有的硬件,你有多少內(nèi)存,以及你愿意等待多長(zhǎng)時(shí)間才能得到答案。這些是你要掙扎的事情。但這種電網(wǎng)還有另一個(gè)挑戰(zhàn),因?yàn)闊岜旧砭褪且粋€(gè)問(wèn)題。重要的是,你要檢查一下,看看你是否確實(shí)有一個(gè)散熱問(wèn)題,除了重新設(shè)計(jì)之外,無(wú)法通過(guò)任何其他方式解決。

熱也會(huì)影響機(jī)械應(yīng)力和電遷移/紅外壓降。“現(xiàn)在你遇到這種情況,你必須確保你使用的網(wǎng)格可以在這些不同的東西上以某種方式對(duì)齊,”弗格森說(shuō)。“如果你要嘗試把它們加起來(lái),你可以讓一個(gè)窗口與另一個(gè)窗口重疊一半。你是怎么弄清楚這些東西的?這令人困惑。這仍然是一個(gè)很大的挑戰(zhàn)。該行業(yè)正在努力擺脫網(wǎng)格窗口方法,做一些更全面的事情,這意味著更多地從方程方法看待它,并從真正的物理學(xué)角度思考問(wèn)題。例如,溫度在哪里下降?正是由于這些原因,整個(gè)電網(wǎng)情況是該行業(yè)的一個(gè)挑戰(zhàn)。我如何知道要選擇的正確分辨率?它足夠準(zhǔn)確嗎?它會(huì)與我需要的所有其他內(nèi)容集成嗎?擺脫這種做法是重要的一步。

進(jìn)化變化

在這個(gè)領(lǐng)域,解決方案最終會(huì)是什么樣子還有待觀(guān)察。艾特肯指出,今天將進(jìn)行廣泛的實(shí)驗(yàn),并相信在某個(gè)時(shí)候,該行業(yè)將開(kāi)始合并。Ferguson說(shuō):“即使看一下軟件包選項(xiàng),過(guò)去也有相當(dāng)少的軟件包,而這些軟件包的特點(diǎn)是封裝供應(yīng)商。“所以你知道如果你把你的設(shè)計(jì)放在那里會(huì)發(fā)生什么。但現(xiàn)在有許多不同的封裝設(shè)計(jì),即使你只限于硅中介層。人們用它們做了很多事情,也有很多方法可以把它們放在一起。關(guān)于哪一個(gè)更好,并沒(méi)有真正達(dá)成任何共識(shí)。這意味著,如果您是制造商,現(xiàn)在您不僅要為每個(gè)客戶(hù),而且可能為每個(gè)設(shè)計(jì)提供定制服務(wù)。這又是在尋找,“讓我們盡可能地嘗試過(guò)度設(shè)計(jì),這樣我們才能認(rèn)為我們是安全的。但與此同時(shí),要小心。

隨著其他材料的引入,將添加新問(wèn)題。“你可以加入一些新材料,設(shè)計(jì)這些東西的人沒(méi)有很長(zhǎng)的歷史,”他說(shuō)。“根據(jù)你去的地方,你可以在文獻(xiàn)中找到一些關(guān)于其導(dǎo)熱性和抗拉強(qiáng)度的細(xì)節(jié)。但是,誰(shuí)在進(jìn)行測(cè)量以真正將這些東西撥入其中呢?他們改變了。你會(huì)得到一批氧化物,而下一批則有點(diǎn)不同。至少對(duì)于熱,我們將進(jìn)行無(wú)網(wǎng)格分析。但是我們?nèi)匀挥幸粋€(gè)問(wèn)題,那就是需要將其覆蓋在網(wǎng)格上,以便我將嘗試傳遞這些數(shù)據(jù)的另一件事,它需要在上游、下游以各種方式使用。歸根結(jié)底,有了這一切,我們行業(yè)一直以來(lái)的運(yùn)作方式就是我們保護(hù)它。我們說(shuō),‘他們說(shuō)這個(gè)東西對(duì)10%有好處。讓我們給一個(gè) 20% 的窗口來(lái)保證自己的安全。但這意味著你總是會(huì)把一些東西留在桌面上。

此外,早期做出決定也是一個(gè)挑戰(zhàn)。

“我們向架構(gòu)詢(xún)問(wèn)可以組合在一起的問(wèn)題,”西門(mén)子的戴維斯說(shuō)。“我有足夠大的包裹嗎?我有足夠大的散熱器嗎?我們行業(yè)一直以來(lái)的處理方式是預(yù)算和近似模型,因此,當(dāng)您在設(shè)計(jì)系統(tǒng)中處于更高或更早的位置時(shí),您就有了模型。有時(shí),模型只是一個(gè)近似值,“我認(rèn)為這個(gè)芯片會(huì)產(chǎn)生這個(gè)溫度,因此它會(huì)像這樣導(dǎo)電。但現(xiàn)在我們看到客戶(hù)問(wèn),’我建造了這個(gè)零件。我把它放在這個(gè)包里。新版本將有一些額外的驅(qū)動(dòng)程序,我希望它們會(huì)產(chǎn)生大量的熱量。我的包裹夠用嗎?在我開(kāi)始影響可靠性之前,我的散熱是否足夠?在你遇到其他問(wèn)題之前,必須回答這個(gè)問(wèn)題。電遷移是溫度的函數(shù),因此,如果溫度(指數(shù)函數(shù))比您預(yù)期的高 10 度,它可能會(huì)使您的壽命縮短 5 年。工程團(tuán)隊(duì)希望更早地做到這一點(diǎn),但他們沒(méi)有關(guān)于他們將使用的技術(shù)的信息,只能說(shuō),‘我們正在考慮這個(gè)問(wèn)題’。

結(jié)論

可以肯定的是,如果設(shè)計(jì)師意識(shí)到所有這些挑戰(zhàn),他們現(xiàn)在可以使用一些技術(shù)。但是,復(fù)雜的異構(gòu)設(shè)計(jì)中有很多元素,這對(duì)設(shè)計(jì)團(tuán)隊(duì)來(lái)說(shuō)是一個(gè)更大的挑戰(zhàn)。

“他們可以從設(shè)備層面應(yīng)用幾種不同的解決方案,”Lin說(shuō),“他們可以降低功耗,平衡功率密度,并可能巧妙地分配芯片和小芯片,使熱傳導(dǎo)路徑保持良好平衡,而不會(huì)引起任何高溫。在系統(tǒng)層面,我們看到很多冷卻解決方案說(shuō),“如果溫度太高,讓我們限制系統(tǒng),讓它不工作,讓它休眠。我們還可以做一些像熱管理、電液體冷卻和強(qiáng)制對(duì)流這樣的事情。所有這些我們已經(jīng)在系統(tǒng)生產(chǎn)中看到了。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論