日月光集團研發(fā)中心李長祺處長日前在世界半導體大會的先進封裝創(chuàng)新技術論壇上分享小芯片集成的2.5D/3D IC封裝技術,李處長表示, 全球數(shù)據(jù)總量在2025年將達到175ZB,大數(shù)據(jù)處理過程與傳輸及時化日趨重要。系統(tǒng)整合把傳輸?shù)木嚯x縮短,有效提升傳輸速率及能量效率。隨著硅光子學(Silicon Photonics)發(fā)展,光的傳輸頻寬級效率也變得越來越高,把光整合至封裝形態(tài)是未來重要的發(fā)展趨勢。

李處長也強調,系統(tǒng)整合與SoC分拆是驅動先進封裝與小芯片Chiplet集成的關鍵因素,在系統(tǒng)整合中,內存、電源與光學整合是主要的發(fā)展機會,SoC分拆中I/O分拆與SRAM分拆最為重要。小芯片Chiplet集成技術中細間距互連、大規(guī)模整合、電力傳輸以及散熱等都是未來主要發(fā)展方向。

2.5D/3D IC封裝特性與異質整合

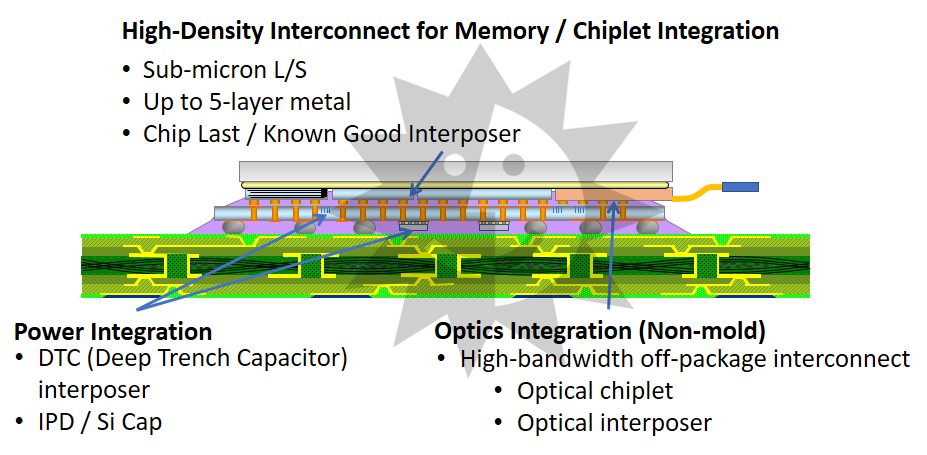

異質整合需要通過先進封裝提升系統(tǒng)性能,以2.5D/3D IC封裝為例,可提供用于存儲器與小芯片集成的高密度互連,例如提供Sub-micron的線寬與線距,或五層的互連,是良好的Interposer(中介層)。此外可通過DTC Interposer與IPD/Si Cap技術完成電源集成,通過高帶寬非封裝互連提供高性能的長距離資料傳輸。日月光目前與合作伙伴正在合作開發(fā)Optical Chiplet與Optical Interposer的技術,為進一步小型化提供可靠的解決方案。

內存集成發(fā)展趨勢

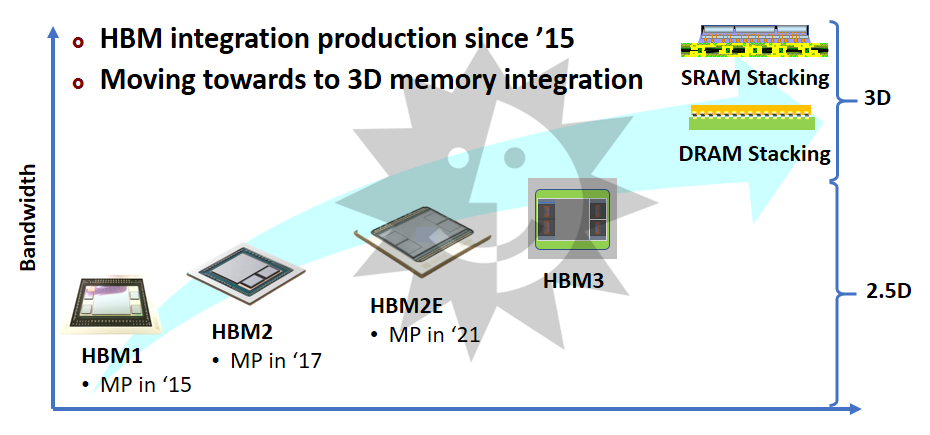

內存頻寬的需求越來越高,高頻寬內存的集成發(fā)展成為關鍵競爭力。內存集成未來主要發(fā)展趨勢有兩種,一種是整合HBM3提高頻寬,另一種是做3D整合及堆疊,如SRAM堆疊及DRAM堆疊。日月光率先在2015年量產(chǎn)HBM1整合的封裝,2017年HBM2也順利量產(chǎn),在2021年量產(chǎn)HBM2E,目前正朝著3D整合方向發(fā)展。

電源集成Si Cap發(fā)展趨勢

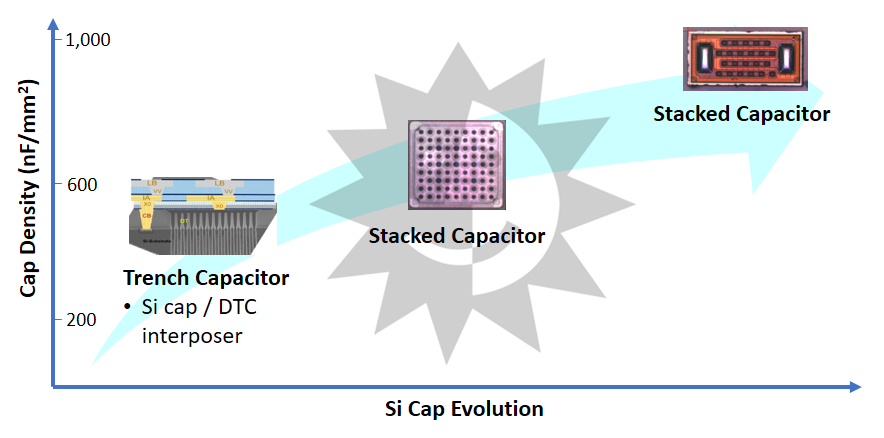

隨著電源功率越來越高,電容密度的要求也同步提高,因此電容整合的重要性尤為突出。日月光正在與合作伙伴共同開發(fā)不同的電容技術,例如應用在Si Cap及DTC Interposer上溝槽電容器(Trench Capacitor)以及電容密度更高的堆疊電容器(Stacked Capacitor),以滿足越來越高的電容密度需求。

光學集成發(fā)展趨勢

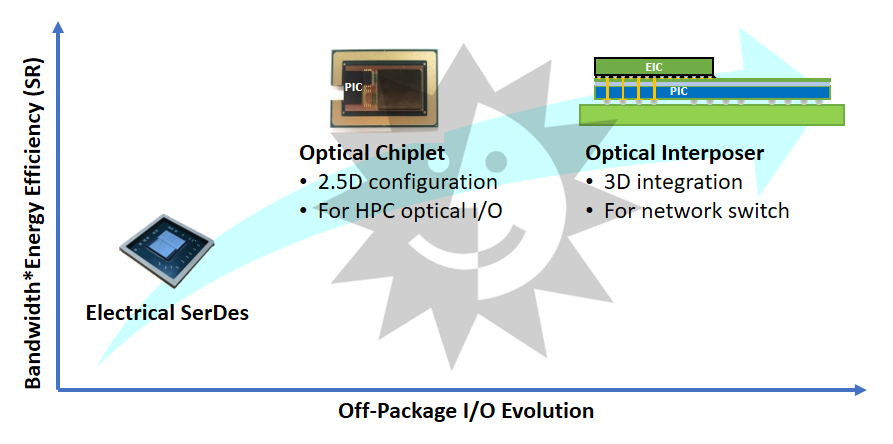

頻寬與能量效率問題是未來電的長距離傳輸主要瓶頸,因此光學整合成為重點發(fā)展趨勢之一。目前日月光與合作伙伴開發(fā)兩種不同的光整合技術,第一個是光學小芯片Chiplet技術,應用2.5D 硅中介層(Silicon Interposer)整合光學小芯片Chiplet以及SoC技術,以滿足最高的能量效率與最高的頻寬,如應用于高速運算光學I/O的要求。另一個發(fā)展趨勢是基于3D整合的光學中介層(Optical Interposer)技術,即電子IC在上面,光子IC在下面,這種整合方式可提供更高的頻寬級能量效率的需求,可應用于網(wǎng)絡交換機。

日月光持續(xù)開發(fā)不同的先進封裝如扇出型封裝Fan Out形態(tài)的 FOCoS、2.5D/3D IC封裝、混合鍵合Hybrid Bonding技術等,與產(chǎn)業(yè)鏈合作伙伴們共同研發(fā)合作,以滿足系統(tǒng)整合及小芯片Chiplet集成發(fā)展要求。

審核編輯:劉清

-

電容器

+關注

關注

64文章

6965瀏覽量

108167 -

soc

+關注

關注

40文章

4606瀏覽量

229705 -

DRAM芯片

+關注

關注

1文章

89瀏覽量

18925 -

IC封裝

+關注

關注

4文章

196瀏覽量

27701

原文標題:聚焦小芯片Chiplet集成的2.5D/3D IC 封裝技術

文章出處:【微信號:ASE_GROUP,微信公眾號:ASE日月光】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

臺積電如何為 HPC 與 AI 時代的 2.5D/3D 先進封裝重塑熱管理

先進封裝成破局,博通率先落地3.5D,6000mm2超大集成

淺談2D封裝,2.5D封裝,3D封裝各有什么區(qū)別?

Socionext推出3D芯片堆疊與5.5D封裝技術

3D封裝的優(yōu)勢、結構類型與特點

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

后摩爾時代破局者:物元半導體領航中國3D集成制造產(chǎn)業(yè)

分享一下小芯片集成的2.5D/3D IC封裝技術

分享一下小芯片集成的2.5D/3D IC封裝技術

評論