01引言:先進封裝設計的破局之路

隨著“后摩爾時代”的到來,芯粒(Chiplet)與 2.5D/3D 先進封裝技術正成為突破晶體管微縮瓶頸的關鍵路徑。通過異構集成將不同的芯片模塊化組合,依托2.5D/3D封裝實現高帶寬互連與低功耗協同,推動從芯片到系統級的性能飛躍。這為半導體技術發展帶來重大機遇,也對傳統設計方法構成全新挑戰。在實際設計中,您是否正面臨以下問題?

1先進封裝設計困境

芯片間互聯數量呈指數級增長,從芯片經通孔/Bump至基板的連線可達十幾萬根。手動布線作業量大,不僅耗時費力,還易因線路復雜導致視覺混淆與迭代困難。

2傳統版圖工具掣肘

大規模封裝數據輸入時,傳統版圖工具存在響應遲緩、操作卡頓等問題,直接影響設計效率。

3低效DFM需求處理困擾

面對Dummy填充、淚滴處理等 DFM(可制造性設計)需求,現有處理方式效率低下,無法滿足生成制造量產的版圖后處理需求。

4繁瑣的驗證流程

設計完成后,DRC/LVS 等物理驗證流程復雜,需多次迭代,耗費大量時間與精力,延長項目周期。

針對上述痛點,解決方案已正式推出。華大九天先進封裝版圖設計解決方案Empyrean Storm,作為一款具備革新意義的 EDA 工具,可直擊傳統封裝設計核心問題,顯著提升設計效率,推動先進封裝設計進入新階段!

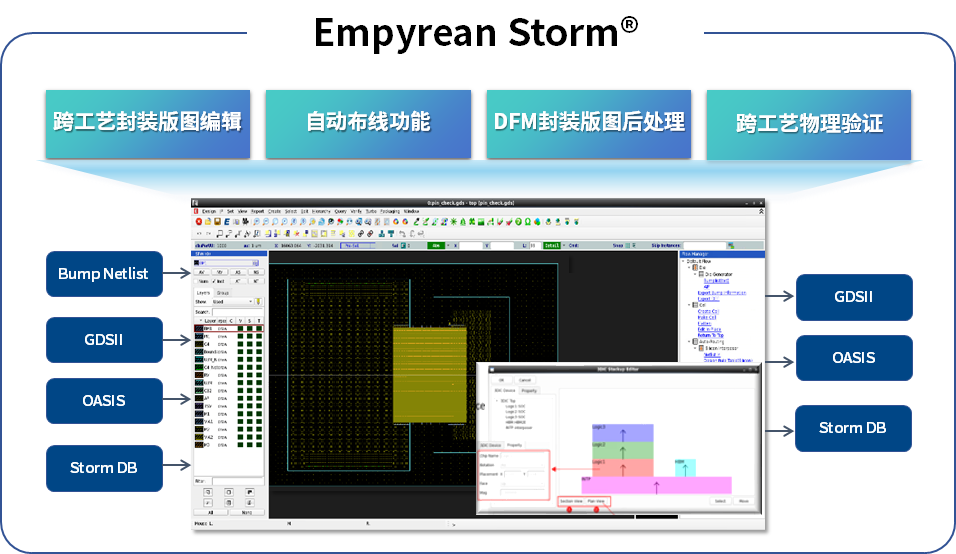

02什么是Empyrean Storm?

Empyrean Storm是一款專為先進封裝設計打造的具備自動布線與物理驗證的版圖平臺。它支持跨工藝封裝版圖數據導入與設計編輯,深度適配當下主流的硅基(Silicon Interposer)以及有機轉接板(Organic RDL)工藝,可實現 HBM和UCIe等通訊協議多芯片的大規模自動布線;同時能夠完成Dummy填充等保障量產的DFM版圖后處理,更是內置無縫集成的跨工藝物理驗證Argus,通過DRC/LVS等檢查確保版圖的正確性。憑借上述強大功能,Storm能夠輕松駕馭多芯片間大規模、高密度的互聯布線和復雜的Layout需求,以高效的平臺性能為先進封裝設計注入強勁動力,助力設計工作實現質的飛躍。

核心亮點一:

強大智能的自動布線功能

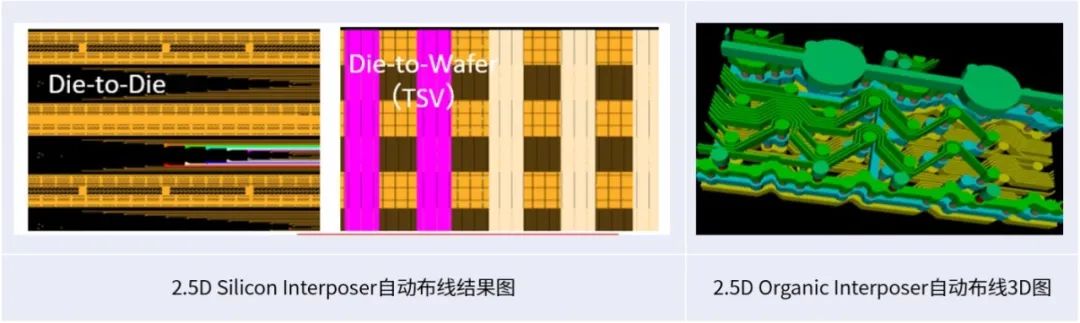

傳統芯粒設計中,復雜布線是一大難點。以2.5D中介板(Interposer)的跨層布線為例,HBM2/2E/3高帶寬存儲器是面向高性能計算HPC、AI加速等場景的堆疊式DRAM技術,通過2.5D/3D集成提供超高帶寬(如HBM3可達 819GB/s),但需通過硅中介層與處理器/SoC互聯,布線密度高、信號完整性要求嚴苛。UCle通用芯粒互聯接口標準,旨在實現不同工藝、廠商的Chiplet高效集成,支持高吞吐低延遲通信,但跨Die布線需協調時序、阻抗匹配,手動優化難度大。兩者均為2.5D封裝中的關鍵模塊,但手工布線需處理幾十萬根高密度互連線,易導致串擾、時序違例等問題,而Storm搭載的智能化自動化布線引擎,可通過簡單操作流程改變這一現狀,用戶僅需完成規則配置并觸發指令,即可啟動自動布線。其核心能力包括:

硅基中介層自動布線:依托智能算法支持從頂層Micro-Bump到底層C4 Bump的跨層布線,可高效完成多芯片間Die-to-Die、芯片到晶圓間Die-to-Wafer(含TSV硅通孔)的自動布線任務,精準規劃芯片間、晶圓級與裸片級混合互聯結構,保障信號傳輸穩定性。

有機中介層自動布線:通過優化垂直互連通道布局實現全局RDL高效布線,同時具備能夠滿足約束條件的電源網絡(PDN)版圖的自動布線功能。同時,為了更便捷地看到走線連接,Storm可生成三維布線圖,直觀呈現線路走向。

多樣化布線角度適配:兼容芯片式曼哈頓布線與PCB式135度布線模式,能夠精準匹配客戶工藝標準,確保布線效率與準確性。

核心亮點二:

為量產護航的DFM版圖后處理能力

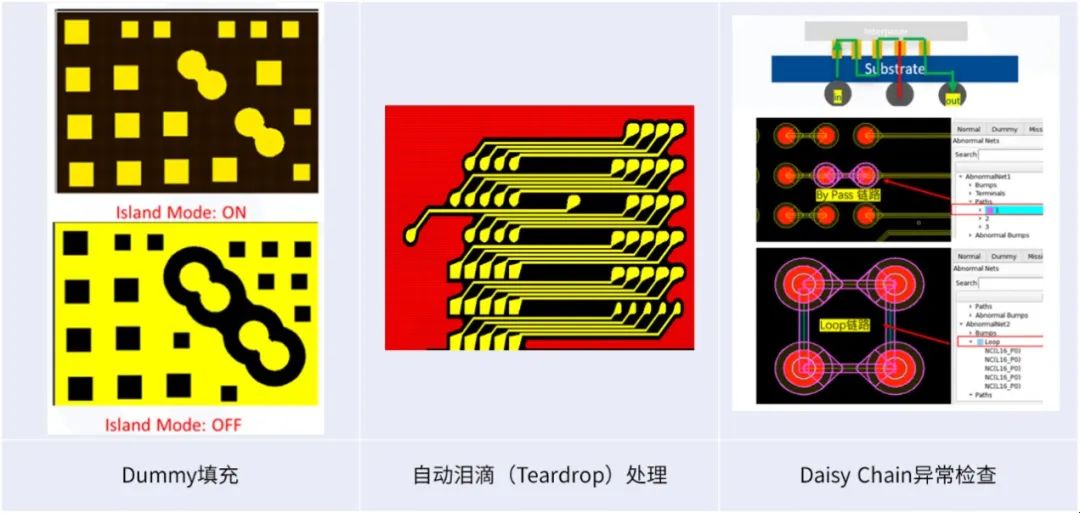

設計的最終目標是實現成功量產。Storm憑借完善的版圖后處理功能,可有效提升設計的可制造性(DFM),為芯粒量產提供有力支持,具體包括:

智能金屬啞元(Dummy)填充:能夠自動、快速完成大面積Dummy填充,且支持特殊形狀(例如Island不規則島狀)的填充。這一功能可解決工藝中的不均勻性問題,有助于提升晶圓制造的穩定性和芯片性能的一致性。

自動淚滴(Teardrop)處理:提供一鍵式操作,為焊盤和過孔精準添加淚滴,從而增強連接的可靠性,降低線路斷裂風險,進而提升產品良率。

封裝測試結構(Daisy Chain)模塊:可自動完成封裝測試結構的連接與分析,能夠識別封裝中Interposer、Substrate等結構的連接情況,分類展示Bumps、Terminals、Paths及Abnormal Bumps等信息。針對Bypass鏈路,可精準標記異常路徑;對于 Loop鏈路,能清晰羅列關聯節點,幫助工程師在芯片封裝設計階段快速定位異常并排查問題,提升設計可靠性。

核心亮點三:

不止于布線與后處理,更是一站式設計平臺

Storm并非單一的布線與后處理工具,而是先進封裝設計領域的綜合性平臺。其功能覆蓋設計全流程,可提升設計流暢度并推動流程優化,具體包括:

全功能版圖編輯:傳統EDA工具在導入多個GDSII文件時,會出現同圖層覆蓋問題,導致無法區分Die1,Die2,在異構集成場景中效率低下。Storm平臺可以支持多個GDSII/OASIS數據無損導入導出,創新性研發出針對封裝版圖的層次化(hierarchy)編輯設計功能,突破傳統工具僅支持扁平化(Flatten)封裝版圖編輯模式、難以快速批量修改封裝版圖的局限。同時Storm支持直觀形象的3D堆疊Stack顯示、編輯與快速查詢功能,形成完整的異構版圖集成解決方案。

實時分析與檢查:在沿用傳統2D操作習慣的基礎上,Storm平臺創新性地提供了多工藝節點跨芯片線網追蹤(Trace)功能,設計師通過點擊、拖拽等簡單操作,即可實現快速追蹤跨芯片關鍵線網走向,清晰呈現信號傳輸路徑,可在版圖繪制階段提前檢查信號連通性與短路風險,推動設計左移。此外,平臺具備封裝測試結構(Daisy Chain)異常檢查等功能,能在設計階段及時發現問題,降低后期修改成本。

無縫集成驗證工具:與華大九天物理驗證工具Empyrean Argus實現無縫集成,能夠提供快速的Online DRC以及開/短路檢查,也同時提供Signoff級別的DRC/LVS,覆蓋從設計到驗證的全流程,保障版圖正確性,縮短迭代周期,提升設計效率。

改版數據比對:通過同步視圖端口實現高效版本差異對比,借助雙版本同步透視可并列顯示改版前后的布局/GDS 視圖,自動高亮差異區域,支持跨工藝庫參數比對;點擊差異標記可即時跳轉至對應層級,實現變更點的快速識別與動態定位。

03Empyrean Storm 平臺帶來的價值

華大九天版圖設計解決方案Empyrean Storm平臺在先進封裝設計中優勢顯著。

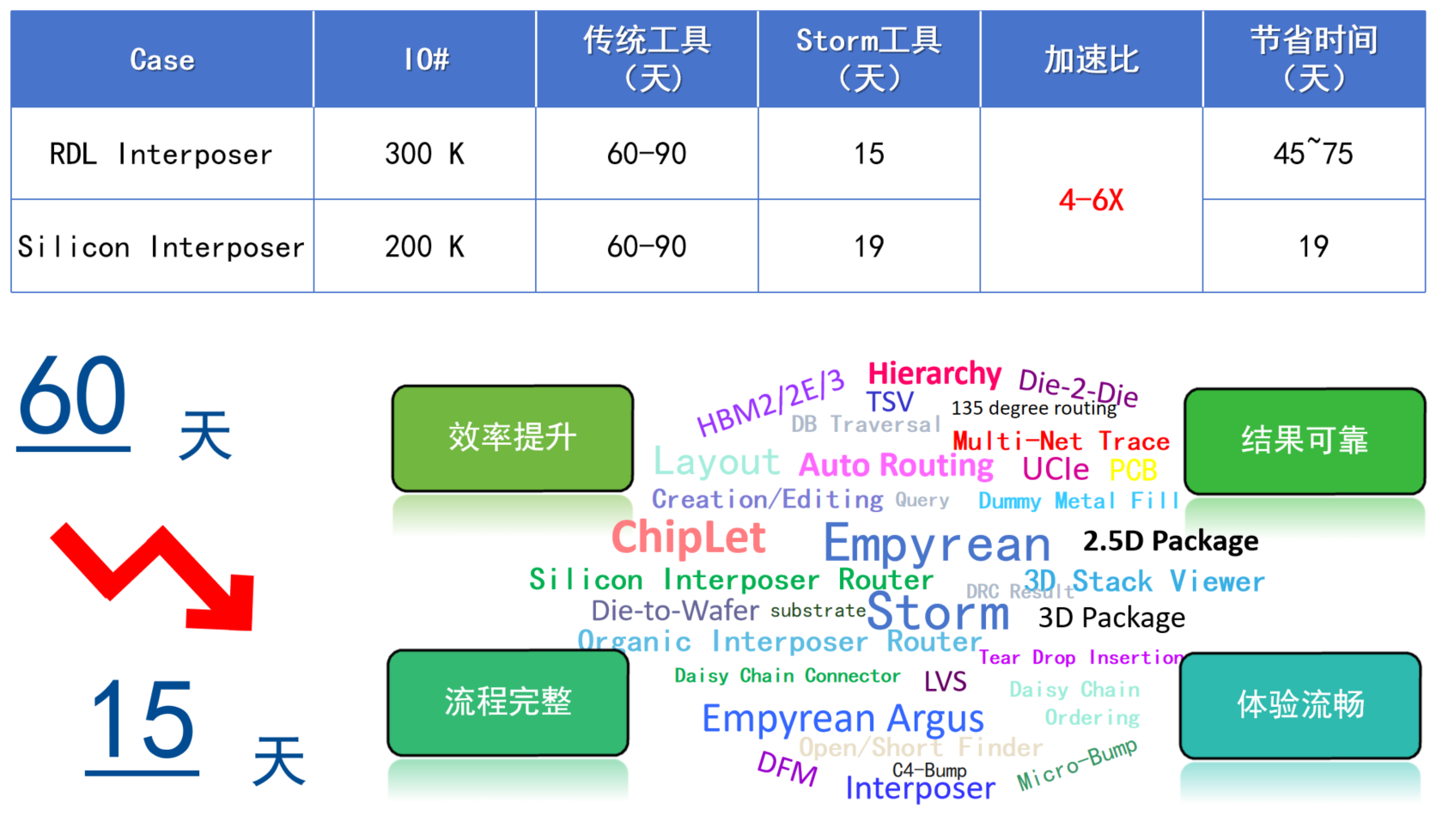

例如,在處理HBM2/2E/3與UCle等高速接口時,傳統工具需耗時約兩三月、60-90天之久,而Storm的自動布線引擎可在15天內完成IO數量高達200K的Micro-bumps與TSV跨層走線。該平臺能高效處理TSV布線、微凸點(Microbumps)連接及BGA球柵陣列布局,同時支持中介層+基板的物理驗證,并兼容CoWoS(Chip on Wafer on Substrate,晶圓基底封裝)架構。某客戶案例顯示,在完成工具參數Option設置后,自動布線功能僅需10分鐘即可完成1次設計迭代,顯著提升了反復修改的效率:“Storm有效解決了先進封裝的設計瓶頸,效率提升1-2個月”。

04結語

在先進封裝設計這一兼具機遇與挑戰的前沿領域,若持續使用落后設計工具,將直接影響效率提升與創新突破。Empyrean Storm 憑借卓越的自動布線核心引擎、一站式設計平臺的全面功能,以及保障量產的DFM特性,已成為頂尖設計公司的主流選擇。目前,多家大型設計公司已通過 Storm 完成完整的先進封裝版圖設計并成功流片,其強大的版圖處理能力也被眾多封測 OSAT 廠商納入標準流片TO(Tapeout流片)流程。風暴來襲,借助 Storm 平臺的全方位功能為集成電路產業賦能,在先進封裝創新賽道上提升競爭力,重塑全球半導體產業格局。

北京華大九天科技股份有限公司(簡稱“華大九天”)成立于2009年,一直聚焦于EDA工具的開發、銷售及相關服務業務,致力于成為全流程、全領域、全球領先的EDA提供商。

華大九天主要產品包括全定制設計平臺EDA工具系統、數字電路設計EDA工具、晶圓制造EDA工具、先進封裝設計EDA工具和3DIC設計EDA工具等軟件及相關技術服務。其中,全定制設計平臺EDA工具系統包括模擬電路設計全流程EDA工具系統、存儲電路設計全流程EDA工具系統、射頻電路設計全流程EDA工具系統和平板顯示電路設計全流程EDA工具系統;技術服務主要包括基礎IP、晶圓制造工程服務及其他相關服務。產品和服務主要應用于集成電路設計、制造及封裝領域。

華大九天總部位于北京,在南京、成都、深圳、上海、香港、廣州、北京亦莊、西安和天津等地設有全資子公司,在武漢、廈門、蘇州等地設有分支機構。

-

eda

+關注

關注

72文章

3122瀏覽量

183385 -

華大九天

+關注

關注

5文章

115瀏覽量

13932 -

chiplet

+關注

關注

6文章

497瀏覽量

13627 -

先進封裝

+關注

關注

2文章

552瀏覽量

1047 -

芯粒

+關注

關注

1文章

87瀏覽量

441

原文標題:全球首發!先進封裝設計平臺Storm橫空出世,Chiplet布線效率提升1-2月 !

文章出處:【微信號:華大九天,微信公眾號:華大九天】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

臺積電如何為 HPC 與 AI 時代的 2.5D/3D 先進封裝重塑熱管理

先進封裝時代,芯片測試面臨哪些新挑戰?

華大九天與西安電子科技大學簽署戰略合作協議

西門子Innovator3D IC異構集成平臺解決方案

2D、2.5D與3D封裝技術的區別與應用解析

華大九天與海光信息達成戰略合作

華大九天Argus 3D重塑3D IC全鏈路PV驗證新格局

淺談2D封裝,2.5D封裝,3D封裝各有什么區別?

華大九天新一代全定制IC設計平臺Empyrean Aether介紹

《電子發燒友電子設計周報》聚焦硬科技領域核心價值 第23期:2025.08.04--2025.08.08

華大九天“芯聚九天”系列活動助力集成電路產業蓬勃發展

多芯粒2.5D/3D集成技術研究現狀

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

評論