多年來,封裝技術并未受到大眾的廣泛關注。但是現在,尤其是在AI芯片的發展過程中,封裝技術發揮著至關重要的作用。2.5D封裝以其高帶寬、低功耗和高集成度的優勢,成為了AI芯片的理想封裝方案。

在2.5D封裝領域,英特爾的EMIB和臺積電的CoWoS是兩大明星技術。眾所周知,臺積電的CoWoS產能緊缺嚴重制約了AI芯片的發展,這正是英特爾EMIB技術可以彌補的地方。本文我們將以英特爾EMIB為例,深入解析2.5D封裝之所以能成為AI芯片的寵兒的原因。

為何EMIB是AI領域的理想選擇?

2.5D封裝并不是一個全新的概念,但它在AI芯片領域的應用卻煥發出了新的生命力。簡單來說,2.5D封裝是一種通過硅中介層(Silicon Interposer)或嵌入式橋接技術(如英特爾的EMIB)將多個芯片水平連接起來的技術。與傳統的2D封裝相比,它允許在單一封裝內集成更多功能單元,比如CPU、GPU、內存(HBM)和I/O模塊;而與復雜的3D堆疊相比,它又避免了過高的制造難度和熱管理挑戰。這種“不上不下的中間狀態”恰恰為AI芯片提供了完美的平衡。

AI芯片的一個顯著特點是需要高帶寬和低延遲的芯片間通信。例如,訓練一個深度學習模型時,GPU需要與高帶寬存儲器(HBM)快速交換數據,而傳統的封裝技術往往受限于互連帶寬和功耗。2.5D封裝通過在芯片間引入高密度互連通道,顯著提升了數據傳輸效率,同時保持了相對簡單的制造流程。這使得它特別適合AI加速器和數據中心處理器等高性能應用。

“我經常被問到一個問題:為什么EMIB是AI領域的理想選擇?是什么讓這項技術對這些應用如此適合?”英特爾先進系統封裝與測試事業部副總裁兼總經理Mark Gardner表示。他通過一張圖詳細解析了EMIB作為AI加速器理想封裝技術的優勢,并總結了EMIB的五大關鍵優勢:

第一,成本更低。EMIB采用小型硅橋連接芯片,一個晶圓上就能生產數千個橋接單元,極大提高了利用率。相比之下,傳統晶圓級封裝在制造復雜結構(如含12個HBM堆疊和多個光罩芯片的大型封裝)時,成品率低且浪費嚴重。而EMIB不僅提升了良率,還能在HBM數量增加時,展現出成本優勢的指數級增長。

第二,更高良率。與其他2.5D技術相比,EMIB減少了復雜的工藝步驟。傳統晶圓級封裝需要“芯片對晶圓”(Chip-on-Wafer)流程,涉及模具、凸點等多重工序,增加了出錯風險。EMIB簡化了這些步驟,自然帶來了更高的生產穩定性。

第三,更快生產周期。更少的工藝步驟不僅提升良率,還縮短了生產時間。與動輒數天的傳統流程不同,EMIB能將周期縮短數周。在AI市場瞬息萬變、上市時間至關重要的背景下,提前幾周拿到加電測試數據、硅片驗證數據對客戶意義重大。

第四,更強擴展性。EMIB將硅橋嵌入基板,而基板制造通常基于大型方形面板。這種設計大幅提高了基板利用率,特別適合需要集成更多HBM或復雜工作負載的大型封裝。對于AI客戶來說,這意味著更強的適應性和性能潛力。

第五,為客戶提供更多選擇。英特爾代工致力于為客戶提供多樣化的選項。市場上已有既定的行業解決方案,而EMIB技術為客戶提供了一種替代方案。在某些情況下,客戶可以選擇多源供應,也可以選擇單一來源,關鍵是EMIB為他們提供了靈活性和選擇權。EMIB技術已經在生產中應用了近十年,擁有成熟的供應鏈。這些因素共同構成了EMIB作為AI領域(尤其是加速器)理想平臺的原因。

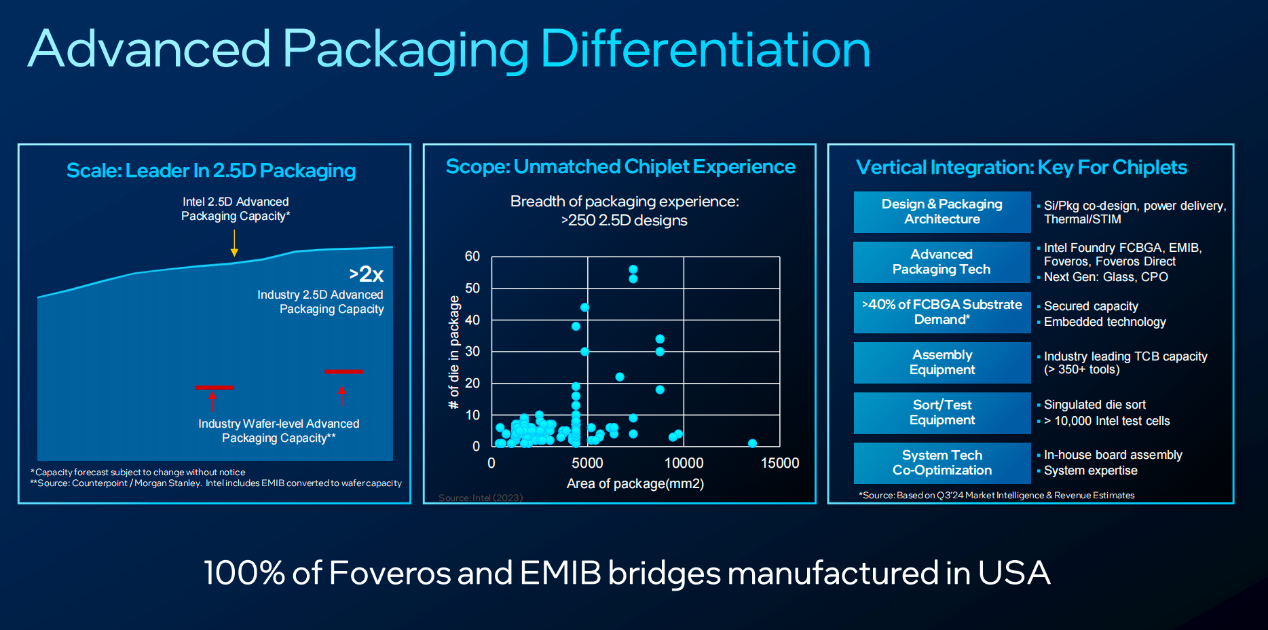

近年來,2.5D封裝產能一直面臨限制,特別是在某些市場需求不斷增長的情況下,封裝產能不足問題愈發顯著。然而,英特爾的EMIB技術在這一領域具有明顯的產能優勢。通過結合Foveros 2.5D和EMIB 2.5D,英特爾的綜合產能已經超過行業水平的兩倍,對于那些擔心需求波動或增長無法得到滿足的客戶,英特爾的解決方案無疑具有巨大的吸引力。據英特爾透露,AWS和Cisco在數據中心服務器和AI加速器產品領域就采用了英特爾的先進封裝技術。

英特爾領銜封裝技術數十年

作為封裝技術的先鋒,英特爾在過去五十多年里一直處于行業領先地位。從早期的引線鍵合架構(Wire-Bond)到倒裝陶瓷芯片(Flip-Chip Ceramic)和多芯片(Multi-Chip)封裝技術,英特爾不斷推動封裝技術的發展。如今,它通過與生態系統伙伴合作制定標準,帶領整個行業邁入先進封裝的新時代,包括2.5D、3D乃至3.5D技術。以英特爾EMIB 2.5D為例,其首個產品已量產近十年,這些成果并非一蹴而就,而是長期積累的結晶。

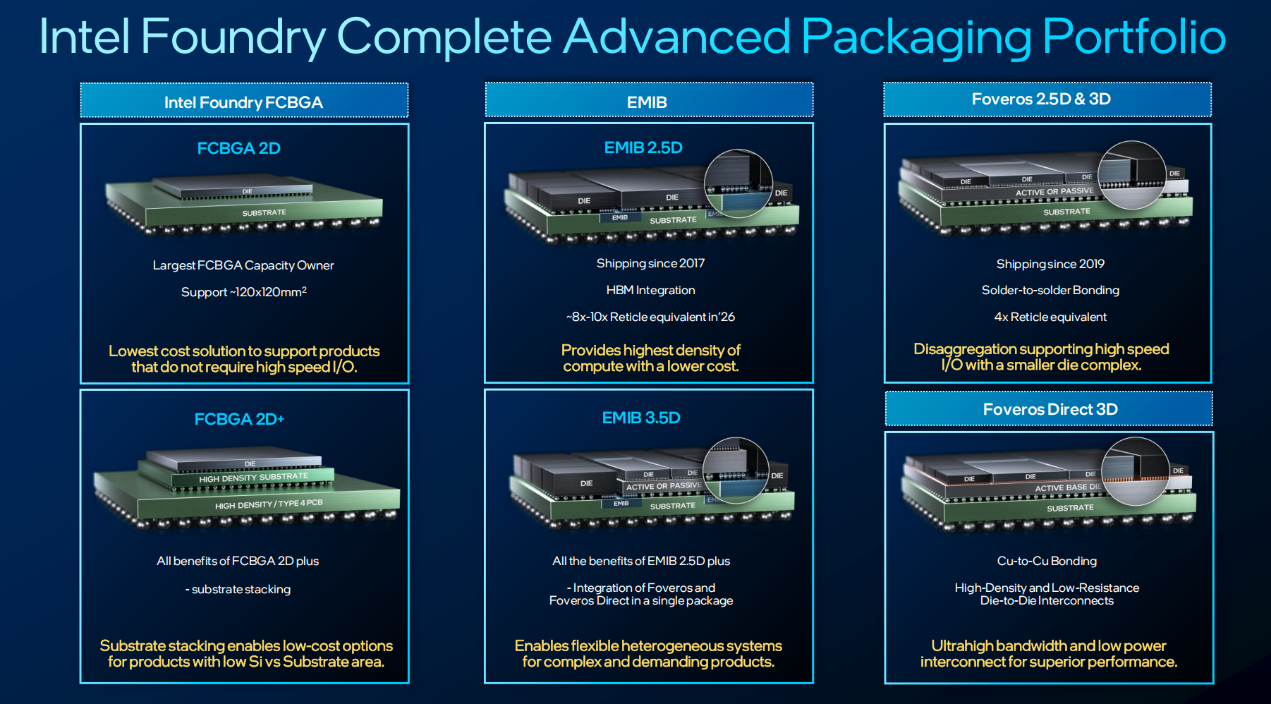

目前,英特爾代工提供了一套完整的先進封裝產品組合,滿足從低成本到高性能的多樣化需求:

首先,成本低廉的FCBGA。FCBGA(Flip-Chip Ball Grid Array)分為兩種版本:FCBGA 2D和FCBGA 2D+。FCBGA 2D是傳統的有機封裝技術,至今仍在量產。它成本低廉,適合I/O需求少、不需要高速連接的產品,是許多細分市場的理想選擇。而FCBGA 2D+在FCBGA 2D基礎上加入了基板層疊技術(Substrate Stacking),針對主板連接尺寸大但芯片復雜度不高的場景,能有效降低客戶為高密度基板支付的額外成本。這種技術在網絡和交換設備領域尤其受歡迎。

接著,EMIB系列主打高性能。EMIB(嵌入式多芯片互連橋接)包括EMIB 2.5D和EMIB 3.5D兩種。EMIB 2.5D通過基板中的微型硅橋連接單層芯片或HBM堆疊,實現高密度、低功耗的芯片間通信。雖然它也用于消費類產品,但在AI和高性能計算(HPC)領域表現尤為出色。EMIB 3.5D與EMIB 2.5D類似,都采用嵌入基板中的硅橋技術。不同之處在于EMIB 3.5D引入了3D堆疊技術,將芯片疊放在有源或無源基板上。這不僅保留了EMIB的連接優勢,還增加了垂直堆疊的靈活性。某些IP更適合垂直堆疊,而不是水平連接。此外,由于封裝的復雜度較高,客戶希望利用EMIB技術將這些堆疊連接起來,而不是使用大型的無源或有源中介層。

最后則是Foveros技術,Foveros技術分為Foveros 2.5D和Foveros 3D。Foveros 2.5D采用焊料連接芯片與晶圓,適合將高速I/O與小型芯片組分離的場景。而Foveros Direct則使用銅-銅直接鍵合,提供最高帶寬和最低功耗的互連,性能無可匹敵。在AI和HPC應用中,這些技術還能靈活組合——比如Foveros Direct 3D搭配HBM,再融入EMIB 3.5D,形成一個多技術融合的封裝方案。

英特爾代工的新招

半導體行業正迎來一個全新的發展階段,傳統的芯片設計與制造模式已不足以應對AI和高性能計算帶來的復雜需求。在這一轉型期,系統級代工廠(Systems Foundry)和系統技術協同優化(System Technology Co-Optimization)的重要性日益凸顯。作為代工廠或服務提供商,英特爾認為,通過這些協同優化策略,可以更好地滿足客戶需求,打造更強大的產品。

在這一背景下,英特爾不僅專注于傳統封裝技術,還擴展到了系統級架構和設計服務。比如,熱建模與優化、功耗建模與優化,這些都是英特爾多年來與內部產品部門合作積累的技術成果,并廣泛應用到各種產品中。一個典型的例子是幾年前推出的英特爾數據中心 GPU Max 系列。這款產品把近50塊芯片集成到一個封裝里,這些芯片基于五種不同的制造工藝,有些來自英特爾,有些來自第三方代工廠。要實現這樣的產品,光靠技術本身還不夠,還需要硅芯片與封裝的協同設計,再加上熱管理、功率傳輸等環節的優化,才能讓這么多芯片在一個封裝里高效工作。

說到復雜封裝,英特爾還在細節上下足了功夫。比如在大型封裝中,芯片和基板可能會因為尺寸大而出現翹曲問題。英特爾通過優化工藝流程和主板設計,解決了這些翹曲邊緣的管理問題,確保即使在高復雜度下,產品性能依然穩定可靠。

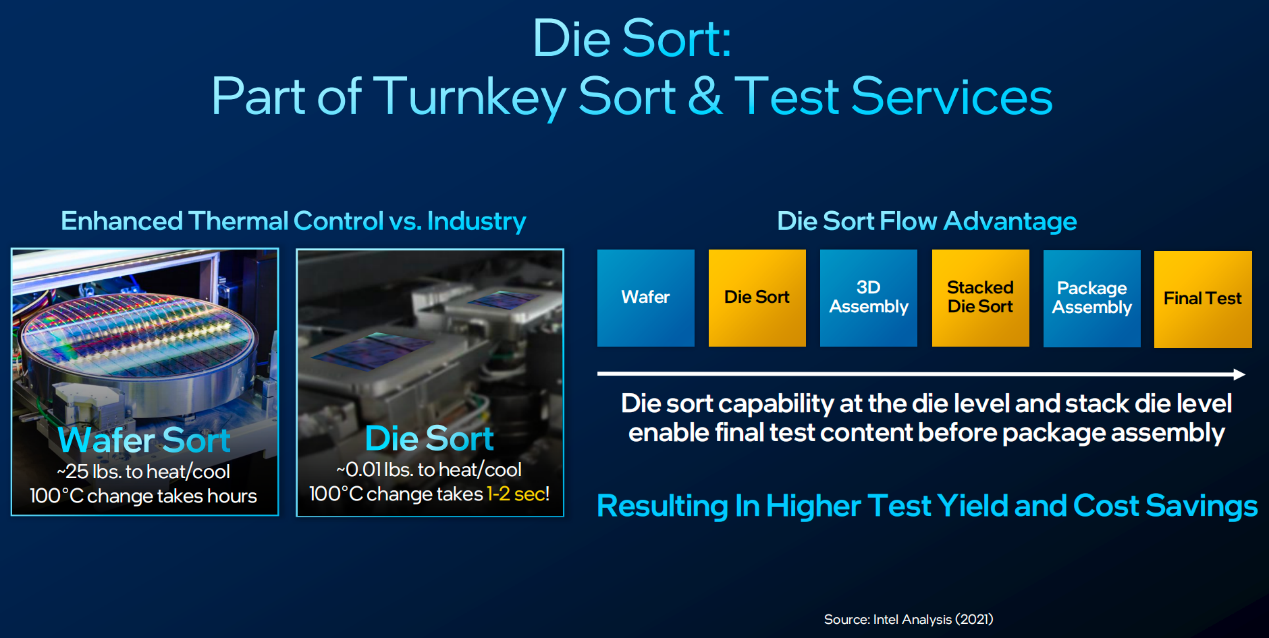

當然,好封裝離不開好測試。芯片測試是確保封裝質量的關鍵一環,尤其是要保證進入封裝的芯片都是“已知良品”(Known Good Die,簡稱KGD)。如果一個封裝里只有一塊芯片,測試還算簡單。但像現在這樣,一個封裝可能包含50塊不同功能的芯片,比如GPU、I/O單元和HBM堆疊,只要有一塊壞芯片,整個封裝就可能報廢。所以,提前檢測出問題芯片,避免浪費其他好芯片,顯得特別重要。

為此,英特爾開發了“裸片測試”(Die Sort)技術,這項技術已經在生產中用了十多年。它的做法是先把整片晶圓切成單個裸片,然后在組裝到基板之前進行測試。因為裸片很小,熱量控制非常精準,甚至可以在1秒內讓溫度變化100攝氏度。這種高精度的測試能提前發現缺陷,比如GPU或計算單元的問題,從而提高生產效率和良率。過去,這種提前檢測已經很有價值,但現在,當一個封裝的材料和芯片成本高達幾千美元時,它的重要性就更加凸顯了。尤其在如今的產品中,可能包含10片、20片甚至50片芯片,良品管理成了重中之重。通過在制造的早期加入測試環節,英特爾能確保每一步都用的是好芯片,避免后期更大的損失。

與此同時,英特爾的代工服務也在變得更靈活。Mark Gardner提到,客戶現在可以根據需要自由選擇服務:比如只用英特爾的EMIB封裝技術,芯片則交給其他代工廠生產;或者只用英特爾的裸片測試能力。這種“按需定制”的模式也延伸到了晶圓制造層面,讓客戶能專注于對自己最重要的環節,獲得最有價值的服務。

英特爾已完成超過250個2.5D設計項目,涵蓋消費電子、FPGA、服務器數據中心和AI加速器等多領域應用,2.5D技術已廣泛投入生產。英特爾還提供增值服務,幫助客戶優化產品設計,包括硅與封裝協同設計、功率傳輸、熱管理等方面,憑借豐富的經驗與技術積累,協助客戶提升產品性能。

值得一提的是,英特爾還跟其他代工廠,比如臺積電和三星,保持長期合作。他們制定了兼容的設計規則,確保這些代工廠生產的晶圓能無縫適配英特爾的封裝技術。這不僅給了客戶更多選擇,也讓不同供應商的技術能自由組合,滿足多樣化的市場需求。

未來展望:更大封裝與玻璃基板的應用

展望未來,英特爾正在積極推動封裝技術的進一步發展,特別是在封裝尺寸和材料選擇上。Gardner透露,英特爾正在研發120毫米×120毫米的超大封裝尺寸,并計劃在未來一到兩年內實現量產。這一技術的推進將進一步拓展AI加速器的封裝能力,滿足更大規模計算需求。

此外,英特爾對玻璃基板和玻璃核心技術的投資也在不斷加大。隨著封裝尺寸的增大,傳統材料的局限性變得愈加明顯,玻璃基板因其出色的性能和擴展性,逐漸成為未來封裝技術的重要組成部分。Gardner認為,玻璃基板將在未來幾年成為主流,將推動封裝技術的持續擴展和創新。

結語

隨著AI技術的不斷進步和應用場景的不斷擴展,封裝技術的創新將成為推動產業變革的重要動力。英特爾通過EMIB、Foveros等多項先進封裝技術,不斷突破技術瓶頸,提供高效、靈活的解決方案,引領著封裝技術的未來方向。

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54007瀏覽量

465923 -

英特爾

+關注

關注

61文章

10301瀏覽量

180416 -

封裝

+關注

關注

128文章

9248瀏覽量

148610 -

AI

+關注

關注

91文章

39755瀏覽量

301356

發布評論請先 登錄

先進封裝成破局,博通率先落地3.5D,6000mm2超大集成

先進封裝時代,芯片測試面臨哪些新挑戰?

2D、2.5D與3D封裝技術的區別與應用解析

淺談2D封裝,2.5D封裝,3D封裝各有什么區別?

Socionext推出3D芯片堆疊與5.5D封裝技術

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

3D封裝的優勢、結構類型與特點

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

為何邊緣設備正成為AI的新重心

芯原推出面向可穿戴設備的超低功耗OpenGL ES GPU,支持3D/2.5D混合渲染

3D封裝與系統級封裝的背景體系解析介紹

2.5D封裝為何成為AI芯片的“寵兒”?

2.5D封裝為何成為AI芯片的“寵兒”?

評論