近日,全球晶圓代工龍頭臺積電宣布推出4nm制程工藝——N4P,希望借此贏得明年蘋果公司A16處理器代工訂單。臺積電表示,憑借5nm(N5)、4nm(N4)、3nm(N3)、以及最新的N4P制程,將能

2021-10-28 08:05:11 18894

18894 新思科技公司(Synopsys, Inc., 納斯達克股票市場代碼:SNPS)日前宣布: 該公司針對多家領先的晶圓代工廠優化的28納米工藝DesignWare IP已贏得第100項設計。

2012-09-20 10:11:40 1485

1485 美國高通公司與臺積電公司今日共同宣布,美國高通公司的全資子公司美國高通技術公司將率先采用臺積電公司28納米高性能移動(28HPM)制程生產芯片。

2013-02-26 17:20:20 1427

1427 微處理器設計公司ARM與臺積電今天共同宣布,首個采用臺積電下下代16nm工藝制程FinFET技術生產的ARM Cortex-A57處理器已成功流片。Cortex-A57處理器為ARM旗下性能最高的處理器。

2013-04-03 09:05:05 1484

1484 半導體設計公司新思科技 (Synopsys) 17 日宣布,將與晶圓代工龍頭臺積電合作推出針對高效能運算 (High Performance Compute) 平臺的創新技術,而這些新技術是由新思科技與臺積電合作的 7 納米制程 Galaxy 設計平臺的工具所提供。

2016-10-18 10:55:37 1097

1097 新思科技接口和基礎 IP 組合已獲多家全球領先企業采用,可為 ADAS 系統級芯片提供高可靠性保障 摘要: 面向臺積公司N5A工藝的新思科技IP產品在汽車溫度等級2級下符合 AEC-Q100 認證

2023-10-23 15:54:07 1964

1964 芯片PMIC 5即將問世,由于改為BCD制程,臺積電憑借先進制程技術優勢,可望拿下高通新一代PMIC 5訂單約70~80%數量,并牽動高通電源管理芯片代工廠大洗牌。 業界推估高通各種用途電源管理芯片的年

2017-09-22 11:11:12

越來越先進,臺積電的5nm制程成本也水漲船高,開發一款芯片的費用將達到5.4億美元,臺積電5nm全掩模流片費用大概要3億人民幣,而且還不包含IP授權費用。如此高的門檻,大部分公司都會選擇觀望。目前,也

2020-03-09 10:13:54

Kochpatcharin表示:“臺積公司與新思科技等開放創新平臺(OIP)合作伙伴緊密合作,助力我們的客戶在執行定制及模擬模塊的工藝制程設計遷移時,提高生產效率并加快設計收斂。現在,通過全新的新思科技AI驅動型模

2023-04-03 16:03:26

10nm將會流片,而張忠謀更是信心十足,他直言不諱地表示10nm量產后將會搶下更高的份額。臺積電聯席CEO劉德音此前也曾在一次投資人會議上透露,公司計劃首先讓自己的10納米芯片產線在今年底前全面展開

2016-01-25 09:38:11

臺積電稱其已解決造成40nm制程良率不佳的工藝問題

據臺積電公司高級副總裁劉德音最近在一次公司會議上表示,臺積電40nm制程工藝的良率已經提升至與現有65nm制程

2010-01-21 12:22:43 1259

1259 新思科技完整實施流程助力英飛凌在中國成功實現首款40納米3G基帶處理器芯片設計和一次流片成功

中國北京和西安,2010年8月9日—全

2010-08-11 14:39:39 773

773 Cadence設計系統公司日前宣布展訊通信有限公司實現了其首款40納米低功耗GSM/GPRS/EDGE/TD-SCDMA/HSPA商用無線通信芯片的一次性流片成功。

2011-01-22 10:04:17 1235

1235 聯電(2303-TW)(UMC-US)與全球半導體設計制造軟體暨IP領導廠商新思科技(Synopsys)昨日共同宣布,雙方已擴展夥伴關系,將于聯電28奈米HLP Poly SiON制程平臺上開發新思科技的DesignWare IP。 聯電表

2011-10-13 09:41:08 992

992 新思科技公司日前宣布:該公司與三星在FinFET技術上的多年合作已經實現了一個關鍵性的里程碑,即采用三星的14LPE工藝成功實現了首款測試芯片的流片

2013-01-09 12:11:31 1469

1469 領先的韓國半導體公司TLi采用Arasan的通用閃存(UFS)知識產權(IP)產品實現了芯片設計的出貨,該公司之前獲得了Arasan的UFS設備控制器IP及支持高達Gear 3速率的MPHY等產品的授權。TLi是最新一家使用Arasan的UFS Total IP解決方案成功實現芯片設計的公司。

2016-01-06 17:46:12 6084

6084 ASIC的復雜性不斷提高,同時工藝在不斷地改進,如何在較短的時間內開發一個穩定的可重用的ASIC芯片的設計,并且一次性流片成功,這需要一個成熟的ASIC的設計方法和開發流程。

2016-12-12 14:07:46 4384

4384 在晶圓代工市場,臺積電與三星的競爭始終是大家關心的戲碼。三星雖然有高通等VIP客戶,但在7納米制程節點,高通預計會轉投臺積電,三星要想受更多客戶的青睞,只能從制程技術著手了。這也是三星為什么跳過非

2018-06-19 15:06:00 5263

5263 Mali-G76處理器)的初期采用者實現了成功的流片。采用Fusion技術的新思科技設計平臺、Verification Continuum Platform和DesignWare接口IP互相配合,提供了優化的性能、功耗和面積,并加速了基于Arm的產品上市時間。

2018-07-28 11:17:00 1833

1833 日前,才在英國倫敦發布會上展出4款Mate 20系列手機,以及新款麒麟980處理器的華為,根據外電報導,更新一代的麒麟990處理器也已經發展到一個階段。這款預計采用臺積電內含EUV技術,7納米+加強版制程的處理器,預計將在2019年的第1季進行流片。

2018-10-22 14:48:20 9144

9144 臺積電總裁魏哲家昨(6)日在一年一度的供應鏈論壇中透露,臺積電將在南科六廠旁,新建一座8英寸廠,滿足客戶對特殊制程要求。這是2003年臺積電在上海松江8英寸廠成立后,臺積電15年來第一次新建8英寸廠。

2018-12-07 15:06:32 2888

2888 4月4日消息,據Digitimes報道,臺積電宣布在開放創新平臺之下推出5nm設計架構的完整版本,協助客戶實現支持下一代高效能運算應用產品的5nm系統單芯片設計,目標鎖定擁有廣闊發展前景的5G與人

2019-04-04 11:16:02 3456

3456 就在16日一早,韓國晶圓代工廠三星宣布發展完成 5 納米制程,并且推出 6 納米制程,并準備量產 7 納米制程的同時,晶圓代工龍頭臺積電也在傍晚宣布,推出 6 納米 (N6) 制程技術,除大幅強化

2019-04-17 16:42:50 3248

3248 新思宣布,其用于臺積電7納米制程技術的DesignWare邏輯庫、嵌入式存儲器、界面和類比IP已獲得超過250個設計的選用(design wins),目前已經有近30家半導體廠商選擇了新思7納米

2019-05-14 16:25:27 3405

3405 新思科技近日宣布與GLOBALFOUNDRIES (GF)合作,針對GF的12納米領先性能(12LP) FinFET工藝技術,開發覆蓋面廣泛的DesignWare? IP組合,包括多協議25G

2019-07-05 09:13:13 3813

3813 臺積電宣布,其領先業界導入極紫外光(EUV)微影技術的7納米強效版(N7+)制程已協助客戶產品大量進入市場。導入EUV微影技術的N7+奠基于臺積電成功的7納米制程之上,也為明年首季試產6納米和更先進制程奠定良好基礎。

2019-10-08 16:11:37 3646

3646 就在晶圓代工龍頭臺積電之前宣布旗下6納米制程將在2020年第1季推出,而更新的5納米制程也將隨之在后的情況下,半導體模擬軟件大廠ANSYS于16日宣布,旗下的半導體套件解決方案已獲臺積電最新版N5

2019-10-17 16:19:11 4053

4053 根據臺積電總裁魏哲家日前在法人說明會中的說法指出,臺積電的5納米制程(N5)已進入風險試產階段,并有不錯的良率表現。對此,根據供應鏈的消息指出,目前已經進入風險試產階段的5納米制程其良率達到了50%,而且月產能可上看8萬片的規模。

2019-10-28 16:32:41 3576

3576 關于臺積電的N5流程,ChainNews通過RetiredEngineer報告稱,蘋果迅速介入以彌補華為削減開支所帶來的損失。它補充說,蘋果還要求臺積電在第四季度每月為其下一代iDevices增加近10,000個晶圓。

2020-04-25 10:14:49 3246

3246 6月11日消息,Moortec今天宣布其深度嵌入式監控產品組合再添新成員 -- 基于臺積電N5工藝技術的分布式熱傳感器(DTS)。Moortec高度微粒化DTS的面積只有一些標準芯片內熱傳感器

2020-06-15 15:04:32 2766

2766 Moortec宣布其深度嵌入式監控產品組合再添新成員 -- 基于臺積電N5工藝技術的分布式熱傳感器(DTS)。Moortec高度微粒化DTS的面積只有一些標準芯片內熱傳感器解決方案的七分之一,還支持

2020-08-04 15:00:02 1076

1076 據珠海特區報近日報道稱,中國領先的一站式IP和定制芯片領軍企業——芯動科技發布消息稱,該公司已完成全球首個基于中芯國際FinFET N+1先進工藝的芯片流片和測試,所有IP全自主國產,功能一次測試通過,為國產半導體生態鏈再立新功。

2020-10-12 09:46:18 7398

7398 我國一站式IP定制芯片企業芯動科技(INNOSILICON)近日宣布:已完成全球首個基于中芯國際FinFET N+1先進工藝的芯片流片和測試,所有IP全自主國產,功能一次測試通過。 芯動科技擁有自主

2020-10-13 17:33:19 3784

3784 、DDR5、LPDDR5、MIPI、OTP NVM等 ●新思科技與GF的長期合作,成功實現了DesignWare IP核從180nm到12nm的開發,并可應用于廣泛領域 新思科技(Synopsys)近日宣布

2020-11-03 16:48:08 2984

2984 當下的半導體界,最值錢的非晶圓代工產能莫屬了。而作為行業龍頭,臺積電的產能,特別是先進制程的,幾乎呈現被“瘋搶”的狀態,這也成為了該公司幸福的煩惱。就在不久前,臺積電宣布取消未來一段時間內12英寸晶

2021-01-12 14:55:48 2719

2719 DesignWare HBM2E PHY IP 可提供每秒 460 GB 的聚合帶寬,能夠滿足先進 FinFET 工藝 SoC 對海量計算性能的要求。HBM2E IP 是新思科技全面內存接口 IP

2021-02-14 09:22:00 1151

1151 SoC 設計與應用技術領導廠商Socionext Inc.(以下“Socionext”)宣布,公司將采用臺積電最新5nm制程工藝(N5P)用于下一代汽車定制芯片業務。Socionext汽車定制芯片

2021-02-05 11:50:27 2701

2701 最大的RISC-V架構廠商SiFive近日宣布,其OpenFive部門已成功采用臺積電(TSMC)的N5工藝技術流片公司首個SoC,采用2.5D封裝HBM3存儲單元,帶寬7.2Gbps。在半導體行業中,流片意味著芯片設計大功告成,一般會在一年內投入商用。

2021-05-01 09:33:00 3547

3547

據外媒最新報道,三星宣布,3nm制程技術已經正式流片! 據悉,三星的3nm制程采用的是GAA架構,性能上完勝臺積電的3nm FinFET架構! 據報導,三星在3nm制程的流片進度是與新思科技合作完成

2021-07-01 15:27:44 4638

4638 電子發燒友網報道(文/吳子鵬)近日,全球晶圓代工龍頭臺積電宣布推出4nm制程工藝——N4P,希望借此贏得明年蘋果公司A16處理器代工訂單。臺積電表示,憑借5nm(N5)、4nm(N4)、3nm(N

2021-10-30 11:25:16 9826

9826 通過與臺積公司在早期的持續合作,我們為采用臺積公司先進的N3制程技術的設計提供了高度差異化的解決方案,讓客戶更有信心成功設計出復雜的SoC。

2021-11-02 09:24:25 687

687 雙方拓展戰略合作,提供全面的3D系統集成功能,支持在單一封裝中集成數千億個晶體管 新思科技3DIC Compiler是統一的多裸晶芯片設計實現平臺,無縫集成了基于臺積公司3DFabric技術

2021-11-05 15:17:19 6382

6382 雙方合作涵蓋新思科技的Interface IP、基于TSMC 3DFabric?的設計解決方案以及針對臺積公司N4制程技術的PPA優化。

2021-11-08 11:54:45 781

781 技(Synopsys)近日宣布其數字定制設計平臺已獲臺積公司N3制程技術認證,雙方將共同優化下一代芯片的功耗、性能和面積(PPA)。基于多年的密切合作,本次經嚴格驗證的認證是基于臺積公司最新版本的設計規則手冊(DRM)和制程設計套件(PDK)。此外,新思科技

2021-11-16 11:06:32 2326

2326 新思科技(Synopsys)近日推出面向臺積公司N6RF工藝的全新射頻設計流程,以滿足日益復雜的射頻集成電路設計需求。

2022-06-24 14:30:13 1700

1700 新思科技數字和定制設計流程獲得臺積公司的N3E和N4P工藝認證,并已推出面向該工藝的廣泛IP核組合。

2022-07-12 11:10:51 1780

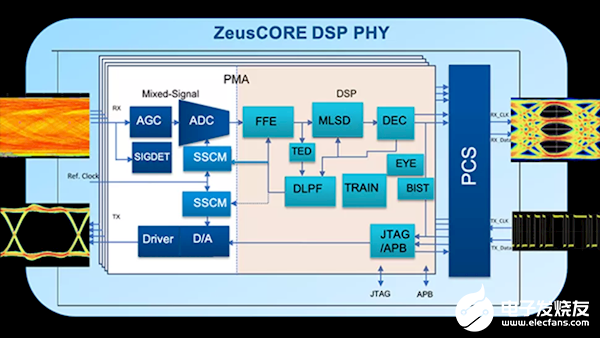

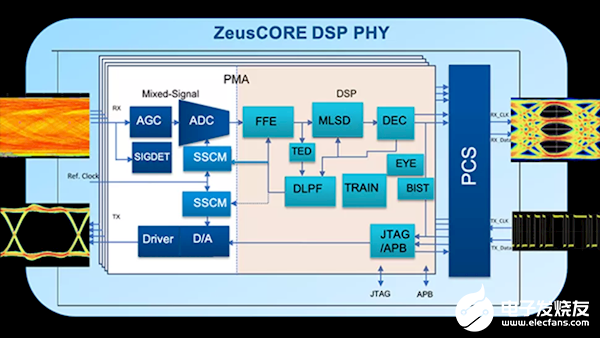

1780 日前,Alphawave公司宣布,其成為臺積電N3E工藝首批流片的客戶。相關產品會在本周晚些時候的臺積電OIP論壇上公布詳情。 據悉,這是一款DSP PHY串行控制芯片,IP核

2022-10-27 10:03:56 2099

2099

,納斯達克股票代碼:SNPS )近日宣布,得益于與臺積公司的長期合作,新思科技針對臺積公司N3E工藝技術取得了多項關鍵成就,共同推動先進工藝節點的持續創新。新思科技經產品驗證的數字和定制設計流程已在臺積公司N3E工藝上獲得認證。此外,該流程和新思科技廣泛的

2022-11-08 13:37:19 1951

1951 3E工藝技術取得了多項關鍵成就,共同推動先進工藝節點的持續創新。新思科技經產品驗證的數字和定制設計流程已在臺積公司N3E工藝上獲得認證。此外,該流程和新思科技廣泛的基礎IP、接口IP組合已經在臺積公司N3E工藝上實現了多項成功流片,助力合

2022-11-10 11:15:22 1158

1158 為滿足客戶對異構計算密集型應用的復雜要求,新思科技(Synopsys,Inc.,納斯達克股票代碼:SNPS)近日宣布,推出業界領先的全面EDA和IP解決方案,面向采用了臺積公司先進N7、N5和N

2022-11-16 16:25:43 1653

1653 ? ? ?新思科技(Synopsys, Inc.)近日宣布,推出全面EDA和IP解決方案,面向采用了臺積公司先進N7、N5和N3工藝技術的2D/2.5D/3D多裸晶芯片系統。基于與臺積公司在

2022-12-01 14:10:19 991

991 )設計流程是雙方合作中的亮點之一 新思科技(Synopsys)近日宣布,連續第12年被評選為“臺積公司OIP開放創新平臺年度合作伙伴”(OIP,Open Innovation Platform)并斬獲六個獎項,充分彰顯了雙方長期合作在 多裸晶芯片系統、 加速高質量接口IP、射頻設計、云解決方案

2022-12-14 18:45:02 1339

1339 摘要: 新思科技連續12年被評為“臺積公司OIP年度合作伙伴” 該合作推動了多裸晶芯片系統的發展和先進節點設計 獎項涵蓋數字和定制設計、IP、以及基于云的解決方案 推出毫米波(mmWave)射頻

2022-12-15 10:48:45 542

542

的先進設計。另一款 CPU 設計采用 AI 賦能的 Cadence Cerebrus Intelligent Chip Explorer 和完整的數字設計流程,借助臺積電 N5 制程工藝,成功讓功耗降低 8%,設計面積縮小 9%,同時顯著提升了工程效率。

2023-02-06 15:02:48 2008

2008 屢獲殊榮的新思科技DSO.ai解決方案通過大幅提高芯片設計效率、性能和云端擴展性,助力客戶實現新突破 摘要: 新思科技攜手芯片設計生態系統,通過DSO.ai率先實現100次流片,覆蓋一系列前沿

2023-02-10 10:56:07 721

721 新 思科 技攜手芯片設計生態系統,通過DSO.ai率先實現100 次流片,覆蓋一系列前沿應用和不同先進工藝節點 意法半導體首次使用云端人工智能設計實現流片,通過DSO.ai以3倍的設計效率達成更高

2023-02-14 15:15:04 1359

1359 來源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺積電 3nm(N3E)工藝技術的 Cadence? 16G UCIe? 2.5D 先進封裝 IP 成功流片。該 IP 采用臺積電

2023-04-27 16:35:40 1377

1377

該 IP 采用臺積電 3DFabric? CoWoS-S 硅中介層技術實現,可提供超高的帶寬密度、高效的低功耗性能和卓越的低延遲

2023-04-28 15:14:12 1709

1709 股票代碼:SNPS)近日宣布,攜手臺積公司和Ansys持續加強多裸晶芯片系統設計與制造方面的合作,助力加速異構芯片集成以實現下一階段的系統可擴展性和功能。得益于與臺積公司在3DFabric?技術和3Dblox?標準中的合作,新思科技能夠為臺積公司先進的7納米、5納米和3納米工藝技

2023-05-17 15:43:06 450

450 新思科技(Synopsys, Inc.)近日宣布,攜手臺積公司和Ansys持續加強多裸晶芯片系統設計與制造方面的合作,助力加速異構芯片集成以實現下一階段的系統可擴展性和功能。得益于與臺積公司在

2023-05-18 16:04:08 1365

1365 集成以實現下一階段的系統可擴展性和功能。得益于與臺積公司在3DFabric技術和3Dblox標準中的合作,新思科技能夠為臺積公司先進的7納米、5納米和3納米工藝技術上的多裸晶芯片系統設計,提供業界領先的全方位EDA和IP解決方案。臺積公司先進工

2023-05-22 22:25:02 875

875

新思科技一直與臺積公司保持合作,利用臺積公司先進的FinFET工藝提供高質量的IP。近日,新思科技宣布在臺積公司的N3E工藝上成功完成了Universal Chiplet Interconnect

2023-05-25 06:05:02 1446

1446 Labs實現光學DSP SoC設計的一次性流片成功。2021年,Banias Labs采用了新思科技的IP,以充分利用該IP在低延遲、傳輸長度靈活性、以及在5納米工藝技術上的成熟度等方面的技術

2023-06-19 18:05:01 642

642

的“耳目”。 新思科技一直走在芯片監控解決方案的前沿,而這些解決方案是新思科技芯片生命周期管理(SLM)系列的一部分。最近, 新思科技在臺積公司N5和N3E工藝上完成了PVT監控IP測試芯片的流片 。這是一個里程碑式的成功。從此,那些準備在這些先進節點

2023-07-11 17:40:01 1828

1828 基于臺積公司N3E工藝技術的新思科技IP能夠為希望降低集成風險并加快首次流片成功的芯片制造商建立競爭優勢

2023-08-24 17:37:47 1737

1737 MediaTek 與臺積公司今日共同宣布,MediaTek 首款采用臺積公司 3 納米制程生產的天璣旗艦芯片開發進度十分順利,日前已成功流片,預計將在明年量產。MediaTek 與臺積公司

2023-09-07 09:30:01 868

868

? 2023 年9月7日 – MediaTek與臺積公司今日共同宣布,MediaTek首款采用臺積公司3納米制程生產的天璣旗艦芯片開發進度十分順利,日前已成功流片,預計將在明年量產。MediaTek

2023-09-07 10:14:48 611

611 已成功流片。 3NM制程天璣旗艦芯片量產時間預計在2024年,2024年下半年會正式上市。業內估計3NM的MediaTek旗艦芯片型號應該不是今年上市的天璣9300,天璣9300可能采用的是臺積電

2023-09-08 12:36:13 2932

2932 內容提要 ● ?經過驗證的接口 IP,可顯著提升 TSMC N3E 制程節點的性能和能效 ● ?224G-LR SerDes PHY IP 在 TSMC N3E 制程上實現一次性流片成功

2023-09-26 10:10:01 1655

1655 蘋果已經發布了基于臺積電3nm制程的A17 Pro處理器。最近,有消息稱,高通的下一代5G旗艦芯片也將采用臺積電3nm制程,并預計會在10月下旬公布,成為臺積電3nm制程的第三個客戶,可能是高通驍龍8 Gen3。

2023-09-26 16:51:31 2546

2546 《半導體芯科技》編譯 來源:EENEWS EUROPE 新思科技(Synopsys)表示,其客戶已在臺積電2nm工藝上流片了多款芯片,同時對模擬和數字設計流程進行了認證。 新思科技表示,臺積電2nm

2023-10-08 16:49:24 930

930 多個設計流程在臺積公司N2工藝上成功完成測試流片;多款IP產品已進入開發進程,不斷加快產品上市時間 ? 摘要: 新思科技經認證的數字和模擬設計流程可提高高性能計算、移動和AI芯片的產品質量

2023-10-19 11:44:22 918

918 作為Synopsys.ai EDA整體解決方案的一部分,由AI驅動的模擬設計遷移流可助力提升模擬和混合信號 SoC 的設計生產率 摘要 : 新思科技AI驅動的設計解決方案可實現電路優化,在提高

2023-10-24 11:41:37 962

962 新思科技近日宣布,其數字和定制/模擬設計流程已通過臺積公司N2工藝技術認證,能夠幫助采用先進工藝節點的SoC實現更快、更高質量的交付。新思科技這兩類芯片設計流程的發展勢頭強勁,其中數字設計流程已實現

2023-10-24 16:42:06 1394

1394 新思科技(Synopsys, Inc.)近日宣布,面向臺積公司N5A工藝推出業界領先的廣泛車規級接口IP和基礎IP產品組合,攜手臺積公司推動下一代“軟件定義汽車”發展,滿足汽車系統級芯片(SoC)的長期可靠性和高性能計算需求。

2023-10-24 17:24:56 1694

1694 和 M-PHY ,以及 USB IP 產品都遵循了 TSMC N5A 工藝領先的車載等級設計規則。 新思科技宣布面向臺積公司N5A工藝推出業界領先的廣泛車規級接口IP和基

2023-10-31 09:18:44 1918

1918 、汽車和高性能計算設計的開發和硅片成功。在2023年臺積公司北美OIP生態系統論壇上,新思科技展示的解決方案數量遠超從前,進一步突顯了新思科技與臺積公司及其合作伙伴面向臺積公司先進工藝和3DFabric技術的成熟解決方案方面的緊密合作。

2023-11-14 10:31:46 1202

1202 據悉,臺積電近期發布的2023年報詳述其先進制程與先進封裝業務進展,包括N2、N3、N4、N5、N6e等工藝節點,以及SoIC CoW、CoWoS-R、InFO_S、InFO_M_PoP等封裝技術。

2024-04-25 15:54:58 1797

1797 套件賦能可投產的數字和模擬設計流程能夠針對臺積公司N3/N3P和N2工藝,助力實現芯片設計成功,并加速模擬設計遷移。 新思科技物理驗證解決方案已獲得臺積公司N3P和N2工藝技術認證,可加速全芯片物理簽核。 新思科技3DIC Compiler和光子集成電路(PIC)解決方案與臺

2024-05-11 11:03:49 695

695

新思科技EDA事業部戰略與產品管理副總裁Sanjay Bali表示:“新思科技在可投產的EDA流程和支持3Dblox標準的3DIC Compiler光子集成方面的先進成果,結合我們廣泛的IP產品組合,使得我們與臺積公司能夠助力開發者基于臺積公司先進工藝加速下一代芯片設計創新。

2024-05-11 16:25:42 1016

1016 新思科技近日與臺積公司宣布,在先進工藝節點設計領域開展了廣泛的EDA和IP合作。雙方的合作成果已經成功應用于一系列人工智能、高性能計算和移動設計領域,取得了顯著成效。

2024-05-13 11:04:48 931

931 由Synopsys.ai EDA套件賦能可投產的數字和模擬設計流程能夠針對臺積公司N3/N3P和N2工藝,助力實現芯片設計成功,并加速模擬設計遷移。

2024-05-14 10:36:48 1197

1197

在近期舉行的2024年歐洲技術研討會上,臺積電透露了即將用于HBM4制造的基礎芯片的部分新信息。據悉,未來HBM4將采用邏輯制程生產,而臺積電計劃利用其N12和N5制程的改良版來完成這一任務。

2024-05-20 09:14:11 1792

1792 在近日舉行的2024年歐洲技術研討會上,臺積電透露了關于HBM4基礎芯片制造的新進展。據悉,未來HBM4將采用邏輯制程進行生產,臺積電計劃使用其N12和N5制程的改良版來完成這一任務。

2024-05-21 14:53:14 1442

1442 在半導體行業的最新動態中,臺積電再次展示了其在制程技術和封裝技術方面的領先地位。本周,臺積電宣布其2nm制程工藝即將進入試產階段,而蘋果公司則獨占了這一先進制程的首批產能,計劃用于制造備受期待

2024-07-16 10:28:58 1698

1698 在半導體技術日新月異的今天,SK海力士再次引領行業潮流,宣布將采用臺積電先進的N5工藝版基礎裸片來構建其新一代HBM4內存。這一舉措不僅標志著SK海力士在高性能存儲解決方案領域的持續深耕,也預示著HBM內存技術即將邁入一個全新的發展階段。

2024-07-18 09:47:53 1328

1328 據業界最新消息,AMD即將成為臺積電位于美國亞利桑那州菲尼克斯附近的Fab 21工廠的第二大知名客戶,該工廠已經開始試產包括N5、N5P、N4、N4P及N4X在內的一系列5nm節點制程。

2024-10-08 15:37:03 840

840 半導體技術領域的發展速度十分驚人,新思科技與臺積公司(TSMC)始終處于行業領先地位,不斷突破技術邊界,推動芯片設計的創新與效率提升。我們與臺積公司的長期合作催生了眾多行業進步,從更精細的工藝節點到更高層次的系統集成,創造了無限可能。

2024-10-31 14:28:17 1022

1022 在音視頻行業追求高畫質、低延時、高效率的傳輸制作環境中,技術創新始終是驅動進步的核心力量。千視秉承“以用戶為中心”的理念,再次從市場痛點出發,為用戶提供更優質的解決方案。這一次,我們推出了針對N

2024-12-18 10:02:51 1679

1679

工藝——N3P。與前代工藝相比,N3P在性能上實現了約5%的提升,同時在功耗方面降低了5%至10%。這一顯著的進步意味著,搭載M5芯片的設備將能夠提供更強大的處理能力,同時擁有更出色的電池續航能力。 除了制程工藝的提升,蘋果M5系列芯片還采用了臺積電

2025-02-06 14:17:46 1313

1313 在分享中表示,OPPO工程師在折疊屏技術上取得了重大突破,成功解決了折疊屏手機普遍存在的折痕問題。為了實現這一目標,工程師們在Find N5的30個關鍵部件上采用了20種新材料,這些創新材料的應用使得Find N5在不犧牲耐用性的前提下,實現了無與倫比的輕薄設計。

2025-02-07 10:59:45 1067

1067 代號為“Venice”的新一代AMD EPYC CPU是首款基于臺積電新一代N2制程的高性能計算產品。 ? AMD表示,其代號為“Venice”的新一代AMD EPYC?處理器是業界首款完成流片并

2025-05-06 14:46:20 637

637

新思科技近日宣布持續深化與臺積公司的合作,為臺積公司的先進工藝和先進封裝技術提供可靠的EDA和IP解決方案,加速AI芯片設計和多芯片設計創新。

2025-05-27 17:00:55 1040

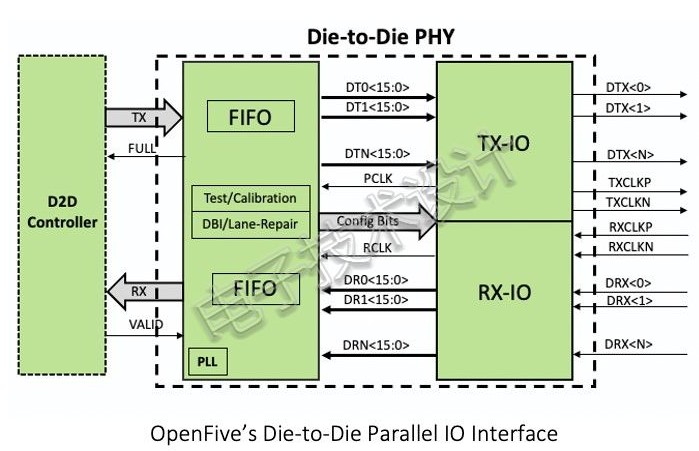

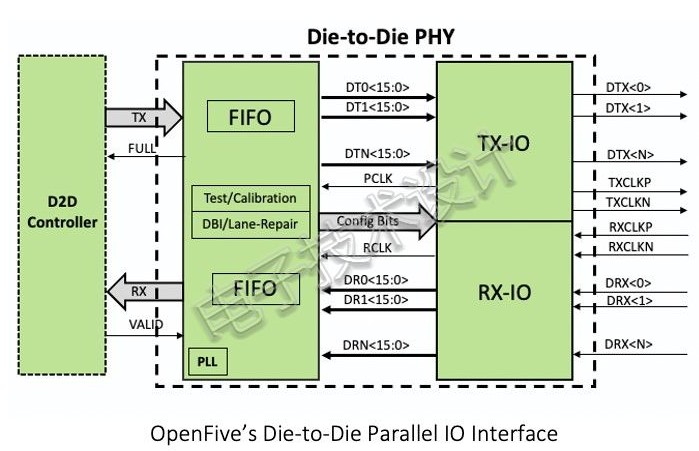

1040 我們很高興展示基于臺積電成熟 N4 工藝打造的 Gen1 UCIe IP 的 16GT/s 眼圖。該 IP 一次流片成功且眼圖清晰開闊,為尋求 Die-to-Die連接的客戶再添新選擇。

2025-08-25 16:48:05 1780

1780

MediaTek 今日宣布,MediaTek 首款采用臺積電 2 納米制程的旗艦系統單芯片(SoC)已成功完成設計流片(Tape out),成為首批采用該技術的公司之一,并預計明年底進入量產。雙方

2025-09-16 16:40:31 978

978 給大家分享兩個熱點消息: 臺積電2納米N2制程吸引超15家客戶 此前有媒體爆出蘋果公司已經鎖定了臺積電2026年一半以上的2nm產能;而高通和聯發科等其他客戶難以獲得足夠多的臺積電2nm制程的產能

2025-09-23 16:47:06 752

752 臺積電2nm 制程試產成功 近日,晶圓代工龍頭臺積電(TSMC)正式宣布其2納米制程技術試產成功,這一重大里程碑標志著全球半導體產業正式邁入全新的制程時代。隨著試產工作的順利推進,2納米芯片距離量產

2025-10-16 15:48:27 1090

1090 還就面向TSMC-COUPE平臺的AI輔助設計流程開展了合作。新思科技與臺積公司共同賦能客戶有效開展芯片設計,涵蓋AI加速、高速通信和先進計算等一系列應用。

2025-10-21 10:11:05 434

434 新思科技近期宣布,其LPDDR6 IP已在臺積公司 N2P 工藝成功流片,并完成初步功能驗證。這一成果不僅鞏固并強化了新思科技在先進工藝節點 IP 領域的領先地位,同時也為客戶提供可信賴的、經硅片驗證的IP選擇,可滿足移動通訊、邊緣 AI 及高性能計算等更高存儲帶寬需求的應用場景。

2025-10-30 14:33:48 1873

1873

為推動小芯片創新的下一波浪潮,Cadence 成功流片其第三代通用小芯片互連技術(UCIe)IP 解決方案,在臺積電先進的 N3P 工藝上實現了業界領先的每通道 64Gbps 速率。隨著行業向日

2025-12-26 09:59:44 168

168

電子發燒友App

電子發燒友App

評論