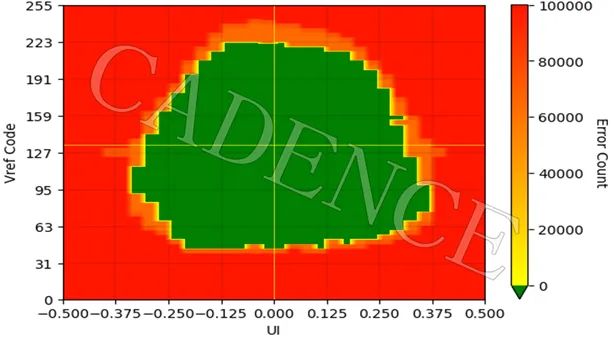

我們很高興展示基于臺積電成熟 N4 工藝打造的Gen1 UCIe IP 的 16GT/s 眼圖。該 IP 一次流片成功且眼圖清晰開闊,為尋求 Die-to-Die連接的客戶再添新選擇。

圖1:Cadence UCIe IP 的 16GT/s 接收端眼圖

UCIe 提供芯片間連接,支持跨技術節點的異構集成。憑借我們經過流片驗證的 D2D IP,這一突破為我們共有的客戶在多芯片設計實施上提供了更大靈活性。這建立在我們先前展示的 16GT/s IP 成功基礎上,其標準和先進的 3nm 封裝設計均已被 IEEE 會議收錄。

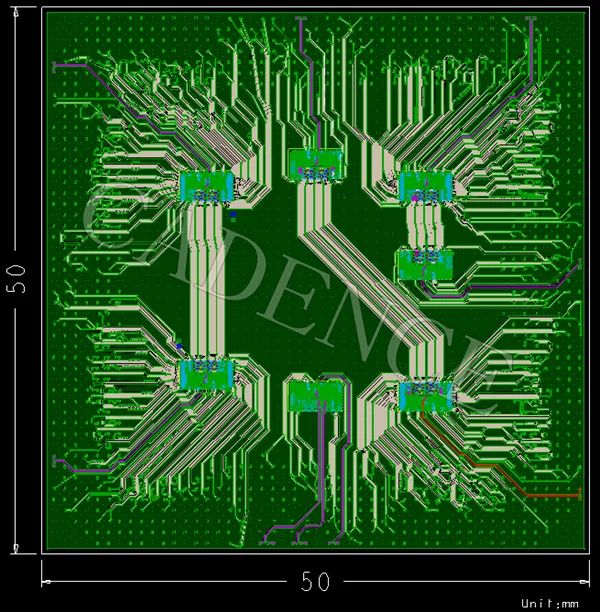

廣泛的測試旨在最大限度地覆蓋用例,這一直是 Cadence 芯片驗證的基石。為此,我們在臺積電 N4 工藝上的 UCIe 測試芯片集成了三對(而非一對)芯片間連接,成功演示了跨多種通道長度的數據傳輸。芯片對間距分別為 5mm、15mm 和 25mm,基板尺寸為 50mm×50mm。

圖2:Cadence 采用大尺寸基板設計測試多種通道長度

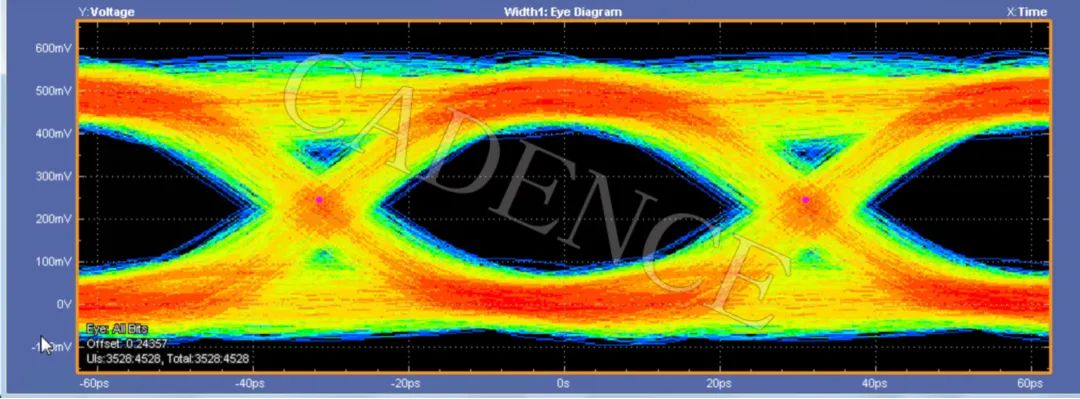

與所有 UCIe-SP 測試芯片一樣,發射端(Tx)眼圖也輸出至商用示波器,實現對信號質量的實時監測。這進一步證明了設計的穩健性,并讓我們能更深入地了解這款低功耗、高速 IP 的性能。

圖3:16GT/s 發射端輸出眼圖

(連接至示波器,PRBS23 碼型)

自 2018 年以來,Cadence 一直是高速 D2D 連接領域值得信賴的 IP 合作伙伴。此次最新的 16GT/s UCIe 流片演示延續了我們的征程。

歡迎聯系我們,一起探討 Cadence 豐富的 D2D 經驗及廣泛的芯片間連接 IP 組合如何助力加速您的分解式設計。

-

臺積電

+關注

關注

44文章

5803瀏覽量

176301 -

Cadence

+關注

關注

68文章

1011瀏覽量

146920 -

眼圖

+關注

關注

1文章

76瀏覽量

21764

原文標題:硅片一次性成功:Cadence 基于臺積電 N4 工藝交付 16GT/s UCIe Gen1 IP

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智原科技持續擴大UMC 14納米工藝IP布局

9DBL0255/9DBL0455:PCIe Gen1 - 7時鐘扇出緩沖器的設計與應用

1.4nm制程工藝!臺積電公布量產時間表

TUSB8043:四端口 USB 3.1 Gen1 集線器的深度解析

TUSB8042A四端口USB 3.2 x1 Gen1集線器:特性、應用與設計要點

Cadence AI芯片與3D-IC設計流程支持臺積公司N2和A16工藝技術

智原推出最新SerDes IP持續布局聯電22納米IP解決方案

智原科技推出最新SerDes IP持續布局聯電22納米IP解決方案

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

小米玄戒O1、聯發科天璣9400e與高通驍龍8s Gen4的全面對比分析

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內存IP系統解決方案

西門子與臺積電合作推動半導體設計與集成創新 包括臺積電N3P N3C A14技術

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

Cadence基于臺積電N4工藝交付16GT/s UCIe Gen1 IP

Cadence基于臺積電N4工藝交付16GT/s UCIe Gen1 IP

評論