SN65LVDS96 LVDS SERDES接收器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn) 在電子設(shè)計(jì)領(lǐng)域,數(shù)據(jù)傳輸?shù)母咝院头€(wěn)定性至關(guān)重要。LVDS(Low-Voltage Differential

2026-01-04 11:15:05 181

181 深入解析SN65LVDS93 LVDS串行器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn) 在電子工程師的日常工作中,選擇合適的芯片來(lái)實(shí)現(xiàn)高效的數(shù)據(jù)傳輸至關(guān)重要。今天,我們就來(lái)詳細(xì)探討一下德州儀器(TI

2026-01-04 11:15:02 183

183 深入剖析SN65LVDS95 LVDS 串行器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn) 在高速數(shù)據(jù)傳輸領(lǐng)域,LVDS(低電壓差分信號(hào))技術(shù)憑借其低功耗、高抗干擾能力和高速率傳輸?shù)膬?yōu)勢(shì),成為眾多工程師的首選。TI

2026-01-04 11:10:14 197

197 SN65LVDS94 LVDS 串行解串接收器:設(shè)計(jì)與應(yīng)用全解析 在當(dāng)今高速數(shù)據(jù)傳輸?shù)碾娮宇I(lǐng)域,LVDS(低電壓差分信號(hào))技術(shù)憑借其高速度、低功耗和低電磁干擾等優(yōu)勢(shì),成為了眾多工程師的首選。今天

2026-01-04 11:10:06 162

162 SN65LVDS86A/SN75LVDS86A FlatLink接收器的技術(shù)解析與應(yīng)用指南 在電子設(shè)備的設(shè)計(jì)中,信號(hào)的高效、穩(wěn)定傳輸至關(guān)重要。今天咱們來(lái)聊聊德州儀器(TI)的SN65LVDS

2026-01-04 10:25:15 76

76 SN75LVDS32與SN75LVDS9637高速差分線接收器:設(shè)計(jì)與應(yīng)用指南 在高速數(shù)據(jù)傳輸領(lǐng)域,低電壓差分信號(hào)(LVDS)技術(shù)憑借其低功耗、高速度和抗干擾能力強(qiáng)等優(yōu)點(diǎn),得到了廣泛應(yīng)用。德州儀器

2026-01-04 09:50:06 199

199 高速差分線路接收器SN75LVDS32和SN75LVDS9637的全面剖析 在電子工程師的日常工作中,高速數(shù)據(jù)傳輸?shù)姆€(wěn)定性和效率是至關(guān)重要的。今天,我們就來(lái)深入探討兩款高性能的高速差分線路接收器

2026-01-04 09:50:03 196

196 高速差分線路驅(qū)動(dòng)器SN75LVDS31與SN75LVDS9638的深度剖析 在電子工程師的日常工作中,高速差分線路驅(qū)動(dòng)器是實(shí)現(xiàn)高效數(shù)據(jù)傳輸?shù)年P(guān)鍵組件。今天就來(lái)詳細(xì)探討一下德州儀器(TI

2026-01-04 09:45:11 197

197 SNx5LVDS3xxxx高速差分線路接收器深度解析 在高速數(shù)據(jù)傳輸領(lǐng)域,低電壓差分信號(hào)(LVDS)技術(shù)憑借其低功耗、高速度和抗干擾能力強(qiáng)等優(yōu)勢(shì),得到了廣泛應(yīng)用。今天,我們就來(lái)詳細(xì)探討德州儀器(TI

2026-01-04 09:20:09 202

202 高速差分線路驅(qū)動(dòng)器SN75LVDS31與SN75LVDS9638的設(shè)計(jì)與應(yīng)用 在高速數(shù)據(jù)傳輸?shù)碾娮釉O(shè)計(jì)領(lǐng)域,差分線路驅(qū)動(dòng)器是至關(guān)重要的組件。今天,我們就來(lái)深入探討德州儀器(TI)的兩款高速差分線

2026-01-04 09:20:02 197

197 深入解析SNx5LVDS3xx高速差分線驅(qū)動(dòng)器 在高速數(shù)據(jù)傳輸?shù)念I(lǐng)域中,差分線驅(qū)動(dòng)器扮演著至關(guān)重要的角色。今天,我們就來(lái)詳細(xì)探討一下德州儀器(TI)的SNx5LVDS3xx系列高速差分線驅(qū)動(dòng)器,包括

2025-12-31 17:10:02 1178

1178 SNx5LVDS3xx高速差分線路驅(qū)動(dòng)器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn) 在電子設(shè)計(jì)領(lǐng)域,高速差分線路驅(qū)動(dòng)器是實(shí)現(xiàn)高速數(shù)據(jù)傳輸?shù)年P(guān)鍵組件。今天,我們就來(lái)詳細(xì)探討一下德州儀器(TI)的SNx5LVDS3xx系列

2025-12-31 17:05:27 1144

1144 深入解析SN65LVDS109與SN65LVDS117:高性能LVDS重復(fù)器的卓越之選 在電子設(shè)計(jì)領(lǐng)域,數(shù)據(jù)傳輸?shù)母咝浴⒎€(wěn)定性和低功耗一直是工程師們追求的目標(biāo)。今天,我們將深入探討德州儀器(TI

2025-12-31 16:35:09 73

73 深入剖析SN65LVDS116:16端口LVDS中繼器的卓越性能與應(yīng)用 在電子設(shè)計(jì)領(lǐng)域,信號(hào)傳輸?shù)姆€(wěn)定性、速度和準(zhǔn)確性至關(guān)重要。今天,我們將深入探討德州儀器(Texas Instruments

2025-12-31 16:35:06 85

85 《SN65LVDS109與SN65LVDS117:LVDS重復(fù)器的卓越之選》 在電子設(shè)計(jì)領(lǐng)域,數(shù)據(jù)傳輸?shù)母咝浴⒎€(wěn)定性與精確性一直是工程師們追求的目標(biāo)。今天,我們聚焦于德州儀器(TI)推出的兩款

2025-12-31 16:15:03 78

78 深入解析SNx5LVDS3xx高速差分線驅(qū)動(dòng)器 在電子設(shè)計(jì)領(lǐng)域,高速差分線驅(qū)動(dòng)器是實(shí)現(xiàn)高速數(shù)據(jù)傳輸?shù)年P(guān)鍵組件。今天我們就來(lái)詳細(xì)探討德州儀器(TI)的SNx5LVDS3xx系列高速差分線驅(qū)動(dòng)器,包括其

2025-12-31 16:00:10 70

70 Texas Instruments SN65LVDS108:8端口LVDS中繼器的技術(shù)剖析與應(yīng)用探索 在高速數(shù)據(jù)傳輸和處理的電子世界里,低電壓差分信號(hào)(LVDS)技術(shù)憑借其低功耗、低噪聲、高抗

2025-12-31 16:00:02 69

69 解析SN65LVDS10x:4端口LVDS與4端口TTL - LVDS中繼器的卓越性能 在電子設(shè)計(jì)的領(lǐng)域中,數(shù)據(jù)傳輸?shù)母咝院头€(wěn)定性始終是工程師們關(guān)注的核心。今天,我們將深入探討德州儀器(TI

2025-12-31 15:50:06 80

80 電子工程師必看:SN65LVDS10x系列解析與設(shè)計(jì)指南 在電子設(shè)計(jì)領(lǐng)域,數(shù)據(jù)傳輸?shù)母咝浴⒎€(wěn)定性和低功耗一直是我們追求的目標(biāo)。TI的SN65LVDS10x系列LVDS和TTL

2025-12-31 15:50:03 72

72 深入解析SN65LVDS047:高性能LVDS四通道差分線驅(qū)動(dòng)器 在高速數(shù)據(jù)傳輸?shù)碾娮釉O(shè)計(jì)領(lǐng)域,低電壓差分信號(hào)(LVDS)技術(shù)憑借其低功耗、高速度和抗干擾能力強(qiáng)等優(yōu)勢(shì),成為了眾多工程師的首選。今天

2025-12-31 14:45:09 77

77 深入解析SNx5LVDS3xx高速差分線驅(qū)動(dòng)器 在現(xiàn)代電子系統(tǒng)中,高速數(shù)據(jù)傳輸和低功耗設(shè)計(jì)是至關(guān)重要的需求。SNx5LVDS3xx系列高速差分線驅(qū)動(dòng)器正是為滿足這些需求而設(shè)計(jì)的,它能夠在多種應(yīng)用場(chǎng)

2025-12-31 14:10:25 88

88 高速數(shù)據(jù)傳輸利器:SNx5LVDS3xx系列LVDS接收器深度解析 在高速數(shù)據(jù)傳輸領(lǐng)域,低電壓差分信號(hào)(LVDS)技術(shù)憑借其低功耗、高速度和抗干擾能力強(qiáng)等優(yōu)勢(shì),成為眾多應(yīng)用場(chǎng)景的首選。德州儀器(TI

2025-12-31 13:50:09 72

72 SN65LVDS048A:高性能LVDS四通道差分線路接收器的深度解析 在高速數(shù)據(jù)傳輸?shù)念I(lǐng)域中,低電壓差分信號(hào)(LVDS)技術(shù)憑借其低功耗、高速率和抗干擾能力強(qiáng)等優(yōu)勢(shì),成為了眾多工程師的首選。TI

2025-12-31 13:50:02 72

72 解析高速差分接收器SN65LVDS/T系列:LVDS技術(shù)的卓越之選 在高速數(shù)據(jù)傳輸領(lǐng)域,低電壓差分信號(hào)(LVDS)技術(shù)憑借其高速、低功耗、低噪聲等優(yōu)勢(shì),成為了眾多工程師的首選。德州儀器(TI

2025-12-31 11:20:12 128

128 探索SN75LVDS84A和SN65LVDS84AQ FlatLink發(fā)射器:高性能與低功耗的完美結(jié)合 在電子設(shè)備的設(shè)計(jì)中,數(shù)據(jù)傳輸?shù)母咝院头€(wěn)定性至關(guān)重要。今天,我們將深入探討德州儀器(TI

2025-12-31 10:20:11 157

157 解鎖SN65LVDS86A/SN75LVDS86A FlatLink接收器:高速數(shù)據(jù)傳輸新方案 在電子設(shè)備的設(shè)計(jì)中,數(shù)據(jù)的高效、穩(wěn)定傳輸一直是工程師們關(guān)注的重點(diǎn)。今天,我們就來(lái)深入探討一下德州儀器

2025-12-31 10:20:02 150

150 深入解析SN65LVDS122和SN65LVDT122:1.5-Gbps 2×2 LVDS交叉點(diǎn)開(kāi)關(guān) 在高速信號(hào)處理領(lǐng)域,找到一款性能卓越、功能多樣的交叉點(diǎn)開(kāi)關(guān)至關(guān)重要。今天,我們就來(lái)深入探討TI

2025-12-30 14:15:10 111

111 SN65LVDS95-Q1 LVDS SERDES 發(fā)射器:特性、應(yīng)用與設(shè)計(jì)指南 在電子工程師的日常工作中,高速數(shù)據(jù)傳輸和低電磁干擾(EMI)設(shè)計(jì)是常見(jiàn)的挑戰(zhàn)。今天,我們就來(lái)深入探討一下德州儀器

2025-12-30 09:45:09 68

68 SN65LVDS95 - EP是一款LVDS(低壓差分信號(hào))串行器/解串器發(fā)射器,專為滿足工業(yè)溫度范圍( - 40°C至85°C)的可靠運(yùn)行而

2025-12-30 09:45:06 80

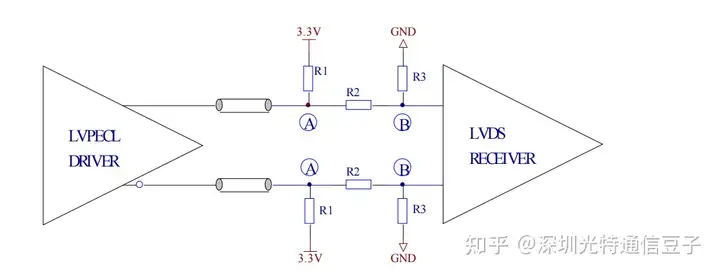

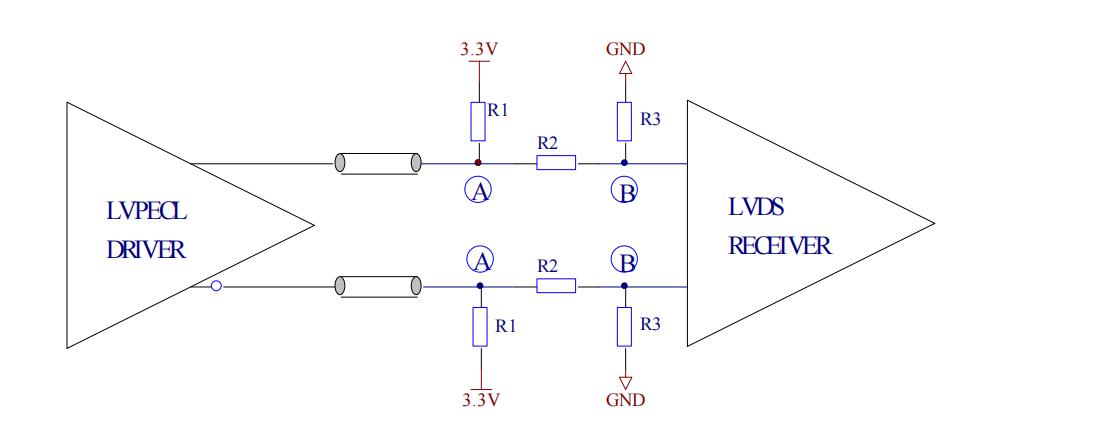

80 20和SN65LVP20芯片,看看它們?cè)?b class="flag-6" style="color: red">LVPECL和LVDS信號(hào)處理方面的卓越表現(xiàn)。 文件下載: sn65lvp20.pdf 一、產(chǎn)品概述 SN65LVDS20和SN65LVP20是將高速差分接收器

2025-12-29 16:40:03 151

151 高速差分線路驅(qū)動(dòng)器SN75LVDS31與SN75LVDS9638的技術(shù)剖析 在高速數(shù)據(jù)傳輸?shù)念I(lǐng)域中,差分線路驅(qū)動(dòng)器扮演著至關(guān)重要的角色。今天,我們就來(lái)深入探討德州儀器(TI)推出的兩款高速差分線

2025-12-29 16:25:06 126

126 深入剖析SN75LVDS83B:LVDS顯示傳輸?shù)睦硐胫x 在當(dāng)今的電子設(shè)備中,顯示技術(shù)的發(fā)展日新月異,對(duì)于高質(zhì)量、高速數(shù)據(jù)傳輸?shù)男枨笠苍絹?lái)越迫切。LVDS(Low-Voltage

2025-12-25 10:20:09 283

283 深入剖析SN75LVDS83A:LVDS顯示發(fā)射機(jī)的卓越之選 一、引言 在當(dāng)今的電子顯示領(lǐng)域,高效、穩(wěn)定的數(shù)據(jù)傳輸至關(guān)重要。SN75LVDS83A作為一款Flatlink?發(fā)射機(jī),憑借其出色的性能

2025-12-25 09:30:12 135

135 就來(lái)深入剖析這款器件,探討其特點(diǎn)、應(yīng)用以及設(shè)計(jì)要點(diǎn)。 文件下載: sn65lvds93a.pdf 特性亮點(diǎn) 寬溫度范圍與多種封裝 SN65LVDS93A支持工業(yè)溫度范圍 -40°C 至 85°C,這

2025-12-25 09:30:09 203

203 深入解析SN65EPT23:3.3V ECL差分LVPECL/LVDS到LVTTL/LVCMOS轉(zhuǎn)換器 在電子設(shè)計(jì)領(lǐng)域,信號(hào)電平轉(zhuǎn)換是一個(gè)常見(jiàn)且關(guān)鍵的需求。今天我們來(lái)詳細(xì)探討德州儀器(TI

2025-12-24 17:45:12 472

472 、SN65LVDS822的特性亮點(diǎn) 1. 強(qiáng)大的解串能力 SN65LVDS822具備4:27 LVDS到CMOS的解串功能,像素時(shí)鐘范圍為4 MHz至54 MHz,能

2025-12-23 10:15:03 172

172 深入剖析SN65LVDS93A-Q1:高性能LVDS發(fā)射器的設(shè)計(jì)與應(yīng)用 在電子設(shè)計(jì)領(lǐng)域,數(shù)據(jù)傳輸?shù)母咝院头€(wěn)定性至關(guān)重要。SN65LVDS93A-Q1作為一款A(yù)EC-Q100合格的FlatLink

2025-12-22 15:20:02 191

191 : sn65lvds93b.pdf 一、SN65LVDS93B特性亮點(diǎn) 1. 寬溫度范圍與多樣封裝 SN65LVDS93B適用于 -40°C 至 85°C 的工業(yè)溫度范圍

2025-12-18 11:35:12 251

251 SNx5LVDS3xx高速差分線路驅(qū)動(dòng)器:設(shè)計(jì)與應(yīng)用全解析 在電子工程師的日常設(shè)計(jì)工作中,高速差分線路驅(qū)動(dòng)器是實(shí)現(xiàn)高效數(shù)據(jù)傳輸不可或缺的組件。今天,我們就來(lái)深入探討一下SNx5LVDS3xx系列高速

2025-12-17 17:40:06 550

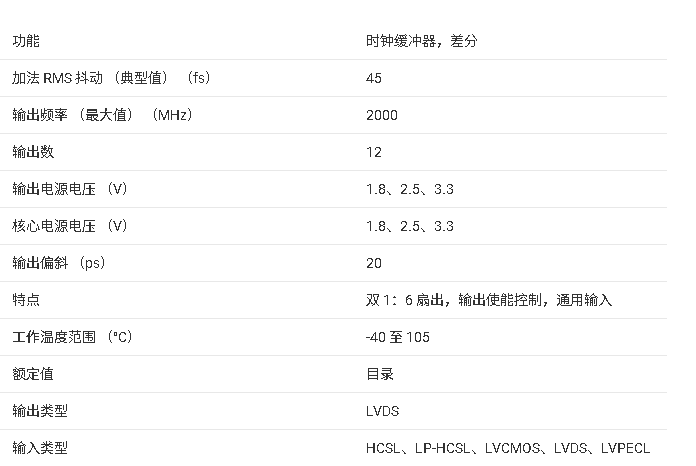

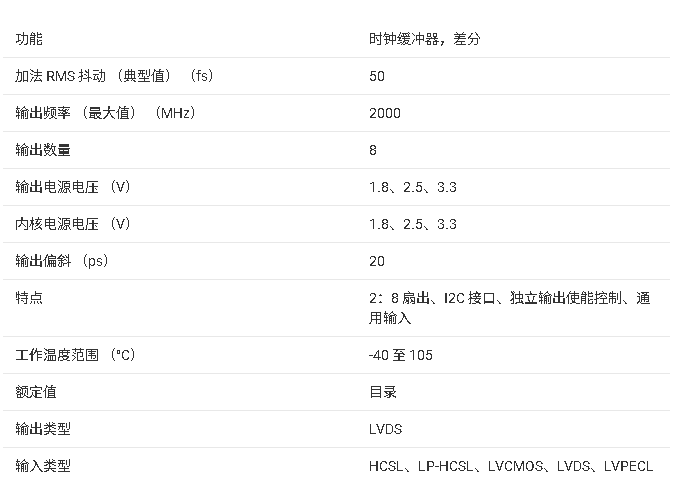

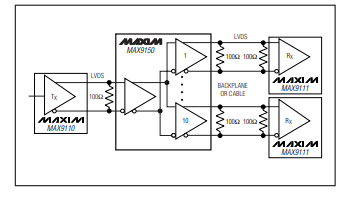

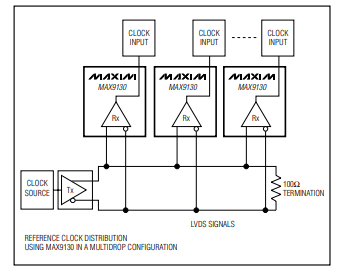

550 ZYNALOG徴格半導(dǎo)體正式推出ZGN4XXX系列高速接口芯片。該系列涵蓋LVDS線路驅(qū)動(dòng)器、LVDS線路接收器以及M-LVDS收發(fā)器,為您的背板數(shù)據(jù)傳輸、有線數(shù)據(jù)傳輸、時(shí)鐘分配提供高性能、高可靠性

2025-11-27 13:32:08 564

564

在高速數(shù)據(jù)傳輸領(lǐng)域,低電壓差分信號(hào)(LVDS)技術(shù)憑借其高速率、低功耗和低電磁干擾等優(yōu)勢(shì),得到了廣泛應(yīng)用。德州儀器(TI)的SN65LVDS33、SN65LVDT33、SN65LVDS

2025-11-26 16:16:48 517

517

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論