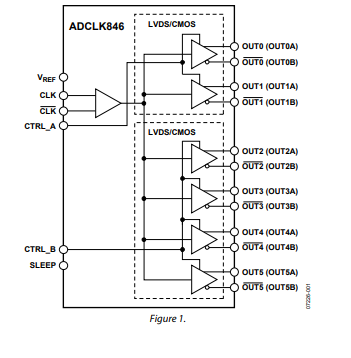

概述

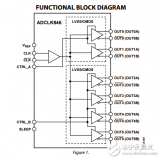

ADCLK846是一款針對(duì)低抖動(dòng)和低功耗優(yōu)化的1.2 GHz/250 MHz、LVDS/CMOS、扇出緩沖器。可配置范圍為6 LVDS至12 CMOS輸出,包括LVDS和CMOS輸出的組合。兩條控制線路用于確定固定模塊輸出是LVDS輸出還是CMOS輸出。

時(shí)鐘輸入接受各種單端和差分邏輯電平,包括LVPECL、LVDS、HSTL、CML和CMOS。

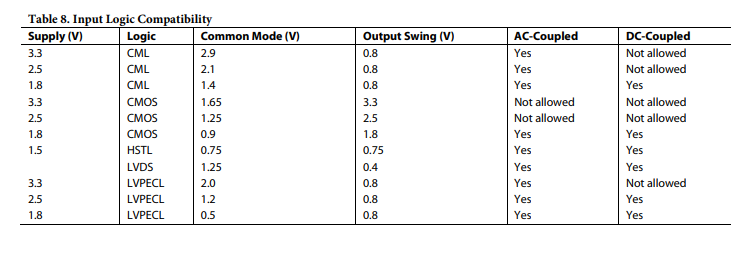

表8提供用于各類連接的接口選項(xiàng)。SLEEP引腳使能睡眼模式以關(guān)斷器件的電源。

這款器件采用24引腳LFCSP封裝,工作溫度范圍為?40℃至+85℃的標(biāo)準(zhǔn)工業(yè)溫度范圍。

數(shù)據(jù)表:*附件:ADCLK846 1.8 V、6 LVDS 12 CMOS輸出低功耗時(shí)鐘扇出緩沖器技術(shù)手冊(cè).pdf

特性

- 可選LVDS/CMOS輸出

- 多達(dá)6 LVDS(1.2 GHz)或者12 CMOS(250 MHz)輸出

- 每通道功耗:<16 mW(工作頻率為100 MHz)

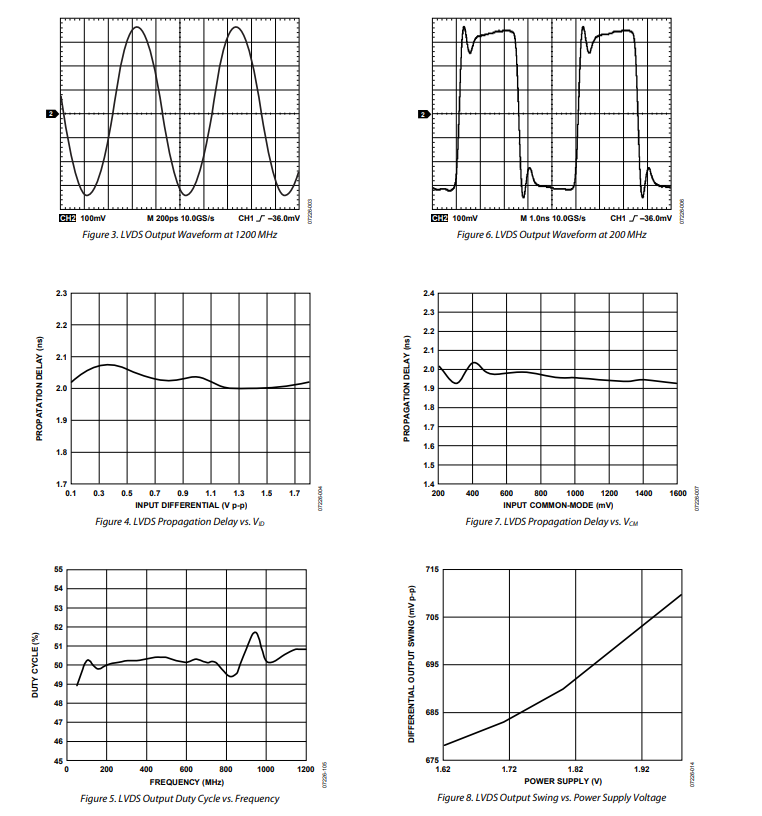

- 綜合抖動(dòng):54 fs(12 kHz至20 MHz)

- 附加寬帶抖動(dòng):100 fs

- 傳播延遲:2.0 ns(LVDS)

- 輸出上升/下降時(shí)間:135 ps(LVDS)

- 輸出至輸出偏斜:65 ps(LVDS)

- 睡眠模式

- 引腳可編程控制

- 1.8 V電源

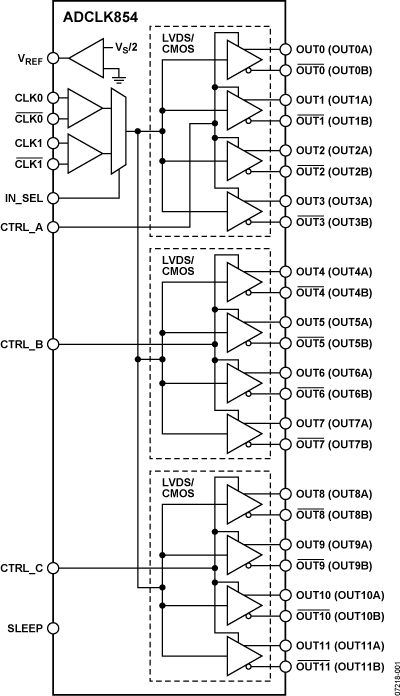

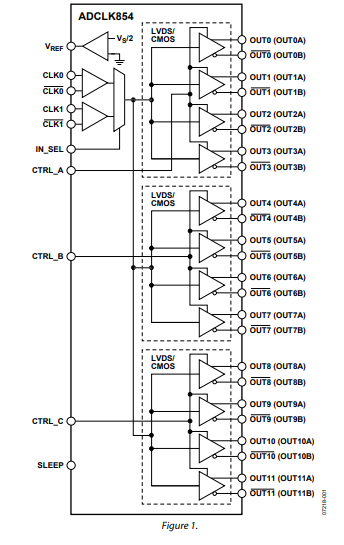

框圖

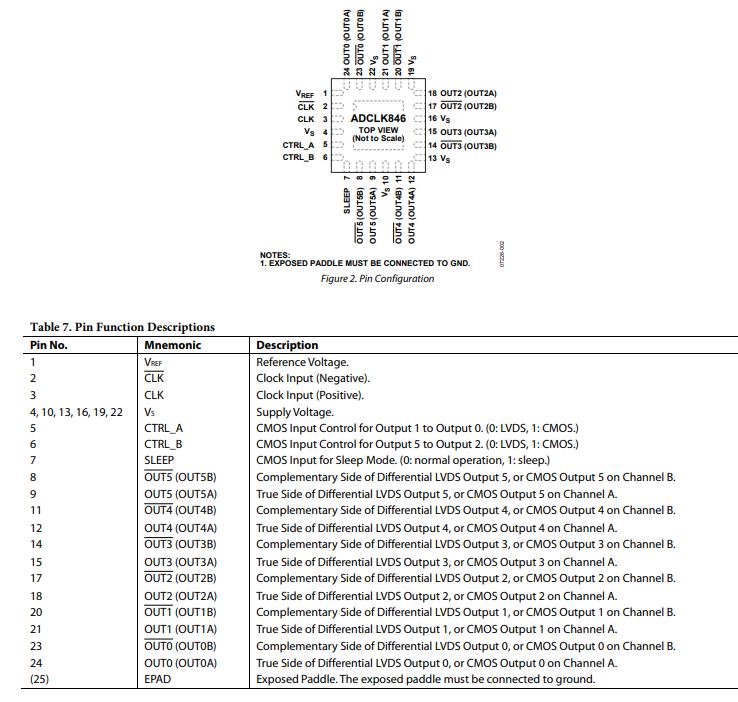

引腳配置描述

典型性能特征

功能描述

ADCLK846的時(shí)鐘輸入會(huì)分配到所有輸出通道。每個(gè)通道組可通過引腳編程設(shè)置為LVDS或CMOS電平。這允許從LVDS和CMOS邏輯的組合中選擇6到12種輸出配置,以及使用這兩種邏輯的其他組合。

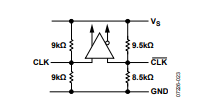

時(shí)鐘輸入

ADCLK846的差分輸入在內(nèi)部進(jìn)行自偏置。時(shí)鐘輸入有一個(gè)電阻分壓器,可設(shè)置共模電平為輸入的互補(bǔ)信號(hào)。應(yīng)將信號(hào)偏置到比真值低30 mV,以避免在輸入信號(hào)停止時(shí)出現(xiàn)振蕩。等效輸入電路見圖20。

輸入可以是交流耦合或直流耦合。表8提供了輸入邏輯兼容性的參考。如果需要單端輸入,可以通過交流或直流耦合到差分輸入的一側(cè)來實(shí)現(xiàn)。將另一個(gè)輸入通過電容旁路到地。

請(qǐng)注意,抖動(dòng)性能會(huì)隨著低輸入斜率而下降,如圖11所示。有關(guān)不同端接方案,請(qǐng)參見圖28至圖32。圖20. ADCLK846輸入級(jí)

交流耦合應(yīng)用

當(dāng)需要交流耦合時(shí),ADCLK846提供兩種選擇。第一種選擇不需要外部組件(不包括隔直電容);它允許用戶將參考信號(hào)耦合到時(shí)鐘輸入引腳(見圖31)。

第二種選擇允許使用**V_{REF}**引腳為ADCLK846設(shè)置直流偏置電平。V_{REF}引腳可以通過電阻連接到CLK和overline{CLK}。這種方法允許在ADCLK846處對(duì)信號(hào)進(jìn)行較低阻抗的端接(見圖32)。

內(nèi)部偏置電阻仍與外部偏置電阻并聯(lián)。相對(duì)較高的內(nèi)部電阻使得外部到**V_{REF}**的端接起主導(dǎo)作用。當(dāng)不希望稍微偏移輸入時(shí),這也很有用。如前所述,提到的僅指內(nèi)部偏置。

時(shí)鐘輸出

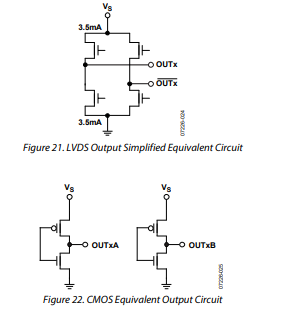

每個(gè)驅(qū)動(dòng)器由一個(gè)差分LVDS輸出或兩個(gè)單端CMOS輸出組成(始終同相)。當(dāng)LVDS驅(qū)動(dòng)器啟用時(shí),相應(yīng)的CMOS驅(qū)動(dòng)器處于三態(tài)。當(dāng)CMOS驅(qū)動(dòng)器啟用時(shí),相應(yīng)的LVDS驅(qū)動(dòng)器斷電并處于三態(tài)。圖21和圖22展示了等效輸出級(jí)。

控制和功能引腳

CTRL_A邏輯選擇

CTRL_A為輸出1和輸出0選擇CMOS(高電平)或LVDS(低電平)邏輯。此引腳有一個(gè)內(nèi)部200 kΩ下拉電阻。

CTRL_B邏輯選擇

CTRL_B為輸出5、輸出4、輸出3和輸出2選擇CMOS(高電平)或LVDS(低電平)邏輯。此引腳有一個(gè)內(nèi)部200 kΩ下拉電阻。

睡眠模式

SLEEP使芯片除帶隙基準(zhǔn)外的部分?jǐn)嚯姟T撦斎霝楦唠娖綍r(shí),會(huì)使輸出進(jìn)入高阻態(tài)。此引腳有一個(gè)200 kΩ下拉電阻。控制引腳在睡眠模式下仍可操作。

電源

ADCLK846的**V_{S}**需要1.8 V ± 5%的電源。最佳實(shí)踐建議在印刷電路板(PCB)上用足夠的電容(>10 μF)對(duì)電源進(jìn)行旁路,并在盡可能靠近器件的位置用足夠的電容(0.1 μF)對(duì)所有電源引腳進(jìn)行旁路。ADCLK846評(píng)估板(ADCLK846/PCBZ)的布局提供了一個(gè)良好的布局示例。

外露金屬焊盤

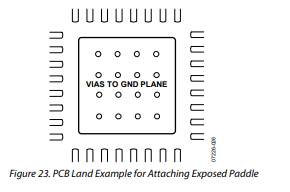

ADCLK846封裝上的外露金屬焊盤用于電氣連接,同時(shí)也增強(qiáng)散熱。為使器件正常工作,該焊盤必須正確連接到地(GND)。ADCLK846通過其外露焊盤散熱。PCB充當(dāng)ADCLK846的散熱器。PCB連接必須為熱量從頂層向下傳導(dǎo)到接地層等更大散熱區(qū)域提供良好的熱路徑。這需要一個(gè)由過孔組成的柵格。圖23給出了一個(gè)示例。

-

CMOS

+關(guān)注

關(guān)注

58文章

6224瀏覽量

243265 -

緩沖器

+關(guān)注

關(guān)注

6文章

2234瀏覽量

49018 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1998瀏覽量

135199 -

lvds

+關(guān)注

關(guān)注

2文章

1239瀏覽量

70125

發(fā)布評(píng)論請(qǐng)先 登錄

請(qǐng)問ADCLK846未用的LVDS一般如何處理?

ADCLK846/PCBZ,ADCLK954高性能時(shí)鐘扇出緩沖器評(píng)估板

ADCLK846,pdf datasheet (Low Po

1.8伏6LVDS/12 CMOS輸出低功耗時(shí)鐘扇出緩沖器adclk846數(shù)據(jù)表

1.8V,12-lvds/24-cmos輸出低功耗時(shí)鐘扇出緩沖器adclk854數(shù)據(jù)表

ADCLK846 1.8 V、6 LVDS/12 CMOS輸出低功耗時(shí)鐘扇出緩沖器

ADCLK854 1.8 V、12 LVDS/24 CMOS輸出的低功耗時(shí)鐘扇出緩沖器

ADCLK846/PCBZ 時(shí)鐘緩沖器參考設(shè)計(jì)

ADCLK846:1.8 V、6 LVDS/12 CMOS輸出低功耗時(shí)鐘扇出緩沖器

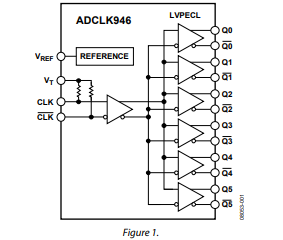

ADCLK946:六路LVPECL輸出,SiGe時(shí)鐘扇出緩沖器數(shù)據(jù)表

ADCLK946采用SiGe工藝的6 LVPECL輸出時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK854 1.8 V、12 LVDS/24 CMOS輸出的低功耗時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK846 1.8 V、6 LVDS/12 CMOS輸出低功耗時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK846 1.8 V、6 LVDS/12 CMOS輸出低功耗時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

評(píng)論