概述

MAX9310A是一種快速,低扭曲1:5差分驅動器,具有可選的LVPECL輸入和LVDS輸出,設計應用于時鐘分配。這種器件的特點是具有340ps的極低傳輸延遲和48mA的電源電流。

MAX9310A工作在3V至3.6V電源范圍,適用于3.3V系統。通過2:1輸入多路復用器,選擇兩路差分輸入中的一路。輸入選擇是由CLKSEL引腳控制。

這種器件也具有同步使能功能的特點。MAX9310A的LVPECL輸入可由差分或單端信號驅動。提供一個參考電壓輸出V BB ,以便應用于單端輸入,此器件也可接收差分HSTL信號。

MAX9310A提供節省空間的20引腳TSSOP封裝,可工作在-40°C至+85°C的寬溫度范圍。

數據表:*附件:MAX9310A 1比5時鐘驅動器,可選擇LVPECL輸入 單端輸入與LVDS輸出技術手冊.pdf

應用

- 自動測試設備(ATE)

- 局端背板時鐘分配

- 數據和時鐘驅動器與緩沖器

- DSLAM

- 無線基站

特性

- 保證1.0GHz工作頻率

- 8.0ps輸出至輸出扭曲

- 340ps傳輸延遲

- 接收LVPECL和差分HSTL輸入

- 同步輸出使能/禁止

- 兩路可選擇的差分輸入

- 3V至3.6V電源電壓

- 用于單端工作的片內參考電壓

- ESD保護:±2kV (人體模型)

- 輸入開路時,輸入偏置電阻驅動輸出為低

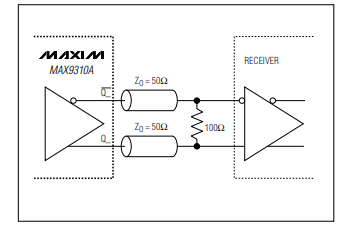

應用電路

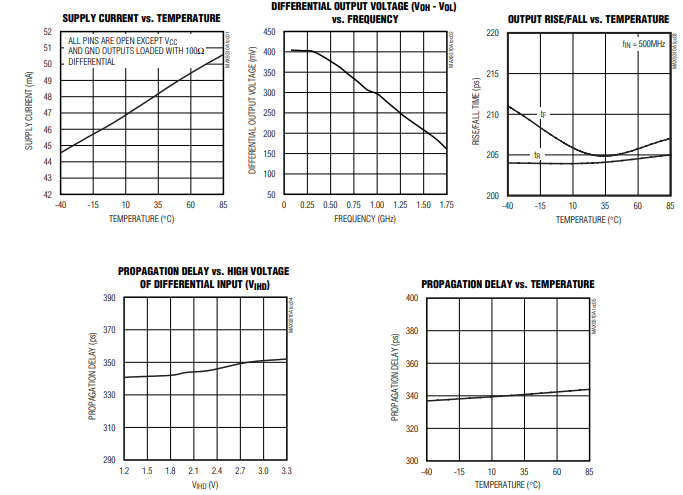

典型操作特性

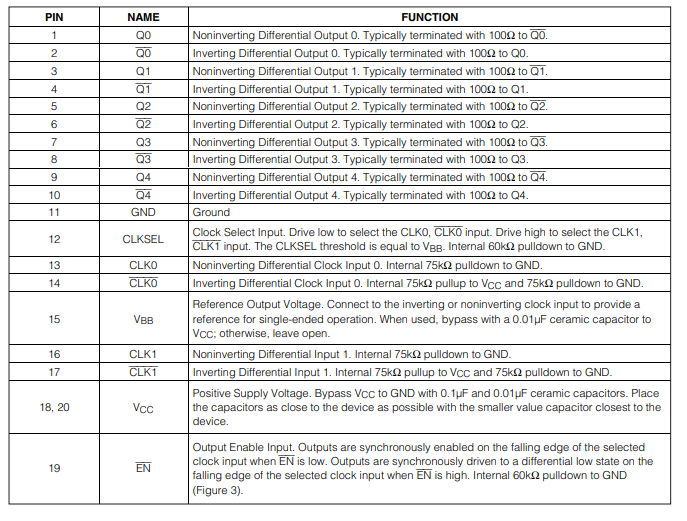

引腳配置描述

詳細說明

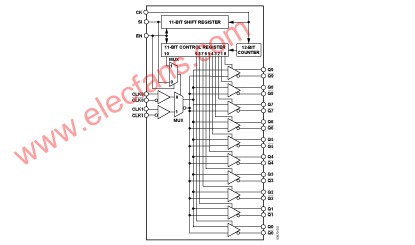

MAX9310是一款低偏斜的1:5差分驅動器,具備兩個可選的LVPECL輸入和LVDS輸出,適用于時鐘分配應用。選通時鐘接收差分輸入信號,并將其復制到五個獨立的差分LVDS輸出。輸入由內部偏置電阻進行偏置,當輸入開路時,輸出為差分低電平。該芯片支持單端輸入操作,器件保證在高達1.0GHz的頻率下工作,LVDS輸出電平符合EIA/TIA - 644標準 。

MAX9310A的設計工作電壓范圍為3V至3.6V,適用于標稱3.3V電源的系統。

差分LVPECL輸入

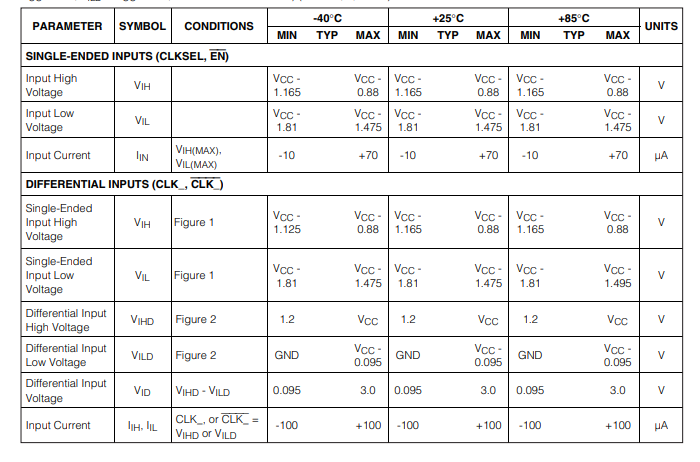

MAX9310A有兩個差分對,用于接收LVPECL/HSTL輸入信號,并且可通過VBB電壓基準配置為接受單端LVPECL輸入。每個差分輸入對都能獨立進行端接。一個選擇引腳(CLKSEL)用于激活所需的輸入。施加到輸入的差分信號的最大幅度為3V。差分信號的高電平和低電平(VHD和VLD)以及差分輸入電壓(VIH - VIL)可同時應用。

單端輸入和VBB

差分輸入可配置為通過VBB參考電壓接受單端輸入。在非反相情況下,通過將VBB連接到CLK_輸入并施加單端信號到CLK_輸入來產生單端輸入。類似地,在反相情況下,通過將VBB連接到CLK_輸入并施加單端信號到CLK_輸入來產生單端輸入。使用差分配置的單端輸入(帶VBB)時,單端輸入可以由Vcc和地驅動,或者由一個單端LVPECL信號驅動。注意,單端信號的擺幅至少為95mV。

同步使能

MAX9310的輸出在差分低電平狀態下同步使能和禁用,以消除選通時鐘脈沖中的短脈沖。EN連接到輸入的邊沿觸發D觸發器的置位端。上電后,將EN驅動為低電平并切換所選時鐘輸入以啟用輸出。輸出在EN下降沿時使能。EN下降沿時,輸出設置為所選時鐘輸入的差分低電平狀態(圖3) 。

輸入偏置電阻

內部偏置電阻確保在輸入(差分)未連接的情況下輸出為低電平。反相輸入(CLK_)通過一個75kΩ下拉電阻偏置到地,同相輸入(CLK_)通過一個75kΩ上拉電阻偏置到Vcc。

差分LVDS輸出

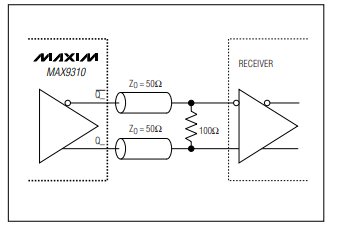

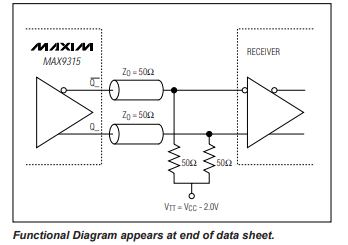

LVDS輸出必須按照典型應用電路所示,在Q和Q之間用100Ω電阻進行端接。輸出具有短路保護功能。

使用VBB參考電壓輸出時,通過一個0.01μF陶瓷電容將VBB旁路到地。如果不使用VBB參考電壓,則將其懸空。VBB參考電壓可吸收或提供500μA電流。對于依賴VBB參考電壓的輸入,請使用VBB參考電壓。

-

驅動器

+關注

關注

54文章

9110瀏覽量

156315 -

lvds

+關注

關注

2文章

1239瀏覽量

70111 -

LVPECL

+關注

關注

2文章

76瀏覽量

18883 -

差分驅動器

+關注

關注

0文章

69瀏覽量

15706

發布評論請先 登錄

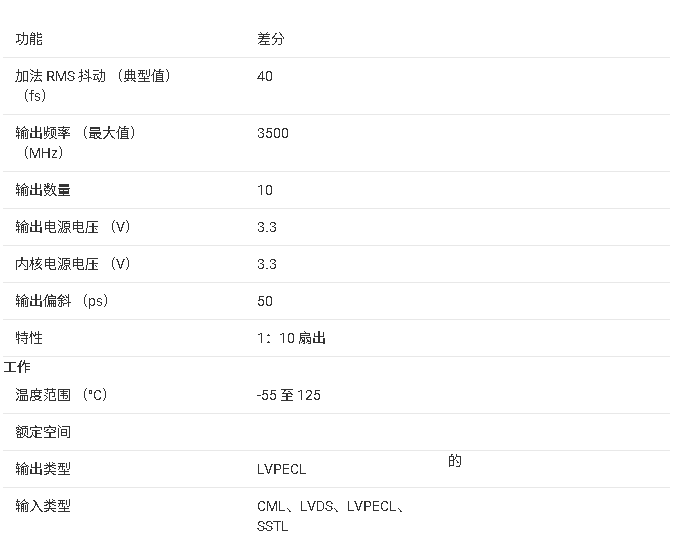

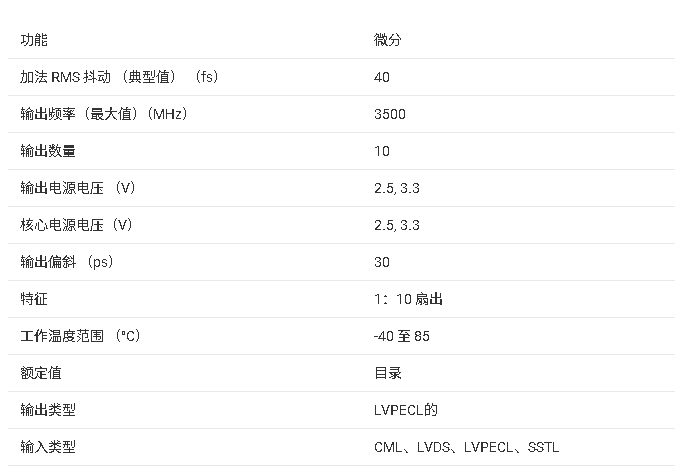

可編程低電壓1:10 LVDS時鐘驅動器ADN4670

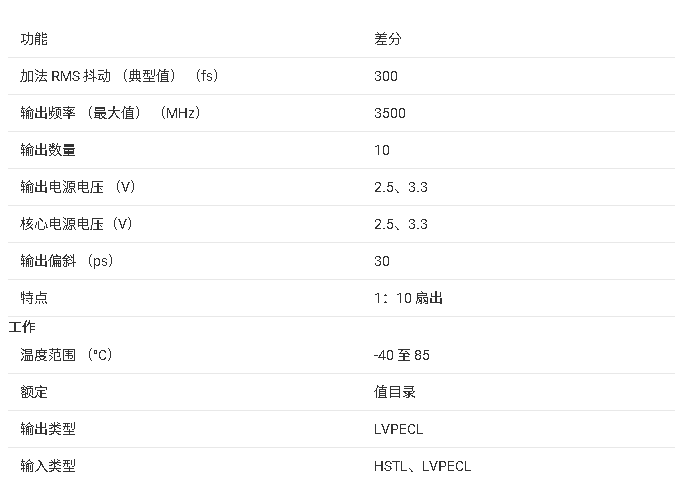

CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL數據表

CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表

MAX9310A 1:5時鐘驅動器,可選擇LVPECL輸入/單端輸入與LVDS輸出技術手冊

MAX9310A 1:5時鐘驅動器,可選擇LVPECL輸入/單端輸入與LVDS輸出技術手冊

評論