概述

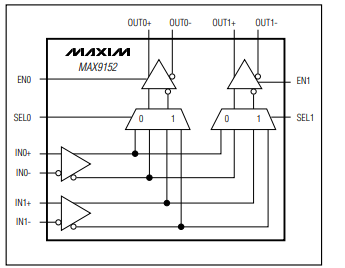

MAX9392/MAX9393雙2 x 2交叉點開關(guān)能夠?qū)崿F(xiàn)高速、低功耗、低噪聲信號切換。MAX9392/MAX9393將兩路差分輸入中的一路復(fù)用到一路或兩路低壓差分信號(LVDS)輸出。獨立的使能輸入對每路差分信號進(jìn)行通、斷控制。

數(shù)據(jù)表:*附件:MAX9392任意邏輯至LVDS、雙路、2 x 2交叉點開關(guān)技術(shù)手冊.pdf

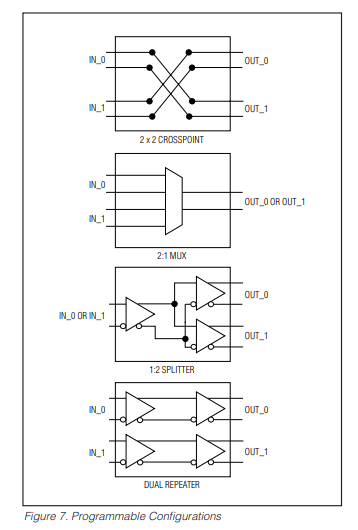

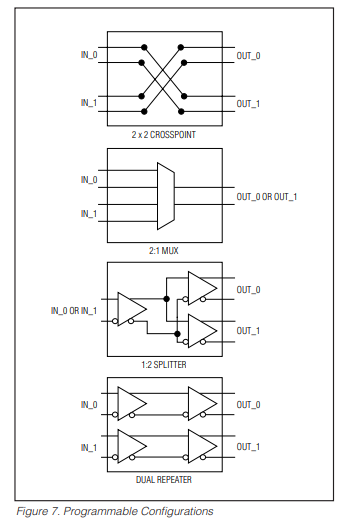

4路 LVCMOS/LVTTL邏輯輸入(每通道兩個)控制輸入與輸出之間的內(nèi)部連接。可靈活實現(xiàn)以下配置:2 x 2交叉開關(guān)、2:1復(fù)用器、1:2分配器或雙轉(zhuǎn)發(fā)器,從而使MAX9392/MAX9393可理想用作故障容錯系統(tǒng)中的保護(hù)開關(guān)、診斷器中的環(huán)回開關(guān)、時鐘/數(shù)據(jù)分配中的扇出緩沖器和信號恢復(fù)。

當(dāng)輸入未被驅(qū)動或共模電壓超出指定范圍時,故障保護(hù)電路將輸出拉至差分低電平。MAX9392為LVDS、HSTL和其它以GND為參考的差分輸入提供高電平輸入失效檢測;MAX9393為LVPECL、CML和其它以VCC為參考的差分輸入提供低電平輸入失效檢測。

具有98ps~(P-P)~ (最大值)超低抖動的偽隨機(jī)序列(PRBS)能夠在對定時誤差高度敏感的高速鏈路中保證可靠通信,特別適合需要時鐘和數(shù)據(jù)恢復(fù)的應(yīng)用,或串行器和解串器應(yīng)用。高速開關(guān)性能確保工作在1.5GHz,并保證小于67ps (最大值)的通道間偏差。

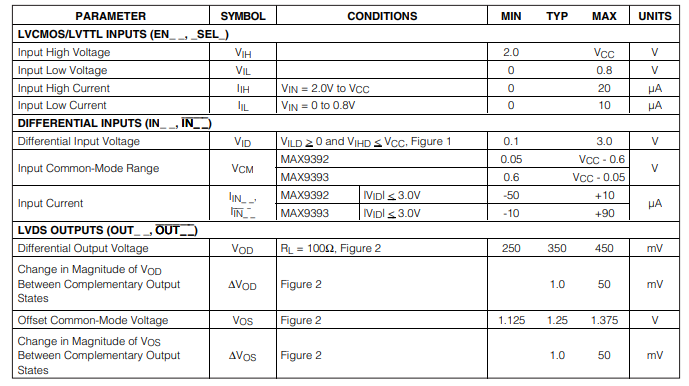

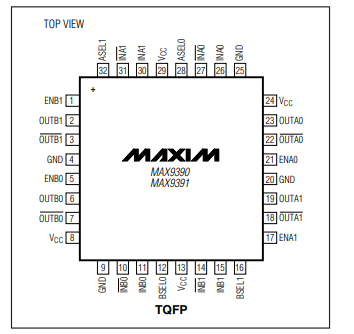

LVDS輸入、輸出兼容于TIA/EIA-644 LVDS標(biāo)準(zhǔn),LVDS輸出可驅(qū)動100Ω負(fù)載。MAX9392/MAX9393提供32引腳TQFP封裝,工作在-40°C至+85°C擴(kuò)展級溫度范圍。

交叉切換產(chǎn)品請參考MAX9390/MAX9391。

應(yīng)用

- 局端背板時鐘分配

- DSLAM

- 故障容錯系統(tǒng)

- 高速電信/數(shù)據(jù)通信設(shè)備

- 保護(hù)開關(guān)

特性

- 250mV差分輸出擺幅,可工作在1.5GHz

- 2ps

RMS(最大)隨機(jī)抖動 - 交流指標(biāo)保證接受150mV差分輸入

- 信號輸入可接受任何差分信號標(biāo)準(zhǔn)

- 用于時鐘或高速數(shù)據(jù)的LVDS輸出

- 高電平輸入失效檢測(MAX9392)

- 低電平輸入失效檢測(MAX9393)

- 3.0V至3.6V供電范圍

- LVCMOS/LVTTL邏輯輸入控制信號切換

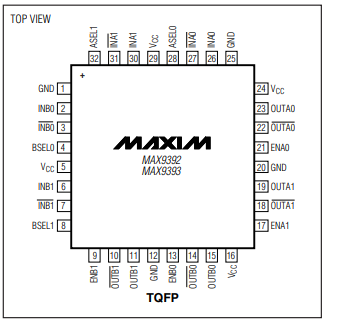

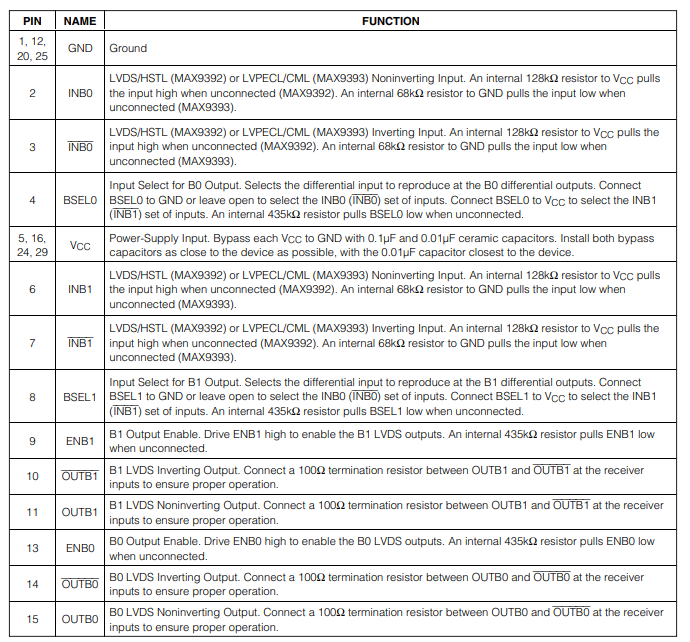

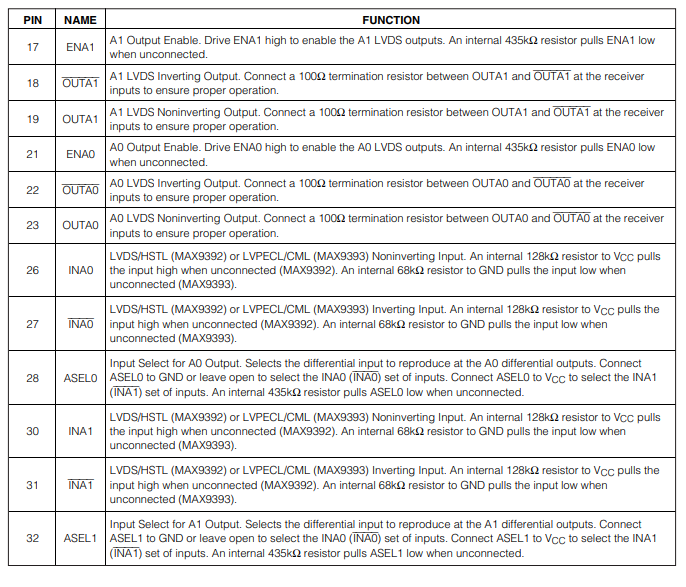

引腳描述

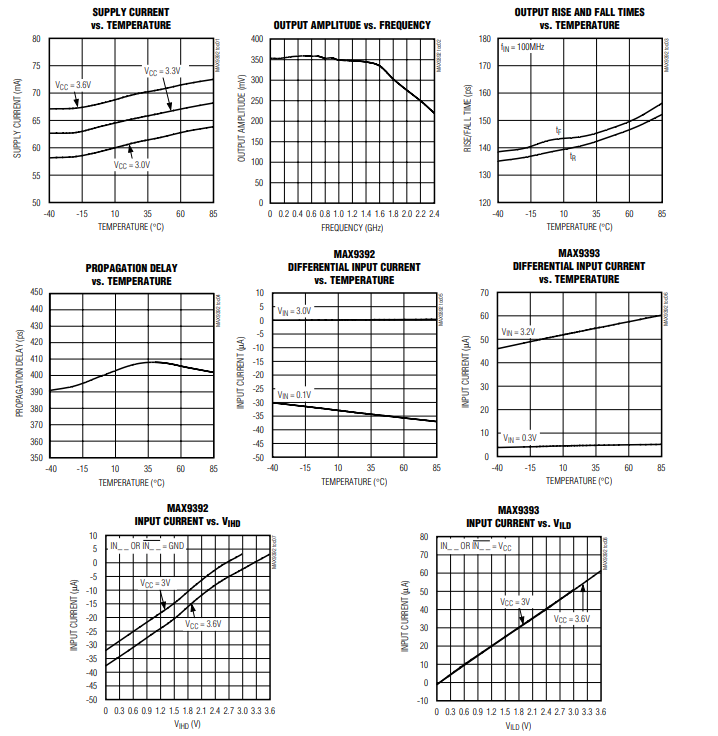

典型操作特性

詳細(xì)說明

低壓差分信號(LVDS)接口標(biāo)準(zhǔn)為受控阻抗介質(zhì)上的點對點通信提供了一種信令方法,該標(biāo)準(zhǔn)由美國國家標(biāo)準(zhǔn)協(xié)會(ANSI)TIA/EIA - 644 定義。LVDS 使用比其他通信標(biāo)準(zhǔn)更低的電壓擺幅,從而在降低電磁輻射和系統(tǒng)對噪聲敏感度的同時,實現(xiàn)更高的數(shù)據(jù)速率并降低功耗。

MAX9392/MAX9393 1.5G Hz 雙 2×2 交叉點開關(guān)優(yōu)化高速信號,實現(xiàn)點對點接口。MAX9392 支持 LVDS 和高速晶體管 - 晶體管邏輯(HSTL),而 MAX9393 接受 LVPECL 和 CML 電平。這兩款器件都將輸入信號路由至一個或兩個 LVDS 輸出。

配置為 1:2 分配器時,器件會復(fù)制所選輸入的配置,創(chuàng)建信號副本以實現(xiàn)保護(hù)切換。配置為中繼器時,器件在雙聲道緩沖器中運行。中繼可恢復(fù)信號幅度,從而實現(xiàn)隔離。在媒體段或長距離媒體傳輸中,這有助于信號傳輸。

配置為 2:1 多路復(fù)用器時,可選擇主信號或備用信號,以提供保護(hù)切換、故障轉(zhuǎn)移或其他應(yīng)用功能。

輸入故障保護(hù)

MAX9392/MAX9393 的差分輸入具備內(nèi)部故障保護(hù)功能。故障保護(hù)電路會在輸入未驅(qū)動或共模電壓超出規(guī)定范圍時,強(qiáng)制將差分輸入設(shè)置為低電平狀態(tài)。MAX9392 為 LVDS、HSTL 及其他高速差分輸入提供高電平輸入故障保護(hù)。MAX9393 為 LVPECL、CML 及其他低壓差分輸入提供低電平輸入故障保護(hù)。

選擇功能

SEL 邏輯輸入控制每個通道的輸入和輸出信號連接。SEL0 和 SEL1 可將器件配置為差分交叉點開關(guān)、2:1 多路復(fù)用器或 1:2 分配器(見圖 7 )。有關(guān)模式選擇設(shè)置,請參見表 1(插入 A 或 B 代表相應(yīng)表格 )。A 通道和 B 通道的輸入具有獨立的選擇輸入,可為每個通道實現(xiàn)不同的配置。

使能功能

EN 邏輯輸入用于啟用或禁用每組差分輸出。將 EN_0 連接到 VCC 可啟用 OUT_0/OUT_0 差分輸出對;將 EN_0 連接到地可禁用該差分輸出對。禁用時,差分輸出對會呈現(xiàn)差分故障低狀態(tài)。

-

信號

+關(guān)注

關(guān)注

12文章

2914瀏覽量

80124 -

lvds

+關(guān)注

關(guān)注

2文章

1237瀏覽量

69829 -

交叉點開關(guān)

+關(guān)注

關(guān)注

1文章

16瀏覽量

6182

發(fā)布評論請先 登錄

美國國家半導(dǎo)體兩款低功率LVDS 2x2交叉點開關(guān)電路

雙路2x2交叉點開關(guān)MAX3840相關(guān)資料下載

Maxim推出雙向、4選2、USB 2.0交叉點開關(guān)MAX4

MAX14885E 低電容VGA 2:2雙通道圖形交叉點開關(guān)

2x2 LVDS交叉點開關(guān)SN65LVCP22數(shù)據(jù)表

DS25CP152 3.125Gbps LVDS 2x2交叉點開關(guān)數(shù)據(jù)表

DS90CP22 800 Mbps 2x2 LVDS交叉點開關(guān)數(shù)據(jù)表

DS90CP02 1.5 Gbps 2x2 LVDS交叉點開關(guān)數(shù)據(jù)表

DS10CP152 1.5Gbps 2X2 LVDS交叉點開關(guān)數(shù)據(jù)表

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關(guān)技術(shù)手冊

MAX9392任意邏輯至LVDS、雙路、2 x 2交叉點開關(guān)技術(shù)手冊

MAX9392任意邏輯至LVDS、雙路、2 x 2交叉點開關(guān)技術(shù)手冊

評論