概述

MAX9174/MAX9175是670MHz低抖動、低扭曲的1:2分配器,尤其適合于保護切換、環回、時鐘和數據分配。這些器件具有1.0ps~(RMS)~ (最大)的超低隨機抖動,保證在那些定時誤差極為敏感的高速鏈路中可靠工作。

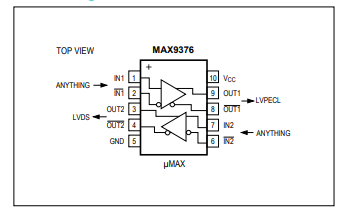

MAX9714具有安全失效的LVDS輸入和LVDS輸出。MAX9175接收任何差分輸入(CML/LVDS/LVPECL),提供LVDS輸出。控制掉電輸入,可以將輸出置為高阻。當輸入處于開路、無驅動短路或無驅動終端匹配時,MAX9174的安全失效電路驅動輸出為高電平。MAX9175具有偏置電路,在輸入開路時驅動高電平輸出。掉電輸入兼容于標準的LVTTL/LVCMOS邏輯,并且掉電輸入可以承受-1V的下沖和VCC + 1V的過沖。MAX9174/MAX9175提供10引腳μMAX和10引腳、底盤裸露的薄型QFN封裝,工作于+3.3V單電源,工作溫度范圍-40°C至+85°C。

數據表:*附件:MAX9174 MAX9175 670MHz、LVDS至LVDS和任意邏輯至LVDS 1比2分配器.pdf

應用

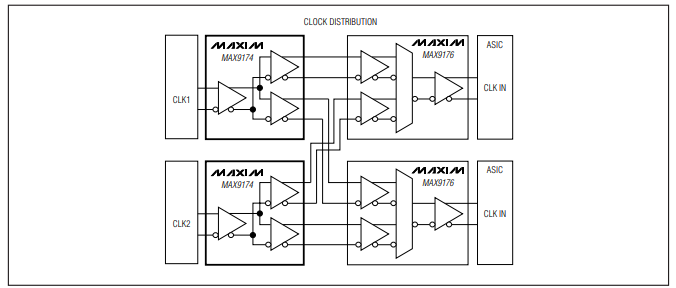

- 時鐘分配

- 環回

- 保護開關

特性

- 670MHz時,最大1.0ps

(RMS)抖動 - 800Mbps數據速率時,最大80ps

(P-P)抖動 - +3.3V工作電源

- LVDS安全失效輸入(MAX9174)

- 任意輸入電平(MAX9175)包括差分CML/LVDS/LVPECL

- 斷電時,輸入能夠承受-1.0V至V

CC+ 1.0V的電壓 - 低功耗CMOS設計

- 10引腳μMAX和薄型QFN封裝

- -40°C至+85°C的工作溫度范圍

- 符合ANSI TIA/EIA-644 LVDS標準

- IEC 61000-4-2第4級ESD保護

應用電路

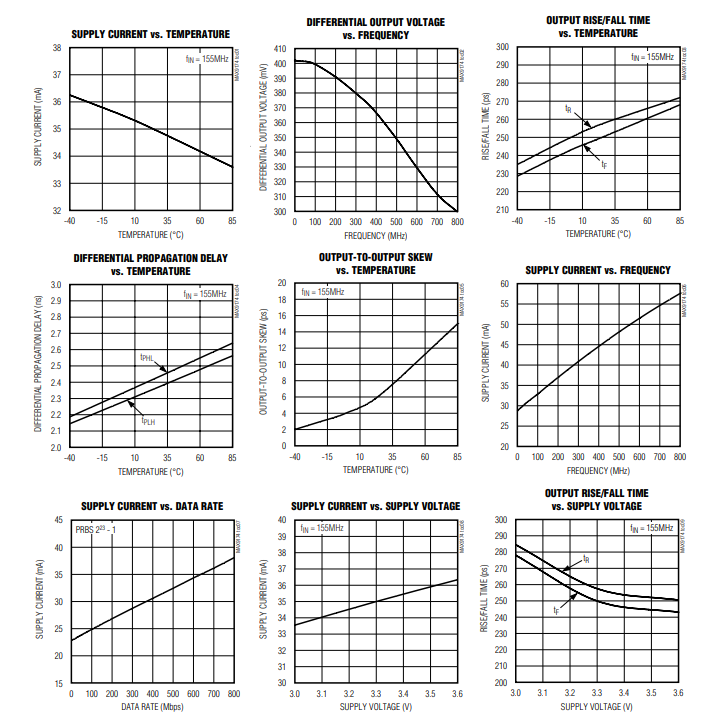

典型操作特性

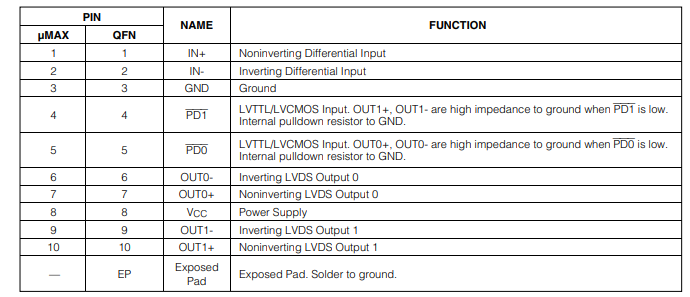

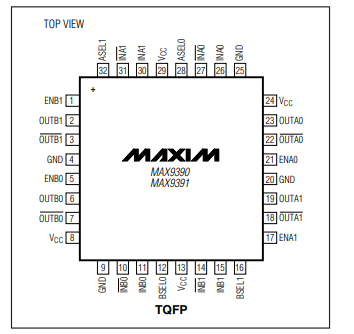

引腳配置描述

應用信息

電源去耦

繞過 Vcc 引腳,通過在盡可能靠近器件的位置并聯安裝 0.1μF 和 0.001μF 的高頻表面貼裝陶瓷電容器,將較小值的電容器連接到 Vcc。

差分走線

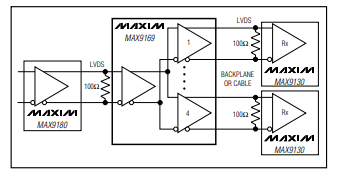

輸入和輸出走線會影響 MAX9174/MAX9175 的性能。使用受控阻抗差分走線(100Ω 類型)。為減少輻射噪聲并確保信號耦合對稱,將差分輸入和輸出信號布置在同一層中。通過匹配兩條信號線的電氣長度來減少偏移,過度的偏移會導致磁場抵消的降低。在差分走線之間保持恒定距離,以避免差分阻抗的不連續性。盡量減少過孔的數量,以進一步防止阻抗不連續性。

電纜和連接器

LVDS(低壓差分信號)互連通常具有 100Ω 的受控差分阻抗。使用具有匹配差分阻抗的電纜和連接器,以最大限度地減少阻抗不連續性。避免使用非平衡電纜,如帶狀電纜或簡單的同軸電纜。平衡電纜,如雙絞線,信號質量更好,并且往往產生較少的電磁干擾,因為它們的磁場相互抵消。平衡電纜拾取噪聲作為共模信號,會被 LVDS 接收器拒絕。

端接

MAX9174/MAX9175 需要外部輸入和輸出端接電阻,用于 LVDS,在每個差分對中連接一個

-

時鐘

+關注

關注

11文章

1971瀏覽量

135000 -

lvds

+關注

關注

2文章

1237瀏覽量

69844 -

分配器

+關注

關注

0文章

213瀏覽量

27321

發布評論請先 登錄

MAX9234,MAX9236,MAX9238熱插拔、21位、直流平衡、LVDS解串器

MAX9376,pdf datasheet (LVDS/An

DS90LV110AT 1至10 LVDS數據/時鐘分配器數據表

DS90LV110T 1至10 LVDS數據/時鐘分配器數據表

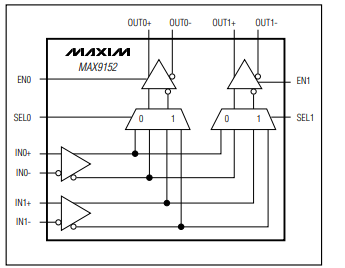

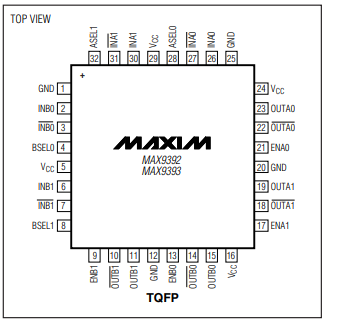

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關技術手冊

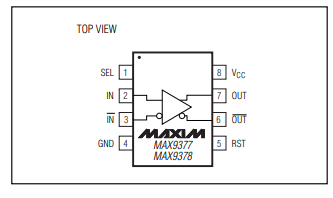

MAX9377/MAX9378任意邏輯至LVPECL/LVDS轉換器,引腳可設置四分頻電路技術手冊

MAX9374/MAX9374A差分LVPECL至LVDS變換器技術手冊

MAX9174/MAX9175 670MHz、LVDS至LVDS和任意邏輯至LVDS 1:2分配器中文手冊

MAX9174/MAX9175 670MHz、LVDS至LVDS和任意邏輯至LVDS 1:2分配器中文手冊

評論