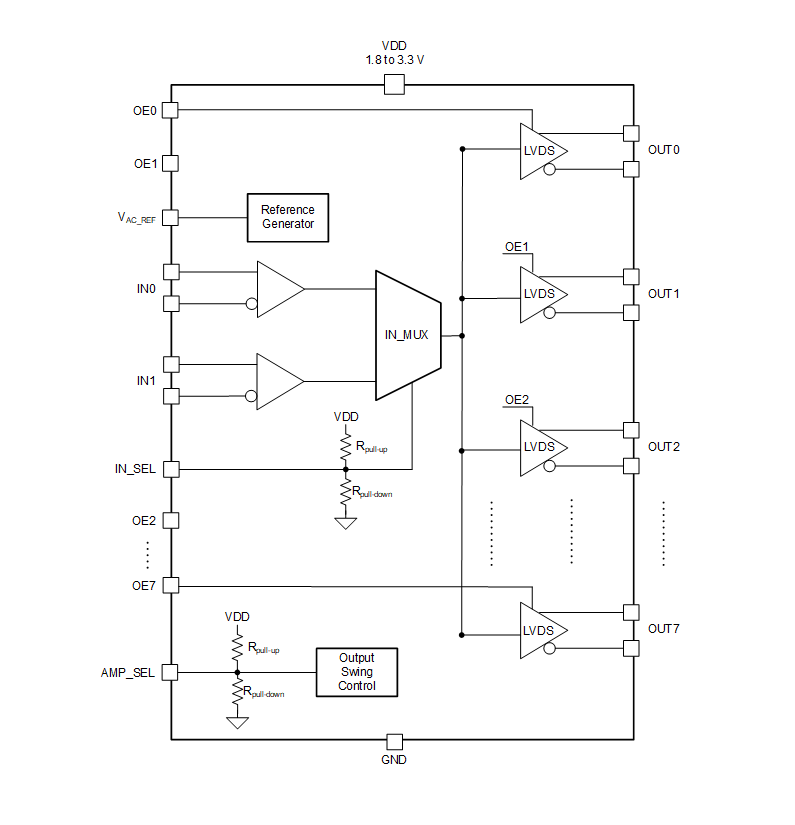

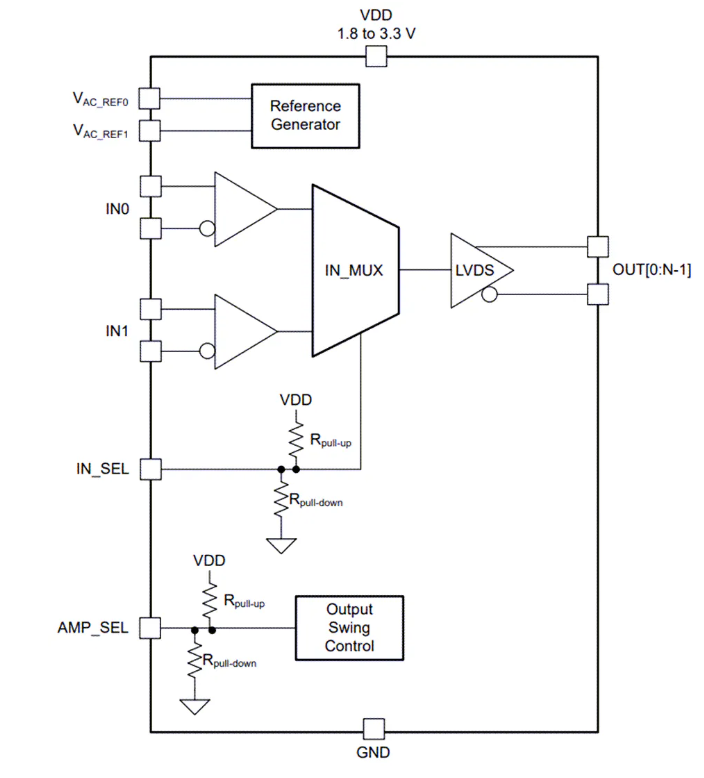

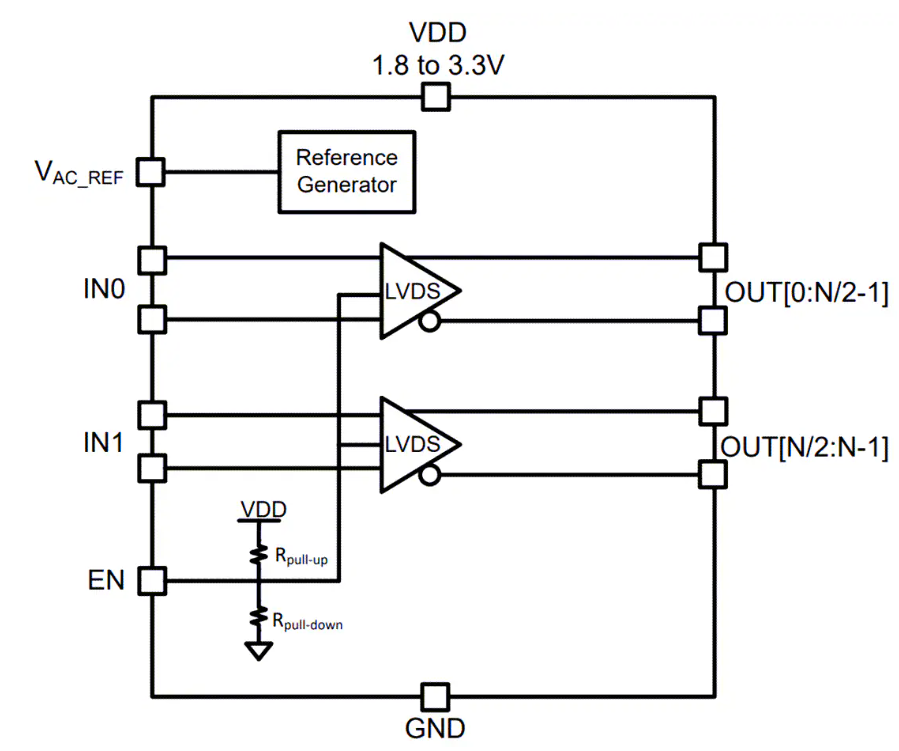

LMK1D1212時(shí)鐘緩沖器以最小偏斜將兩個(gè)可選時(shí)鐘輸入(IN0、IN1)中的一個(gè)分配到12對(duì)差分LVDS時(shí)鐘輸出(OUT0至OUT11)。同樣,LMK1D1216分配16對(duì)差分LVDS時(shí)鐘輸出(OUT0至OUT15)。LMK1D121x 系列可以接受兩個(gè)時(shí)鐘源進(jìn)入輸入多路復(fù)用器。輸入可以是LVDS、LVPECL、LP-HCSL、HCSL、CML或LVCMOS。

LMK1D121x 專為驅(qū)動(dòng) 50 Ω?jìng)鬏斁€而設(shè)計(jì)。在單端模式下驅(qū)動(dòng)輸入時(shí),向未使用的負(fù)輸入引腳施加適當(dāng)?shù)钠秒妷骸?br />*附件:lmk1d1216.pdf

IN_SEL引腳選擇路由到輸出的輸入。如果此引腳保持打開(kāi)狀態(tài),則會(huì)禁用輸出(靜態(tài)低電平)。該部件支持故障安全功能。該器件還集成了輸入遲滯,可防止在沒(méi)有輸入信號(hào)的情況下輸出隨機(jī)振蕩。

該器件在 1.8V 或 2.5V 或 3.3V 電源環(huán)境中工作,特性范圍為 –40°C 至 105°C(環(huán)境溫度)。

特性

- 高性能LVDS時(shí)鐘緩沖器系列:高達(dá)2 GHz

- 2:12 差分緩沖器 (LMK1D1212)

- 2:16差分緩沖器(LMK1D1216)

- 電源電壓:1.71 V 至 3.465 V

- 低附加抖動(dòng):在156.25 MHz時(shí),12kHz至20MHz時(shí)最大值<60 fs RMS

- 極低的本底相位噪聲:-164 dBc/Hz(典型值)

- 極低的傳播延遲:最大< 575 ps

- 輸出偏斜:最大20 ps

- 高擺幅LVDS(升壓模式):AMP_SEL = 1時(shí)典型值為500 mV VOD

- 通用輸入接受 LVDS、LVPECL、LVCMOS、HCSL 和 CML 信號(hào)電平

- LVDS基準(zhǔn)電壓,V AC_REF,可用于電容耦合輸入

- 工業(yè)溫度范圍:–40°C 至 105°C

- 包裝在

- LMK1D1212:6 毫米× 6 毫米、40 引腳 VQFN (RHA)

- LMK1D1216:7 毫米× 7 毫米、48 引腳 VQFN (RGZ)

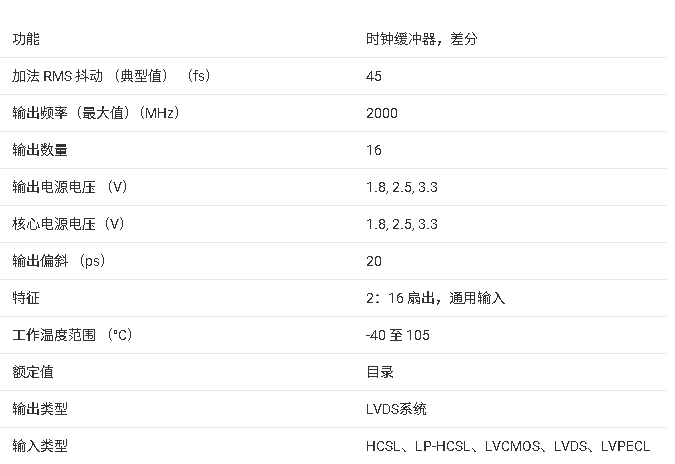

參數(shù)

方框圖

?1. 產(chǎn)品概述?

LMK1D121x是德州儀器(TI)推出的高性能LVDS時(shí)鐘緩沖器系列,包含LMK1D1212(2:12差分緩沖器)和LMK1D1216(2:16差分緩沖器)。核心特性包括:

- ?工作頻率?:支持高達(dá)2 GHz的時(shí)鐘信號(hào)

- ?低附加抖動(dòng)?:<60 fs RMS(12 kHz至20 MHz帶寬,156.25 MHz時(shí))

- ?寬電壓范圍?:1.71 V至3.465 V供電

- ?低傳播延遲?:<575 ps

- ?工業(yè)級(jí)溫度范圍?:-40°C至105°C

?2. 關(guān)鍵特性?

- ?輸入兼容性?:支持LVDS、LVPECL、LVCMOS、HCSL、CML等多種信號(hào)電平

- ?輸出配置?:

- LMK1D1212:12對(duì)差分LVDS輸出(OUT0-OUT11)

- LMK1D1216:16對(duì)差分LVDS輸出(OUT0-OUT15)

- ?輸出擺幅控制?:通過(guò)AMP_SEL引腳選擇標(biāo)準(zhǔn)(350 mV)或增強(qiáng)(500 mV)LVDS輸出幅度

- ?封裝選項(xiàng)?:

- LMK1D1212:6 mm × 6 mm 40引腳VQFN(RHA)

- LMK1D1216:7 mm × 7 mm 48引腳VQFN(RGZ)

?3. 應(yīng)用領(lǐng)域?

- 電信與網(wǎng)絡(luò)設(shè)備

- 醫(yī)療成像系統(tǒng)

- 測(cè)試測(cè)量儀器

- 無(wú)線基礎(chǔ)設(shè)施

- 專業(yè)音視頻及數(shù)字標(biāo)牌

?4. 功能描述?

- ?輸入選擇?:通過(guò)IN_SEL引腳選擇兩路輸入(IN0或IN1),支持失效保護(hù)功能(輸入懸空時(shí)輸出靜態(tài)低電平)。

- ?輸出控制?:未使用的輸出建議以100 Ω電阻差分端接以優(yōu)化性能。

- ?熱管理?:裸露焊盤(DAP)需連接至PCB地平面以增強(qiáng)散熱。

?5. 性能參數(shù)?

- ?電源電流?:

- 靜態(tài)電流(LMK1D1212):65 mA(典型值)

- 100 MHz工作時(shí)(LMK1D1216):120-150 mA

- ?相位噪聲?:-164 dBc/Hz(典型值,156.25 MHz時(shí))

- ?輸出偏斜?:≤20 ps(同器件內(nèi)輸出間)

?6. 設(shè)計(jì)建議?

- ?電源去耦?:每個(gè)電源引腳需就近放置0.1 μF高頻旁路電容,推薦使用鐵氧體磁珠隔離板級(jí)電源噪聲。

- ?布局指南?:縮短高速信號(hào)走線長(zhǎng)度,保持差分對(duì)對(duì)稱性,熱焊盤需充分焊接至PCB地平面。

?7. 文檔支持?

包含完整引腳定義、電氣特性表、典型應(yīng)用電路及封裝機(jī)械圖紙(如SCALE 2.200的VQFN封裝尺寸圖)。

-

時(shí)鐘緩沖器

+關(guān)注

關(guān)注

2文章

270瀏覽量

51910 -

lvds

+關(guān)注

關(guān)注

2文章

1237瀏覽量

69823 -

偏置電壓

+關(guān)注

關(guān)注

0文章

172瀏覽量

14147 -

LVCMOS

+關(guān)注

關(guān)注

1文章

142瀏覽量

11994

發(fā)布評(píng)論請(qǐng)先 登錄

LMK1D210x低附加抖動(dòng)LVDS緩沖器數(shù)據(jù)表

LMK1D120x低附加抖動(dòng)LVDS緩沖器數(shù)據(jù)表

LMK1D121x低附加抖動(dòng)LVDS緩沖器數(shù)據(jù)表

LMK1D210x低附加抖動(dòng)LVDS緩沖器數(shù)據(jù)表

LMK1D121x低附加抖動(dòng)LVDS時(shí)鐘緩沖器技術(shù)解析與應(yīng)用指南

低附加抖動(dòng)LVDS緩沖器LMK1D210x技術(shù)解析與應(yīng)用指南

?LMK1D121x系列低附加抖動(dòng)LVDS緩沖器技術(shù)文檔總結(jié)

?LMK1D121x系列低附加抖動(dòng)LVDS緩沖器技術(shù)文檔總結(jié)

評(píng)論