1.LVPECL與LVDS的互連

1.1 LVPECL與LVDS的直流耦合

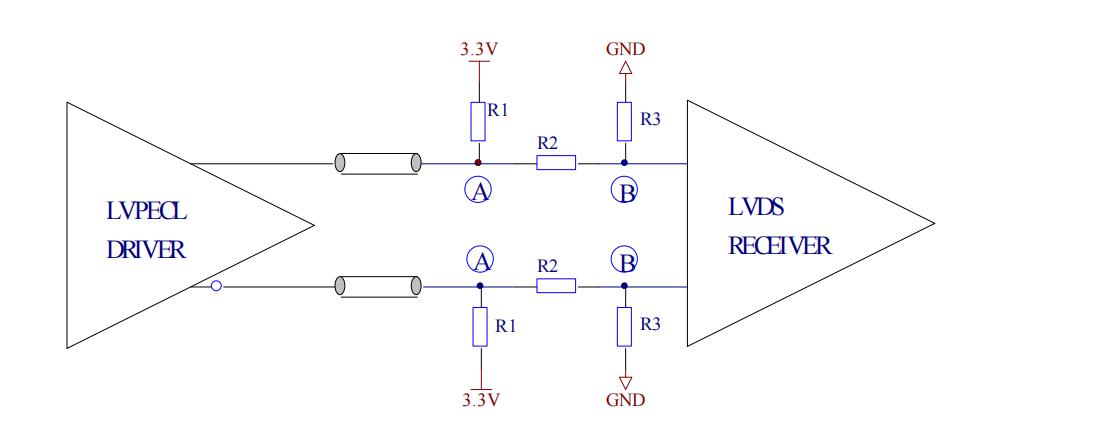

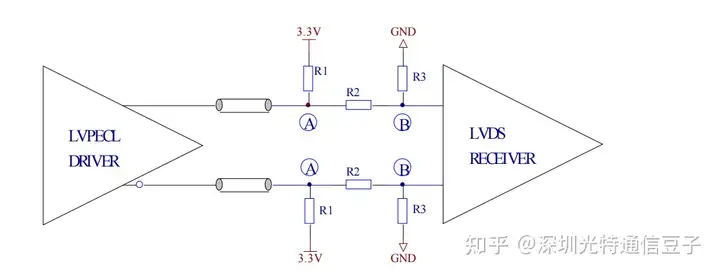

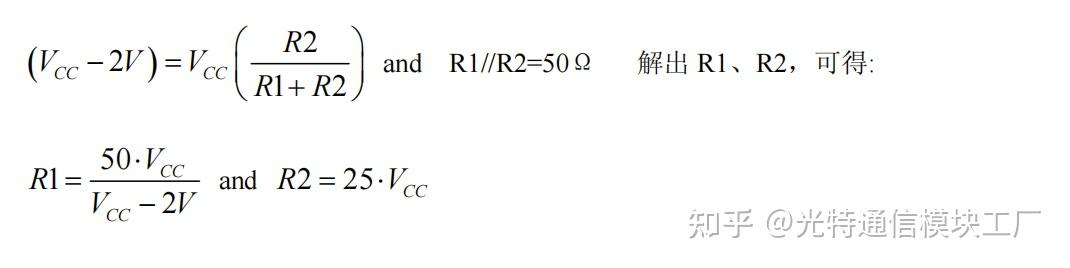

LVPECL到LVDS的直流耦合結(jié)構(gòu)需要一個電阻網(wǎng)絡(luò),如圖5中所示,設(shè)計該網(wǎng)絡(luò)時有這樣幾點必須考慮:首先,我們知道當(dāng)負載是50Ω接到VCC-2V時,LVPECL的輸出性能是最優(yōu)的,因此我們考慮該電阻網(wǎng)絡(luò)應(yīng)該與最優(yōu)負載等效;然后我們還要考慮該電阻網(wǎng)絡(luò)引入的衰減不應(yīng)太大,LVPECL輸出信號經(jīng)衰減后仍能落在LVDS的有效輸入范圍內(nèi)。注意LVDS的輸入差分阻抗為100Ω,或者每個單端到虛擬地為50Ω(圖1所示),該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等。LVPECL到LVDS的直流耦合所需的電阻網(wǎng)絡(luò)需滿足下面方程組:

圖1LVPECL到LVDS的直流耦合

考慮VCC=+3.3V 情況,解上面的方程組得到:R1=182Ω,R2=47.5Ω,R3=47.5Ω,VA=1.13V,

RAC=51.5Ω,RDC=62.4Ω,增益= 0.337。通過該終端網(wǎng)絡(luò)連接LVPECL輸出與LVDS輸入時,實測得VA=2.1V,VB=1.06V。假定LVPECL差分最小輸出電壓為930mV,在LVDS的輸入端可達到313mV,能夠滿足LVDS輸入靈敏度要求。考慮信號較大時,如果LVPECL的最大輸出為1.9V,LVDS的最大輸入電壓則為640mV,同樣可以滿足LVDS輸入指標(biāo)要求。

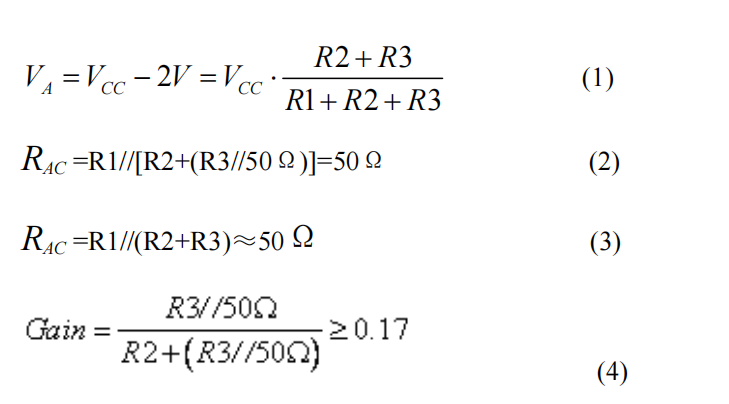

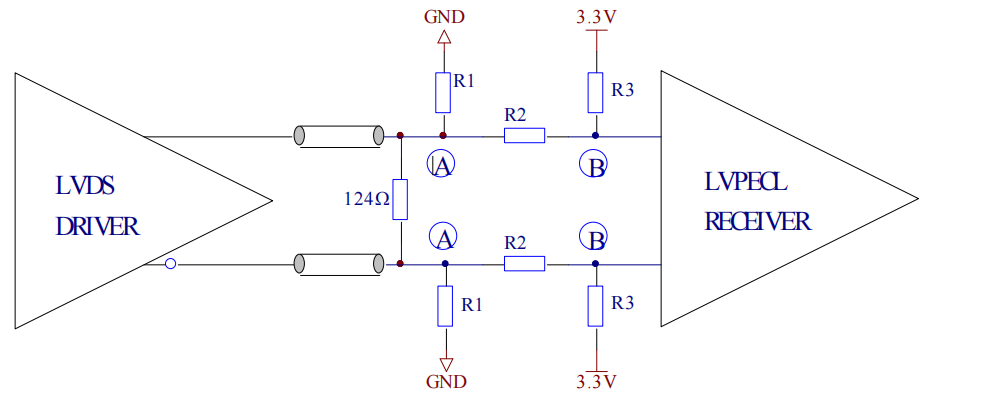

LVDS與LVPECL之間采用直流耦合結(jié)構(gòu)時,需要加一個電阻網(wǎng)絡(luò),如圖2所示。該電阻網(wǎng)絡(luò)完成LVDS

輸出電平(1.2V)到LVPECL輸入電平(VCC-1.3V)的轉(zhuǎn)換。由于LVDS的輸出是以地為參考,而LVPECL的輸

入是以VCC為參考,這需要在構(gòu)建電平轉(zhuǎn)換網(wǎng)絡(luò)時注意LVDS的輸出不會對供電電源的變化敏感;另一個

問題是需要在功耗和速度方面折中考慮,如果電阻值(R1、R2、R3)取得較小,由電阻網(wǎng)絡(luò)和LVPECL輸入寄

生電容構(gòu)成的時間常數(shù)較小,允許電路在更高的速度下工作。但是,由于這些電阻上流過較大的電流,使得

總功耗增大。這時,LVDS的輸出性能容易受電源波動的影響。還有一個問題就是要考慮阻抗匹配和網(wǎng)絡(luò)衰

減問題,電阻值可以通過下面的方程導(dǎo)出。

圖2LVDS到LVPECL的直流耦合

在VCC電壓為+3.3V時,解上面的方程得:R1 =374Ω,R2 =249Ω,R3 =402Ω,VA=1.2V,VB = 2.0V,

RIN=49Ω,增益=0.62。LVDS的最小差分輸出信號擺幅為500mVP-P,在上面結(jié)構(gòu)中加到LVPECL輸入端

的信號擺幅變?yōu)?10mVP-P,該幅度低于LVPECL的輸入標(biāo)準(zhǔn),在實際應(yīng)用中,讀者可根據(jù)器件的實際性能做

出自己的判斷。

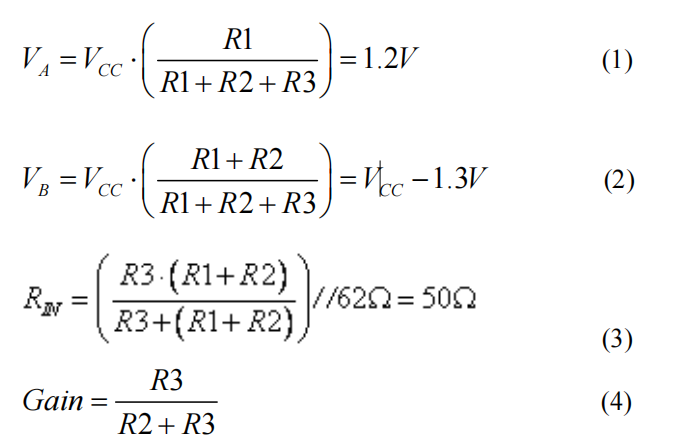

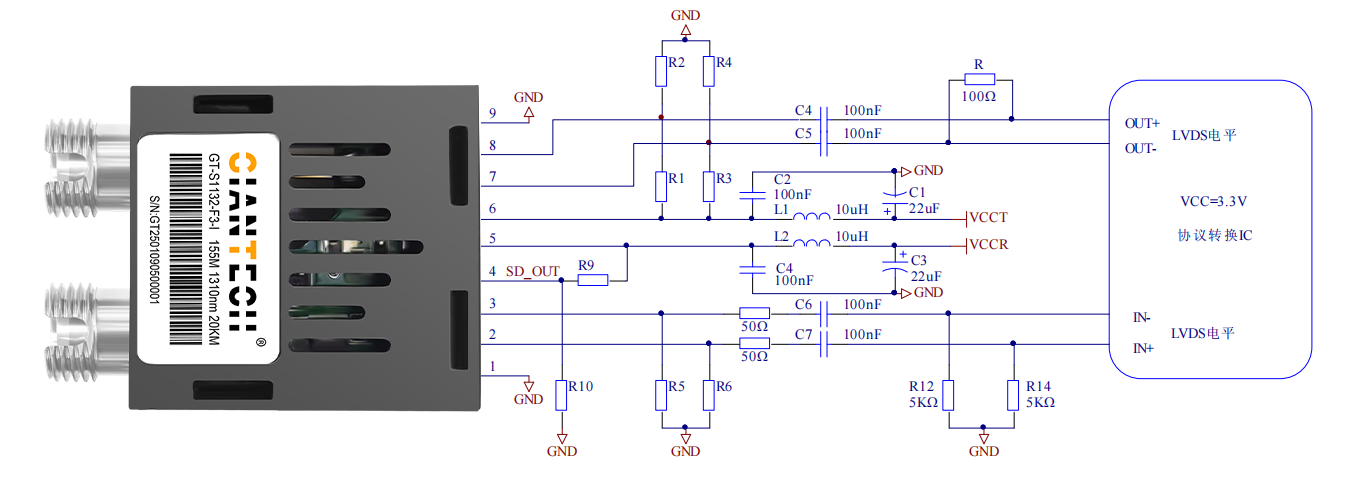

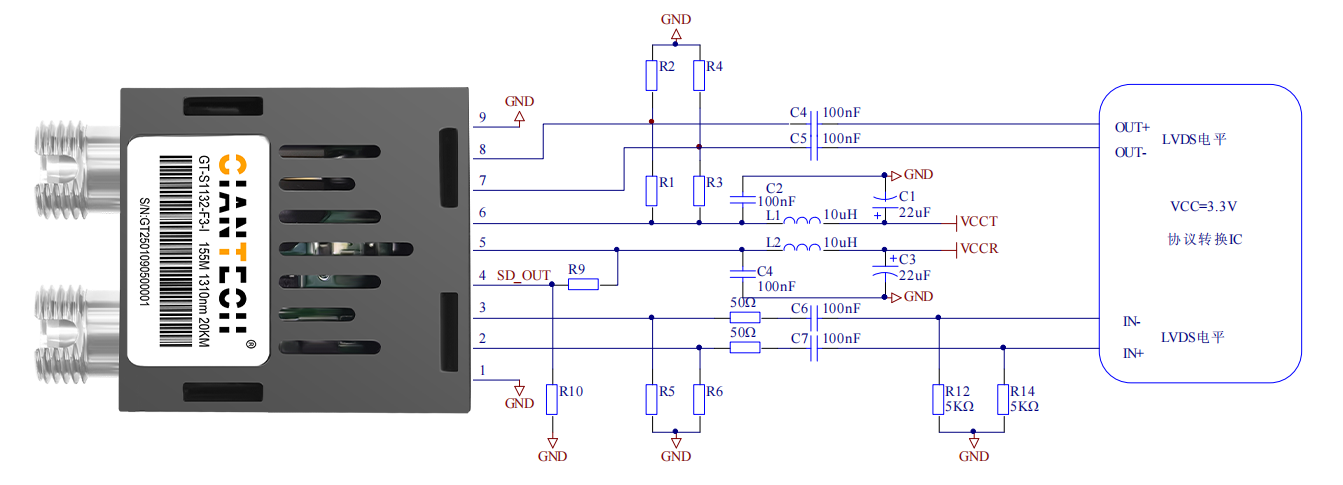

圖3 光模塊與協(xié)議轉(zhuǎn)換IC間LVPECL/LVDS電平的直流耦合

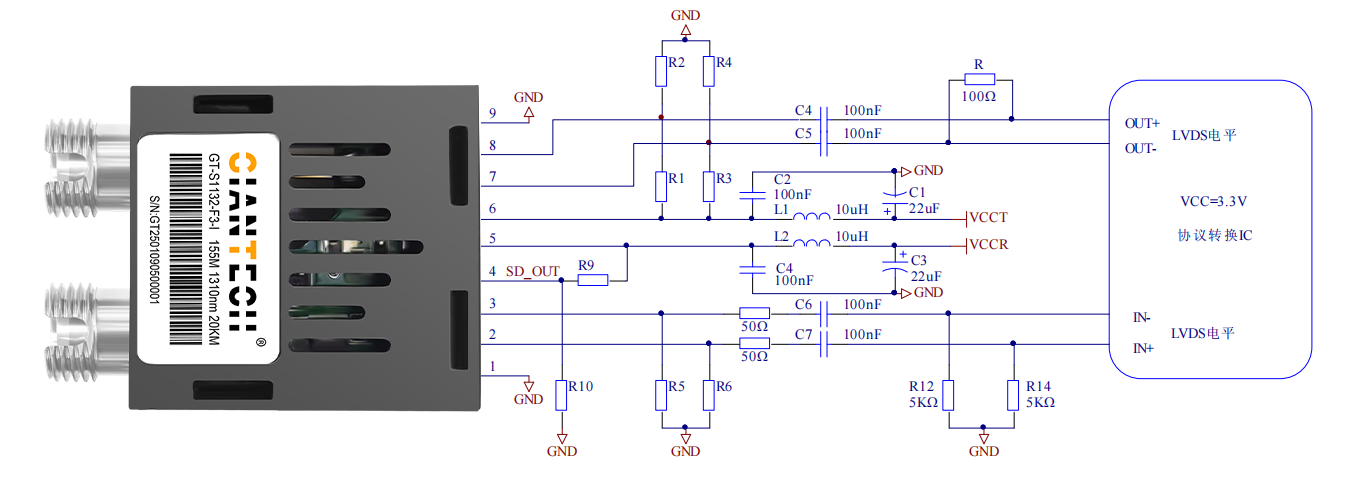

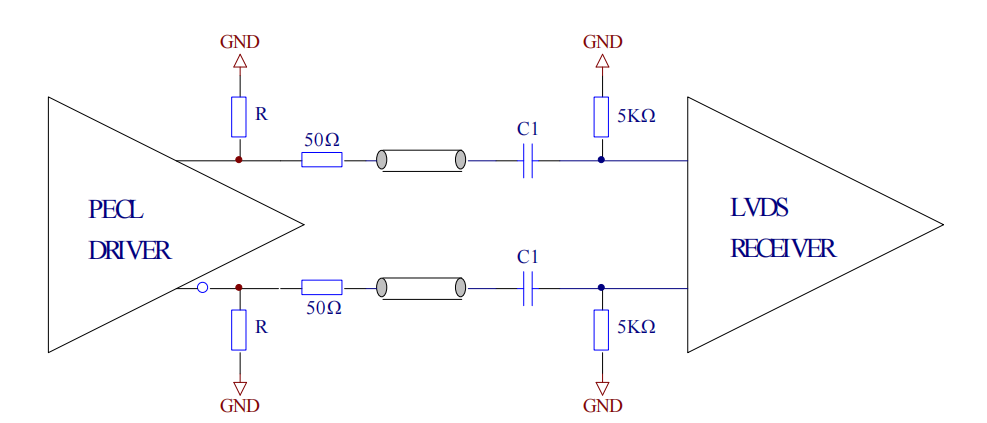

1.2 LVPECL與LVDS的交流耦合

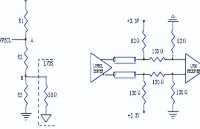

LVPECL到LVDS的交流耦合結(jié)構(gòu)如圖4所示,LVPECL的輸出端到地需加直流偏置電阻R(142Q~200Q),同時信號通道上一定要串接50Ω電阻,以提供一定衰減。LVDS的輸入端到地需加5.0kQ電阻,以提供共模偏置。

圖4.LVPECL與LVDS之間的交流耦合

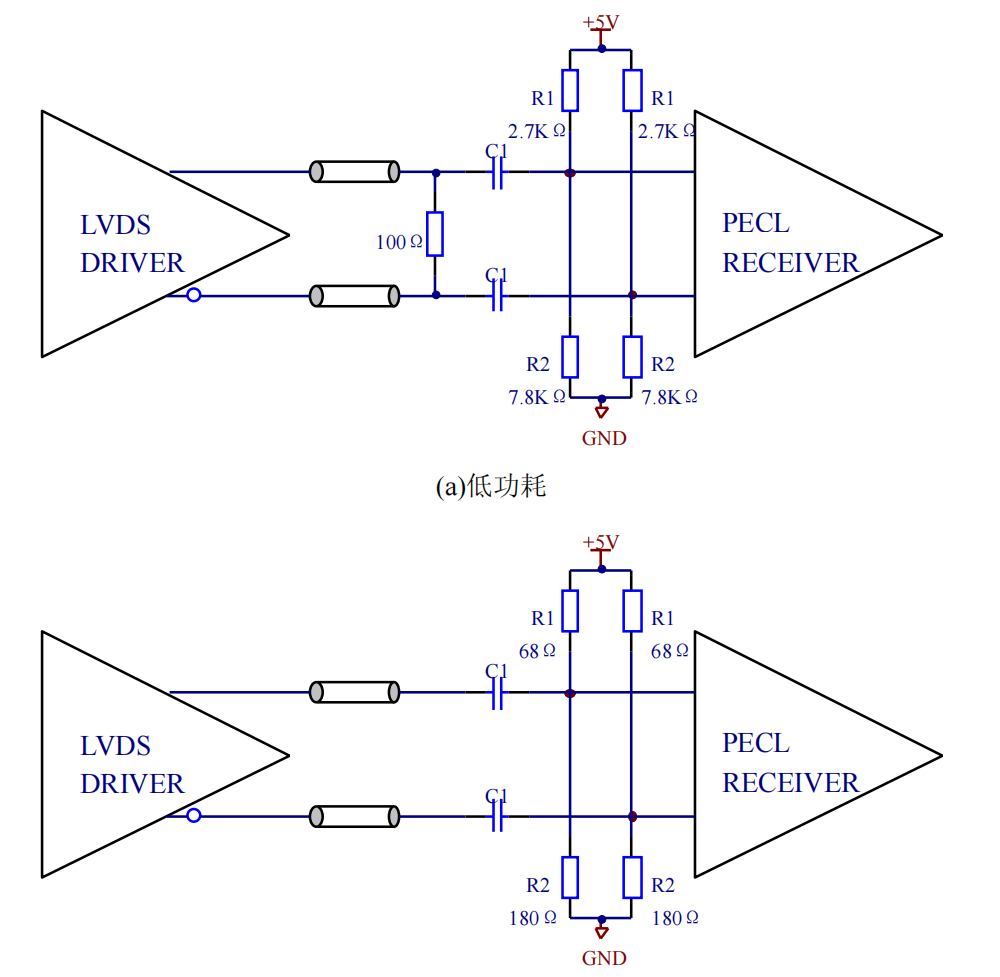

LVDS到LVPECL的交流耦合結(jié)構(gòu)較為簡單,如圖5所示,如果芯片內(nèi)部加了偏置,則可去掉R1和R2。

圖5.LVDS與LVPECL之間的交流耦合

2.PECL與LVDS的互連

PECL到LVDS的交流耦合結(jié)構(gòu)如圖6所示,PECL的輸出端到地需加直流偏置電阻R(270Ω~350Ω),

同時信號通道上一定要串接50Ω電阻,以提供一定衰減。LVDS的輸入端到地需加5.0kΩ電阻,以提供共模

偏置。

圖6.PECL與LVDS之間的交流耦合

LVDS到PECL 的交流耦合結(jié)構(gòu)較為簡單,如圖7 所示,如果芯片內(nèi)部加了偏置,則可去掉R1和R2。

(b)普通接法

圖7.LVDS與PECL 之間的交流耦合

| 參數(shù) | Rl=R3 | R2=R4 | R5=R6 | 備注 |

| VCC=+3.3V | 2.7K Ω | 4.7K Ω | 140Ω~200Ω |

接上電阻 R=100Ω為 低功耗電路 |

| VCC=+5V | 2.7K Ω | 7.8K Ω | 270Ω~350Ω |

(a)低功耗匹配電路

(b)普通匹配電路

圖8.光模塊與協(xié)議轉(zhuǎn)換IC間PECL/LVPECL/LVDS電平的交流耦合

光特通信專注于光模塊研發(fā)生產(chǎn),支持OEM/ODM定制,集研發(fā)、銷售與制造為一體的生產(chǎn)企業(yè)!

參考資料:

Interfacing Between LVPECL, CML, and LVDS Levels---Texas Instruments

審核編輯 黃宇

-

耦合

+關(guān)注

關(guān)注

13文章

605瀏覽量

102591 -

lvds

+關(guān)注

關(guān)注

2文章

1217瀏覽量

69202

發(fā)布評論請先 登錄

LVPECL 與 LVDS 及 PECL 與 LVDS 的互連技術(shù)解析

PECL接口終端匹配技術(shù)詳解:直流與交流耦合設(shè)計指南

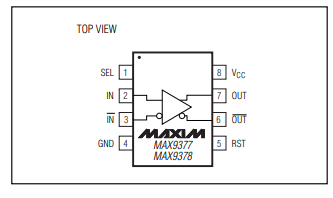

MAX9374/MAX9374A差分LVPECL至LVDS變換器技術(shù)手冊

MAX9377/MAX9378任意邏輯至LVPECL/LVDS轉(zhuǎn)換器,引腳可設(shè)置四分頻電路技術(shù)手冊

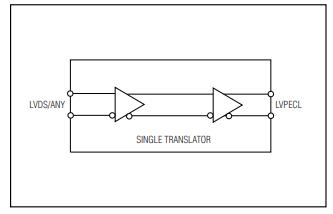

MAX9375單LVDS/任意邏輯至LVPECL轉(zhuǎn)換器技術(shù)手冊

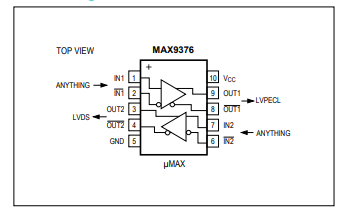

MAX9376 LVDS/任意邏輯至LVPECL/LVDS、雙路電平轉(zhuǎn)換器技術(shù)手冊

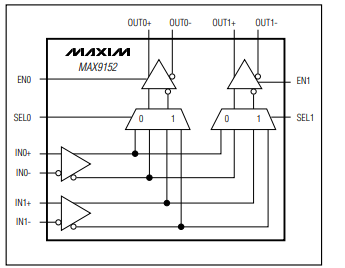

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關(guān)技術(shù)手冊

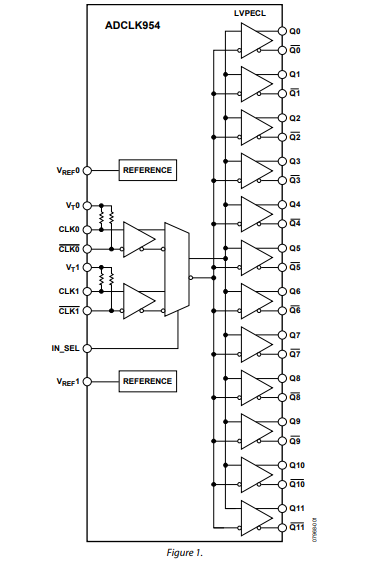

ADCLK954采用SiGe工藝,具有2個可選輸入、12個LVPECL輸出的時鐘扇出緩沖器技術(shù)手冊

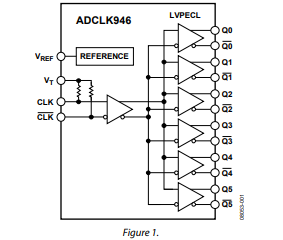

ADCLK946采用SiGe工藝的6 LVPECL輸出時鐘扇出緩沖器技術(shù)手冊

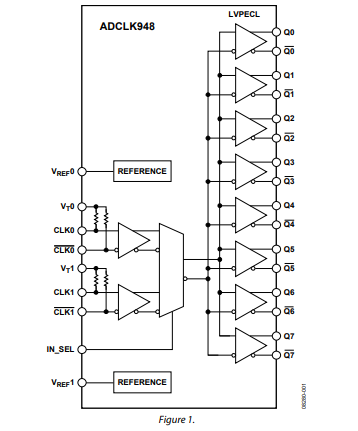

ADCLK948 2路可選輸入、8路LVPECL輸出、SiGe時鐘扇出緩沖器技術(shù)手冊

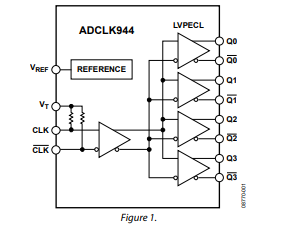

ADCLK944 2.5 V/3.3 V、4路LVPECL輸出、SiGe時鐘扇出緩沖器技術(shù)手冊

差分晶振-LVPECL到LVDS的連接

tlk10022的時鐘輸入是否可以用3.3V的lvpecml電平交流耦合進去?

為什么DATACLK用的是LVDS電平標(biāo)準(zhǔn)的接口呢?

AN-1177: LVDS和M-LVDS電路實施指南

LVPECL與LVDS電平互連:直流與交流耦合設(shè)計指南

LVPECL與LVDS電平互連:直流與交流耦合設(shè)計指南

評論