概述

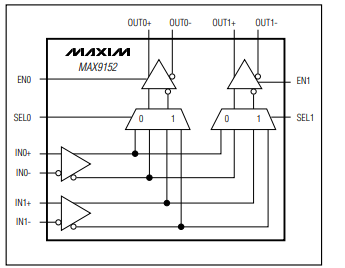

MAX9152 2 x 2交叉點開關專為需要高速、低功耗和低噪聲信號分配的應用而設計。該器件包括兩路LVDS/LVPECL輸入、兩路LVDS輸出和兩路用于設置差分輸入和輸出之間內部連接的邏輯輸入。

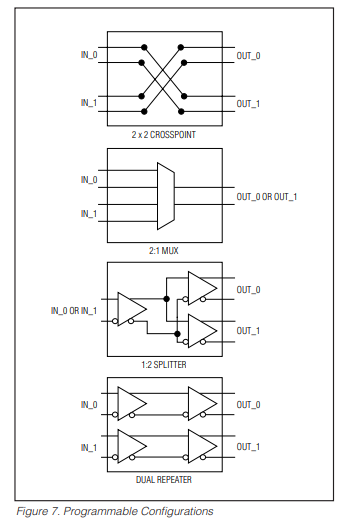

MAX9152可編程為將任何輸入連接至任一輸出或兩路輸出,使其可采用以下配置:2 5 2交叉點開關、2:1多路復用器、1:2解復用器、1:2分路或雙中繼器。這種靈活性使MAX9152非常適用于容錯系統中的保護開關、診斷用的環回開關、用于時鐘/數據分配的扇出緩沖以及用于遠距離通信的信號再生。

數據表:*附件:MAX9152 800Mbps、LVDS LVPECL至LVDS、2 x 2交叉點開關技術手冊.pdf

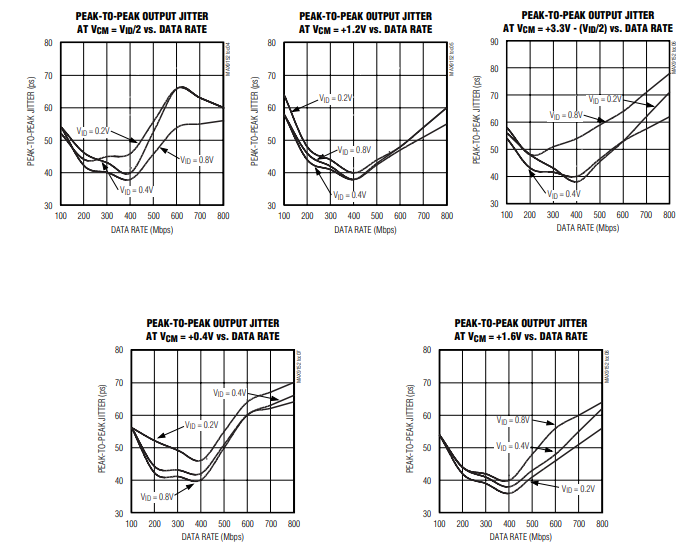

120psPK-PK(最大值)超低PRBS抖動可確保在對時序誤差高度敏感的高速鏈路中實現可靠通信,尤其是那些包含時鐘和數據恢復或串行器和解串器的鏈路。高速開關性能支持800Mbps的數據速率和小于50ps(最大值)的通道間偏斜。

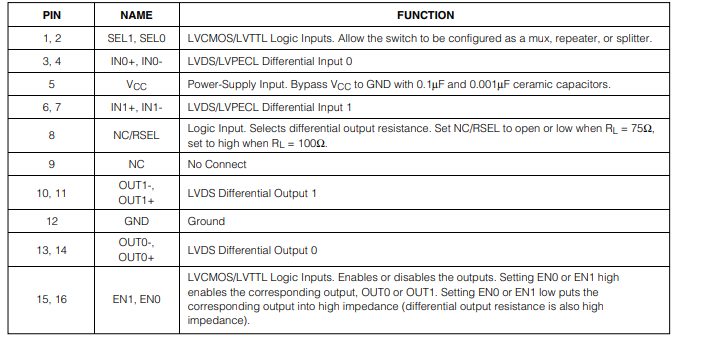

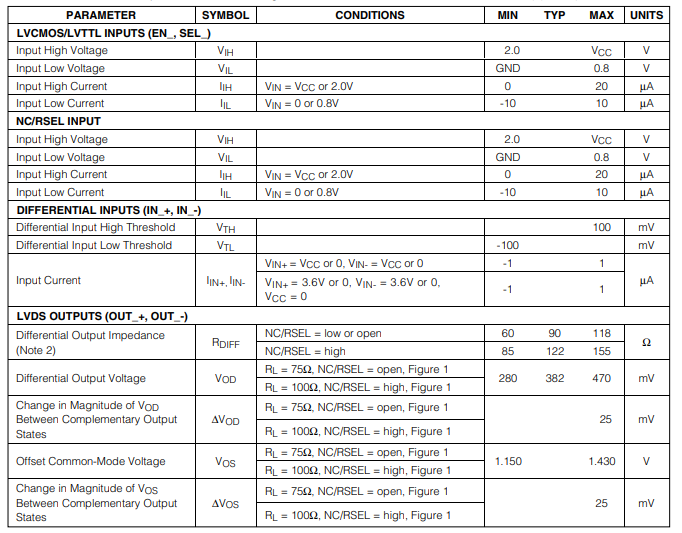

LVDS輸入和輸出符合TIA/EIA-644 LVDS標準。LVDS輸入也可直接接受LVPECL信號,以及通過衰減網絡接受PECL信號。LVDS輸出可驅動75Ω或100Ω負載,并具有可選擇的差分輸出電阻以盡可能地減少反射。

MAX9152采用16引腳TSSOP和SO封裝,在-40°C至+85°C溫度范圍內采用+3.3V單電源供電時功耗僅為109mW。

特性

- 引腳可編程配置

- 2 x 2交叉點開關

- 2:1多路復用

- 1:2解復用器

- 1:2分路器

- 雙中繼器

- 120ps

PK-PK(最大值)超低抖動,800Mbps,PRBS = 2^23^ -1 數據模式 - 低通道間偏斜:50ps(最大值)

- 109mW功耗

- 符合ANSI TIA/EIA-644 LVDS標準

- 輸入接受LVDS/LVPECL信號

- LVDS輸出額定用于75Ω和100Ω負載

- 引腳可編程差分輸出電阻

- DS90CP22的引腳兼容升級版(SO封裝)

- 采用16引腳TSSOP封裝(SO尺寸的一半)

框圖

典型操作特性

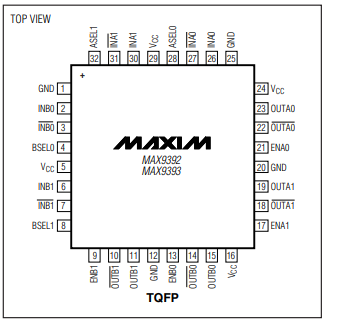

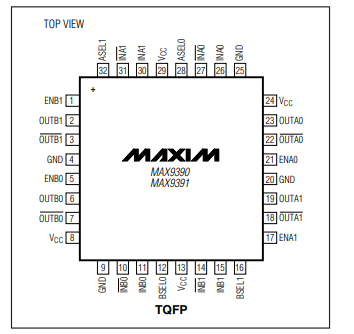

引腳配置描述

詳細說明

LVDS接口標準是一種信令方法,旨在通過受控阻抗介質進行點對點通信,符合ANSI TIA/EIA - 644和IEEE 1596.3標準。LVDS使用比其他常見通信標準更低的電壓擺幅,在降低功耗的同時實現高速數據速率,并減少電磁干擾(EMI),提高系統抗擾度。

MAX9152是一款800Mbps的2×2交叉點開關,專為高速、低功耗的點對點和多點接口而設計。該器件可接受LVDS和差分LVPECL信號,并根據所選模式將其路由至輸出端。

幅度在0.1V至VCC之間、單端電壓在MAX9152的VCC和地之間的差分輸入會切換輸出。需要幅度至少為0.15V且單端電壓在MAX9152的VCC和地之間的差分輸入,才能滿足交流規格。

在1:2分路器模式下,輸出會重復所選輸入。這在分配信號或創建備份副本(用于保護切換,如在轉發器中)時很有用。

在雙通道緩沖器模式下,器件會恢復信號幅度,允許隔離介質段或延長介質傳輸距離。該器件是一個交叉點開關,任何輸入都可以連接到任何一個或多個輸出。在2:1最大模式下,可以選擇主信號和備份信號,以提供故障切換、容錯應用。

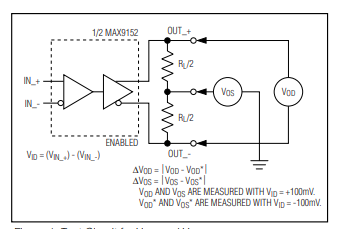

圖1. VOD和VOS測試電路

(圖中展示了相關測試電路的連接和參數測量方式 )

-

信號

+關注

關注

12文章

2922瀏覽量

80368 -

lvds

+關注

關注

2文章

1239瀏覽量

70125 -

LVPECL

+關注

關注

2文章

77瀏覽量

18888 -

交叉點開關

+關注

關注

1文章

16瀏覽量

6186

發布評論請先 登錄

美國國家半導體兩款低功率LVDS 2x2交叉點開關電路

DS25CP152 3.125Gbps LVDS 2x2交叉點開關數據表

DS90CP22 800 Mbps 2x2 LVDS交叉點開關數據表

DS90CP02 1.5 Gbps 2x2 LVDS交叉點開關數據表

DS10CP152 1.5Gbps 2X2 LVDS交叉點開關數據表

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關技術手冊

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關技術手冊

評論