CDCLVD1216時鐘緩沖器將兩個可選時鐘輸入(IN0、IN1)中的一個分配給16對差分LVDS時鐘輸出(OUT0、OUT15),時鐘分配的偏斜最小。該CDCLVD1216可以接受兩個時鐘源進入輸入多路復用器。輸入可以是LVDS、LVPECL或LVCMOS。

*附件:cdclvd1216.pdf

該CDCLVD1216專為驅動 50 Ω輸電線路而設計。如果以單端模式驅動輸入,則適當的偏置電壓 (V AC_REF )應用于未使用的負輸入引腳。

IN_SEL引腳選擇路由到輸出的輸入。如果此引腳保持打開狀態,則會禁用輸出(靜態)。該部件支持故障安全功能。它包含輸入遲滯,可防止在沒有輸入信號的情況下輸出隨機振蕩。

該器件在 2.5 V 電源環境中工作,特性為 –40°C 至 85°C(環境溫度)。該CDCLVD1216采用小型48引腳、7mm×7mm QFN封裝。

特性

- 2:16 差分緩沖器

- 低附加抖動:10 kHz 至 20 MHz 時為

<300 fs RMS - 55 ps(最大值)的低輸出偏斜

- 通用輸入接受 LVDS、LVPECL、LVCMOS

- 通過控制引腳選擇時鐘輸入

- 16 個 LVDS 輸出,兼容 ANSI EIA/TIA-644A 標準

- 時鐘頻率高達 800 MHz

- 2.375–2.625V 器件電源

- LVDS基準電壓,V

AC_REF,可用于電容耦合輸入 - 工業溫度范圍 –40°C 至 85°C

- 封裝采用 7mm × 7mm 48 引腳 QFN (RGZ) 封裝

- ESD 保護超過 3 kV HBM、1 kV CDM

- 應用

- 電信/網絡

- 醫學影像

- 測試和測量設備

- 無線通信

- 通用時鐘

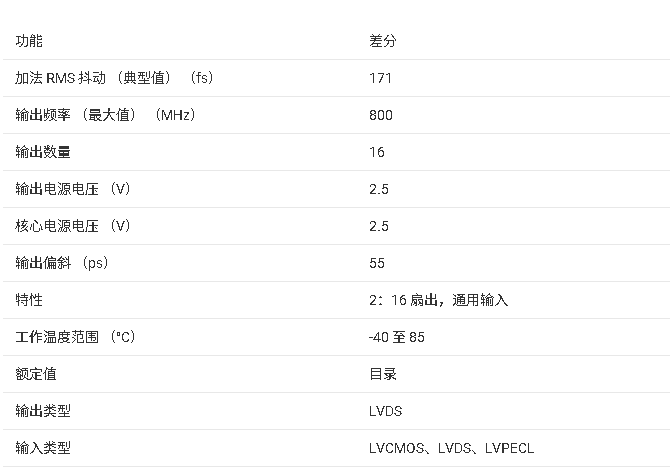

參數

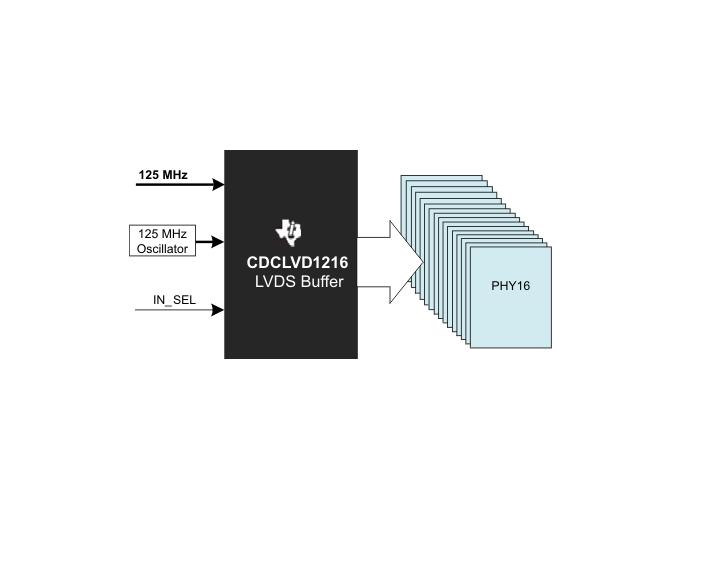

方框圖

?1. 產品概述?

CDCLVD1216是德州儀器(TI)推出的2:16差分時鐘緩沖器,專為高性能時鐘分配設計。核心特性包括:

- ?16路LVDS輸出?:符合ANSI EIA/TIA-644A標準,支持最高800MHz時鐘頻率

- ?低抖動性能?:附加抖動<300 fs RMS(10kHz-20MHz頻段)

- ?多協議輸入?:兼容LVDS、LVPECL和LVCMOS信號

- ?工業級工作溫度?:-40°C至85°C

?2. 關鍵參數?

- ?電源電壓?:2.375V-2.625V(典型2.5V)

- ?輸出特性?:

- 差分輸出電壓250-450mV

- 輸出偏斜≤55ps(最大值)

- 傳播延遲2.5ns(典型值)

- ?熱特性?:48引腳QFN封裝(7mm×7mm),結至環境熱阻30.6°C/W

?3. 功能框圖?

- 輸入選擇通過IN_SEL引腳控制(0=IN0,1=IN1,懸空=關閉輸出)

- 集成參考電壓生成器(VAC_REF)用于容性耦合輸入

- 內置200kΩ輸入上拉/下拉電阻

?4. 典型應用?

- 電信/網絡設備時鐘樹

- 醫療成像系統

- 測試測量儀器

- 無線通信基站

- 通用時鐘分配場景

?5. 設計注意事項?

- ?熱管理?:必須將底部散熱焊盤接地以優化散熱

- ?電源濾波?:建議每個電源引腳配置0.1μF去耦電容

- ?輸入配置?:

- LVDS輸入推薦100Ω端接

- 3.3V LVCMOS需限制擺幅(VIH≤VCC)

- 未用輸入建議通過1kΩ電阻接地

- ?輸出配置?:

- LVDS輸出需100Ω差分端接

- 交流耦合時建議使用0.1μF電容

?6. 可靠性特性?

- ESD保護:3kV HBM,1kV CDM

- 絕對最大額定值:電源電壓-0.3V至2.8V

文檔還包含詳細的電氣特性表、時序圖、封裝尺寸及典型應用電路圖,適用于高速時鐘分配系統的硬件設計參考。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

輸電線路

+關注

關注

1文章

797瀏覽量

24474 -

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51910 -

lvds

+關注

關注

2文章

1237瀏覽量

69820 -

多路復用器

+關注

關注

9文章

1057瀏覽量

66768 -

時鐘源

+關注

關注

0文章

110瀏覽量

16753

發布評論請先 登錄

相關推薦

熱點推薦

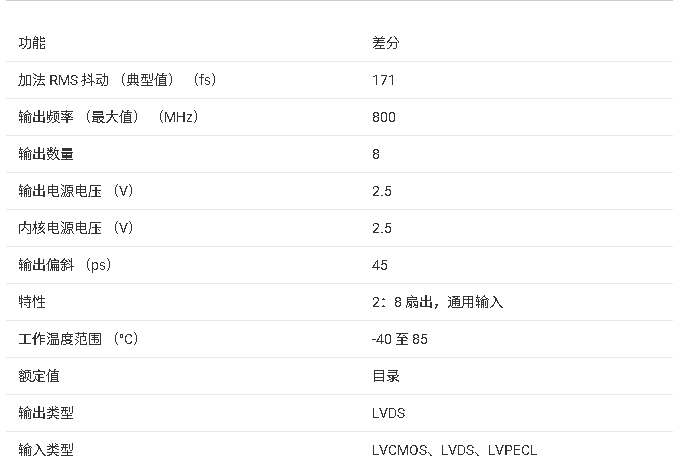

CDCLVD1208 2:8低加性抖動LVDS緩沖器數據表

電子發燒友網站提供《CDCLVD1208 2:8低加性抖動LVDS緩沖器數據表.pdf》資料免費

發表于 08-21 11:15

?0次下載

CDCLVD1212 2:12低加性抖動LVDS緩沖器數據表

電子發燒友網站提供《CDCLVD1212 2:12低加性抖動LVDS緩沖器數據表.pdf》資料免

發表于 08-21 11:16

?0次下載

CDCLVD2108雙通道1:8低附加抖動LVDS緩沖器數據表

電子發燒友網站提供《CDCLVD2108雙通道1:8低附加抖動LVDS緩沖器數據表.pdf》資料

發表于 08-21 10:50

?0次下載

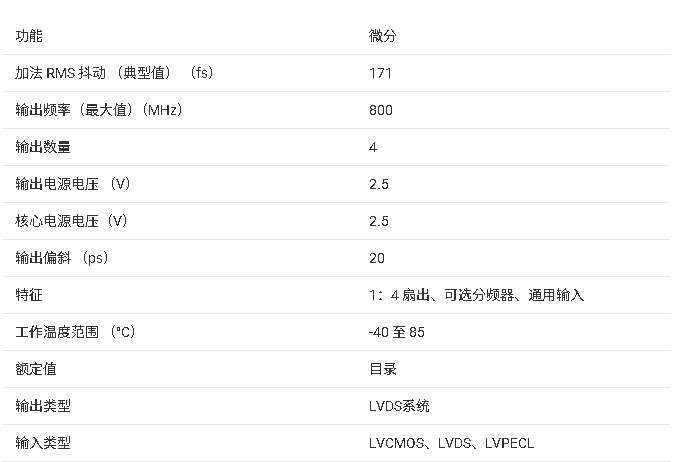

CDCLVD1204 2:4低加性抖動LVDS緩沖器數據表

電子發燒友網站提供《CDCLVD1204 2:4低加性抖動LVDS緩沖器數據表.pdf》資料免費

發表于 08-21 11:10

?0次下載

?CDCLVD1208 2:8低附加抖動LVDS緩沖器技術文檔總結

CDCLVD1208時鐘緩沖器分配兩個可選時鐘輸入(IN0和IN1)之一 8對差分LVDS時鐘輸出(OUT0至OUT7),時鐘偏移最小 分配。該CDCLVD1208可以接受兩個時鐘源進

探索 CDCLVD1212:低抖動 LVDS 緩沖器的卓越性能與應用指南

——CDCLVD1212,它在眾多領域都展現出了非凡的實力。 文件下載: cdclvd1212.pdf 產品概述 CDCLVD1212 是一款 2:12 的

探索CDCLVD1208:低抖動LVDS緩沖器的卓越性能與應用

探索CDCLVD1208:低抖動LVDS緩沖器的卓越性能與應用 在電子設計領域,時鐘緩沖器是確保

CDCLVD1216:低抖動LVDS時鐘緩沖器的設計與應用

CDCLVD1216:低抖動LVDS時鐘緩沖器的設計與應用 在電子設計領域,時鐘信號的精準分配至關重要。德州儀器(TI)的

CDCLVD2104:高性能雙路1:4低附加抖動LVDS緩沖器解析

CDCLVD2104:高性能雙路1:4低附加抖動LVDS緩沖器解析 在電子設計領域,時鐘

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析 在電子設計

CDCLVD1213:高性能低抖動LVDS緩沖器的設計與應用

抖動時鐘分配方面表現出色,能滿足多種應用場景的需求。 文件下載: cdclvd1213.pdf 一、產品概述 CDCLVD1213是一款1:4低附加

?CDCLVD1216 2:16低附加抖動LVDS緩沖器技術文檔總結

?CDCLVD1216 2:16低附加抖動LVDS緩沖器技術文檔總結

評論