文章來(lái)源:學(xué)習(xí)那些事

原文作者:小陳婆婆

本文介紹了功率半導(dǎo)體晶圓級(jí)封裝的發(fā)展。

在功率半導(dǎo)體封裝領(lǐng)域,晶圓級(jí)芯片規(guī)模封裝技術(shù)正引領(lǐng)著分立功率器件向更高集成度、更低損耗及更優(yōu)熱性能方向演進(jìn)。

本文分述如下:

晶圓級(jí)MOSFET封裝革命

晶圓級(jí)封裝發(fā)展趨勢(shì)

1. 晶圓級(jí)MOSFET封裝革命

相較于傳統(tǒng)分立功率封裝,晶圓級(jí)MOSFET通過(guò)封裝形態(tài)的革新實(shí)現(xiàn)了體積占比的根本性轉(zhuǎn)變——從早期DPAK封裝中約75%的環(huán)氧模塑化合物(EMC)占比,逐步演進(jìn)至WLCSP中EMC完全消失、硅及互連金屬占比超80%的極致緊湊結(jié)構(gòu)。這一轉(zhuǎn)變不僅體現(xiàn)在體積指標(biāo)上,更深刻影響了器件的電氣性能與可靠性設(shè)計(jì)。

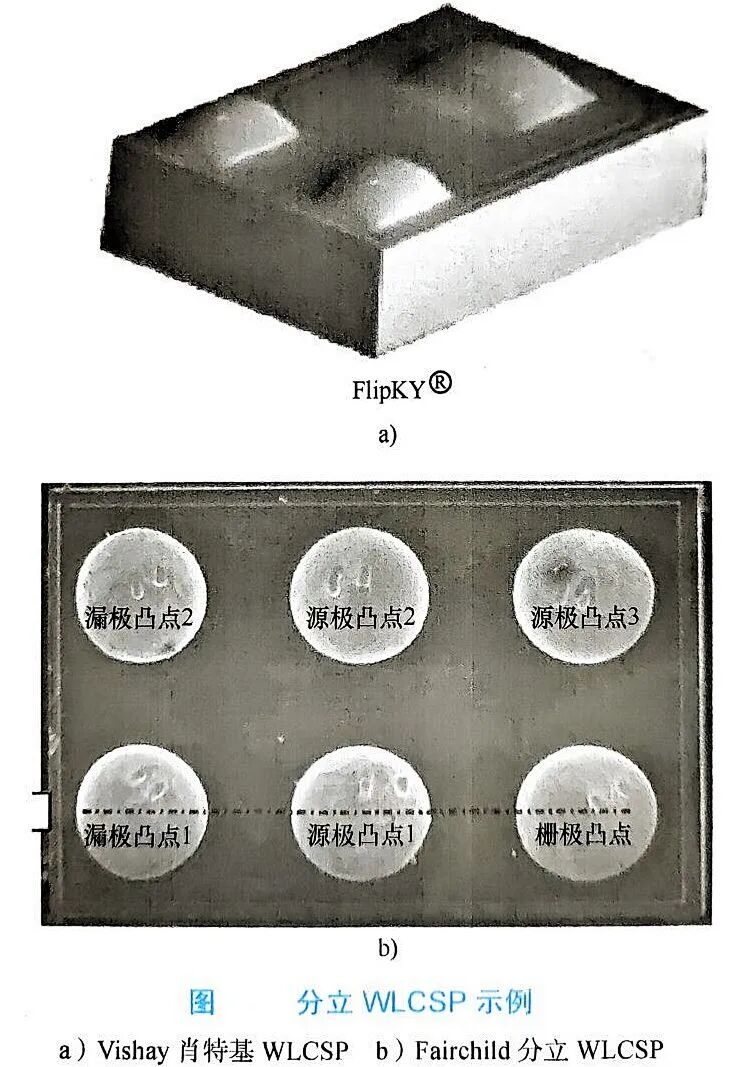

例如,Vishay與Fairchild推出的晶圓級(jí)肖特基二極管及垂直MOSFET產(chǎn)品,通過(guò)扇入型布局實(shí)現(xiàn)了芯片級(jí)封裝,而EMC在扇出型封裝中則轉(zhuǎn)型為重布線層(RDL)基底材料,通過(guò)晶圓級(jí)環(huán)氧樹(shù)脂成型技術(shù)構(gòu)建出具備更大間距的收縮芯片封裝結(jié)構(gòu),既保留了EMC對(duì)器件機(jī)械魯棒性的增強(qiáng)作用,又適配了多樣化取放設(shè)備的安裝需求。

面對(duì)高電流能力需求與芯片收縮趨勢(shì)的雙重挑戰(zhàn),晶圓級(jí)功率封裝的載流能力提升策略呈現(xiàn)出多維度創(chuàng)新特征。在熱管理層面,行業(yè)形成了PCB級(jí)強(qiáng)化散熱與封裝級(jí)多方向散熱的協(xié)同路徑。以金屬框架集成工藝為例,F(xiàn)airchild的MOSFET BGA與Vishay的PolarPAK通過(guò)預(yù)刻蝕腔金屬晶圓與芯片的鍵合,實(shí)現(xiàn)了熱擴(kuò)散路徑的立體化重構(gòu),有效提升了器件在復(fù)雜熱環(huán)境下的穩(wěn)定性。這種設(shè)計(jì)思路在最新研究中進(jìn)一步延伸至復(fù)合金屬基板與納米導(dǎo)熱材料的融合應(yīng)用,通過(guò)微通道散熱結(jié)構(gòu)的精準(zhǔn)構(gòu)建,將熱阻降低至傳統(tǒng)方案的30%以下。

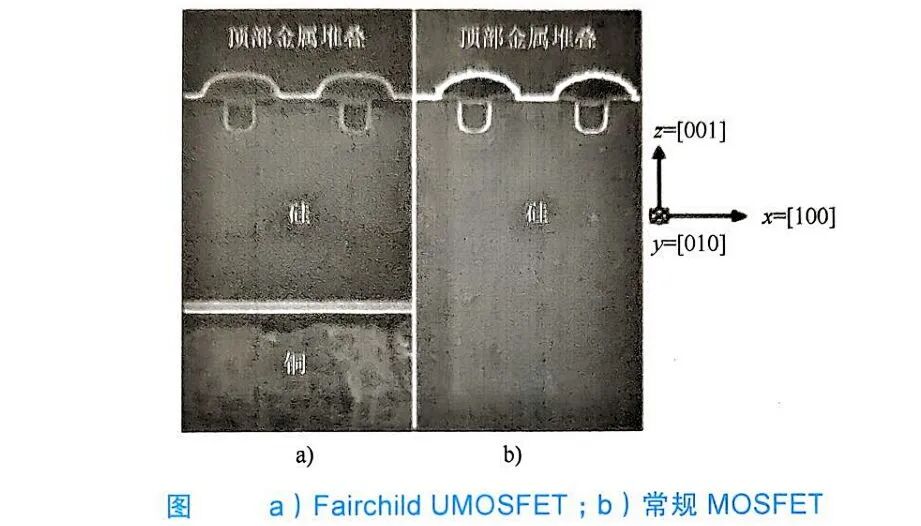

在電氣性能優(yōu)化方面,垂直金屬氧化物晶圓級(jí)MOSFET通過(guò)超薄硅基板(如7μm級(jí))與厚銅漏極(50μm級(jí))的工藝組合,實(shí)現(xiàn)了Rds(on)電阻的顯著降低與熱性能的同步提升。

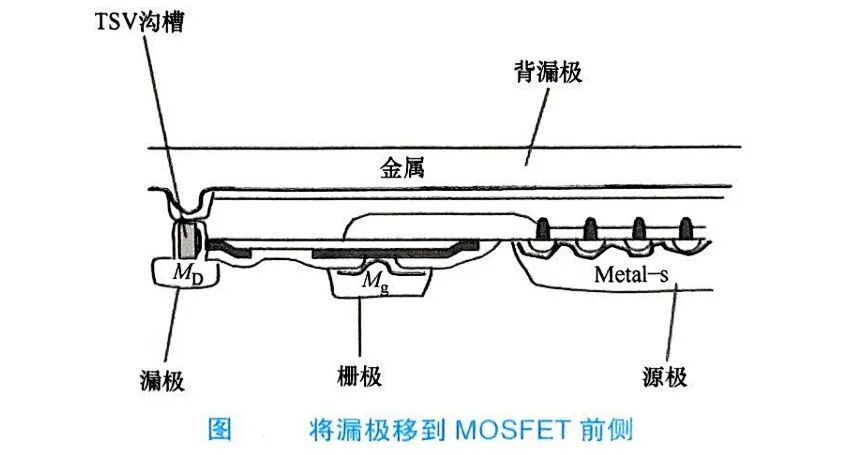

Fairchild的晶圓級(jí)UMOSFET結(jié)構(gòu)便是典型代表,其通過(guò)硅基板減薄與銅鍍層工藝的協(xié)同,在保證機(jī)械強(qiáng)度的同時(shí),將漏極電阻壓縮至傳統(tǒng)結(jié)構(gòu)的1/5。值得關(guān)注的是,行業(yè)正探索漏極位置重構(gòu)的新路徑——將漏極、源極、柵極集成于芯片同側(cè)的橫向布局,雖在高壓應(yīng)用中存在局限,但在低功率場(chǎng)景下展現(xiàn)出表面安裝兼容性與電氣性能的雙重優(yōu)勢(shì)。

對(duì)于VDMOS WLCSP,溝槽區(qū)域TSV直連技術(shù)的突破,實(shí)現(xiàn)了背漏極至前側(cè)的直接電氣連接,在保持低Rds(on)特性的同時(shí),進(jìn)一步簡(jiǎn)化了封裝工藝流程。

當(dāng)前,該領(lǐng)域的前沿探索正聚焦于三維集成技術(shù)與新型材料的深度融合。例如,基于硅通孔(TSV)的3D WLCSP結(jié)構(gòu)已實(shí)現(xiàn)多芯片垂直互連,在功率模塊中展現(xiàn)出更高的功率密度與熱管理效率;而碳納米管、石墨烯等新型導(dǎo)熱材料的引入,則為封裝級(jí)散熱設(shè)計(jì)提供了更優(yōu)的解決方案。

2. 晶圓級(jí)封裝發(fā)展趨勢(shì)

功率IC封裝的發(fā)展趨勢(shì)

在功率IC封裝領(lǐng)域,5~100V電壓范圍的解決方案正通過(guò)單片集成技術(shù)實(shí)現(xiàn)電感負(fù)載范圍的拓展與功能集成度的躍升,典型如晶圓級(jí)片上電源系統(tǒng)將高壓側(cè)/低壓側(cè)電源開(kāi)關(guān)與IC驅(qū)動(dòng)器集成,配合無(wú)傳感器定位、自適應(yīng)運(yùn)動(dòng)控制等數(shù)字功能,形成高集成度的電源轉(zhuǎn)換架構(gòu)。對(duì)于100~700V高壓場(chǎng)景,下一代LDMOS結(jié)構(gòu)已突破硅基幾何極限,通過(guò)優(yōu)化摻雜分布與場(chǎng)板設(shè)計(jì)提升擊穿電壓,推動(dòng)AC-DC單片功率變換能力升級(jí),同時(shí)多晶粒集成極限持續(xù)突破,支撐高功率密度模塊開(kāi)發(fā)。

隨著芯片尺寸向亞毫米級(jí)收縮,封裝占用面積雖呈下降趨勢(shì),但熱管理挑戰(zhàn)愈發(fā)凸顯——WLCSP與PCB級(jí)散熱器的機(jī)械兼容性問(wèn)題導(dǎo)致板級(jí)封裝可靠性降低,傳統(tǒng)空氣冷卻已難以滿足高功率密度需求。

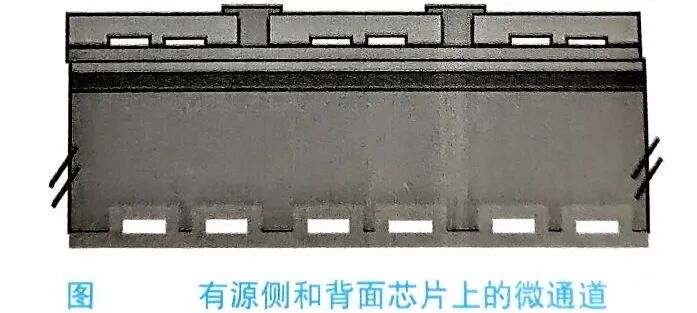

當(dāng)前前沿探索聚焦于晶圓級(jí)微通道冷卻技術(shù),通過(guò)在芯片有源側(cè)/背面構(gòu)建微米級(jí)流道,配合高導(dǎo)熱流體實(shí)現(xiàn)高效熱擴(kuò)散,可完全替代散熱器并消除風(fēng)扇噪聲,該方案在數(shù)據(jù)中心電源模塊中已實(shí)現(xiàn)熱阻降低40%的實(shí)測(cè)效果。

晶圓級(jí)無(wú)源器件的發(fā)展趨勢(shì)

晶圓級(jí)無(wú)源器件的發(fā)展正突破低功率限制,通過(guò)新型材料與工藝創(chuàng)新向中高功率延伸。例如,采用氮化鋁基板的晶圓級(jí)電感器在MHz級(jí)高頻下可承載數(shù)安培電流,其自諧振頻率可達(dá)100MHz以上,遠(yuǎn)超傳統(tǒng)封裝級(jí)電感器性能;而集成電阻器與電容器的BCDMOS工藝已實(shí)現(xiàn)寄生參數(shù)壓縮至傳統(tǒng)方案的1/3,在降壓轉(zhuǎn)換器中顯著降低開(kāi)關(guān)損耗。

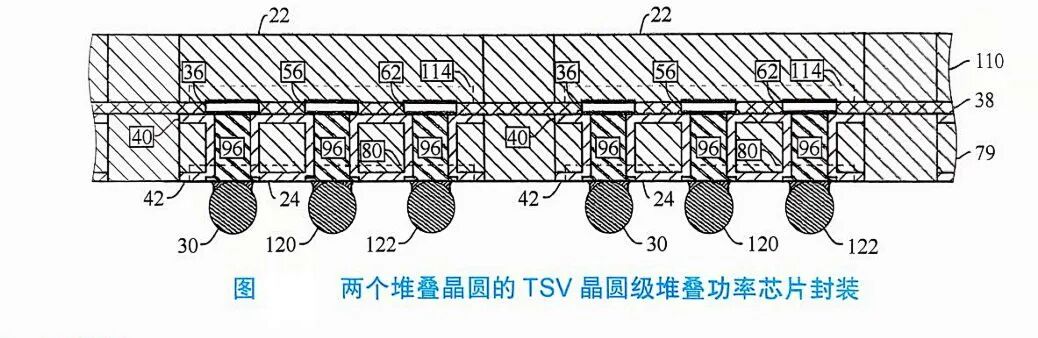

晶圓級(jí)堆疊/3D功率芯片SiP

三維集成與堆疊技術(shù)成為功率SiP的核心演進(jìn)方向。晶圓對(duì)晶圓鍵合配合TSV互連可實(shí)現(xiàn)雙晶圓堆疊,如將MOSFET與驅(qū)動(dòng)IC垂直集成于無(wú)源晶圓上方,通過(guò)TSV連接公共源極/漏極,使高邊/低邊芯片間距縮短至50μm以內(nèi),寄生電阻降低60%以上。

該結(jié)構(gòu)在LCD背光逆變器中已驗(yàn)證,半橋拓?fù)涞拈_(kāi)關(guān)延遲壓縮至2ns以下。當(dāng)前研究正探索混合鍵合與硅通孔微凸點(diǎn)技術(shù),以實(shí)現(xiàn)更高密度的3D堆疊,同時(shí)解決熱應(yīng)力匹配問(wèn)題。

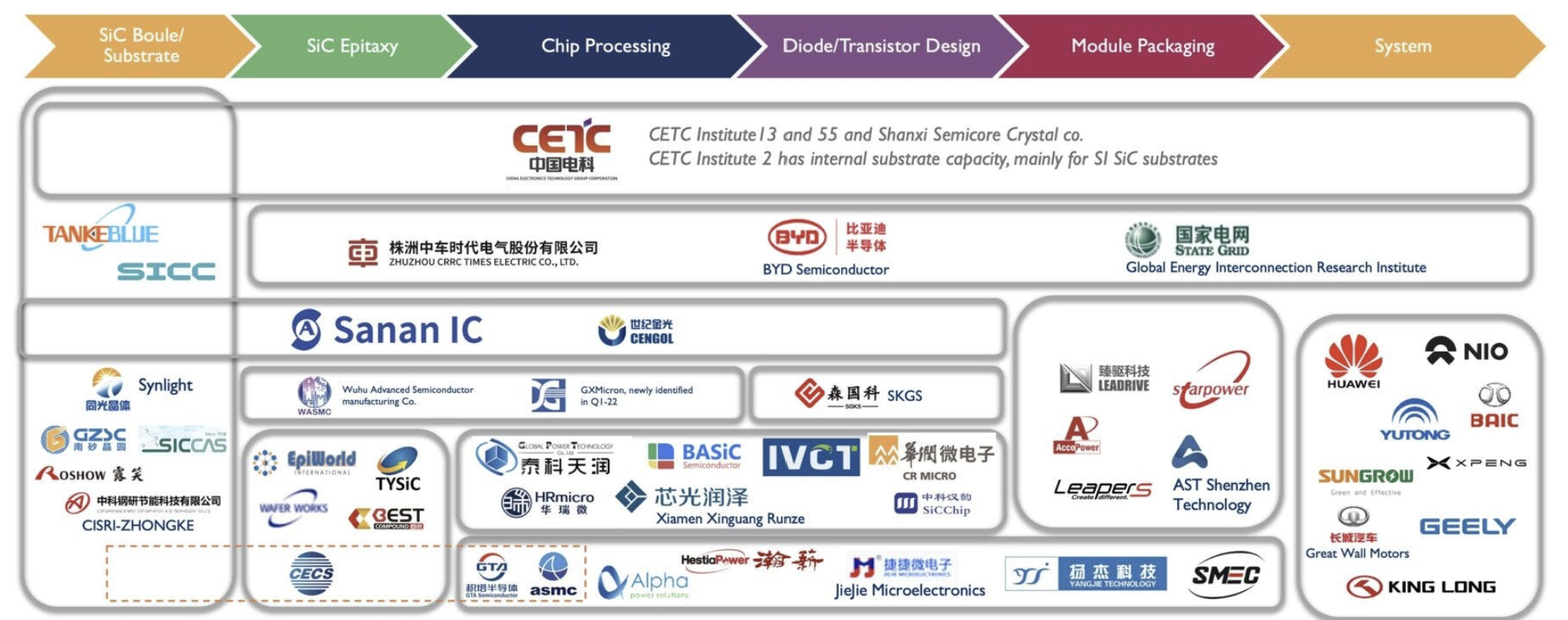

綜上,功率晶圓級(jí)封裝正沿著高集成度、高頻化、三維化的路徑演進(jìn)。扇入型WLCSP仍是主流,但扇出型技術(shù)通過(guò)RDL重布線與EMC成型工藝逐步成熟,在汽車功率模塊中已實(shí)現(xiàn)批量應(yīng)用。VDMOSFET漏極前移技術(shù)持續(xù)普及,配合TSV直連與復(fù)合金屬基板,推動(dòng)全表面貼裝兼容性提升。未來(lái),隨著碳化硅、氮化鎵等寬禁帶材料與晶圓級(jí)封裝的深度融合,以及AI驅(qū)動(dòng)的熱管理算法優(yōu)化,功率器件將向更高功率密度、更低損耗的智能集成方向加速突破,在新能源汽車、智能電網(wǎng)等領(lǐng)域發(fā)揮關(guān)鍵作用。

-

MOSFET

+關(guān)注

關(guān)注

151文章

9846瀏覽量

234138 -

封裝

+關(guān)注

關(guān)注

128文章

9292瀏覽量

148849 -

功率半導(dǎo)體

+關(guān)注

關(guān)注

23文章

1476瀏覽量

45219

原文標(biāo)題:功率晶圓級(jí)芯片尺寸封裝開(kāi)發(fā)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

先進(jìn)封裝技術(shù)的發(fā)展趨勢(shì)

新興的半導(dǎo)體技術(shù)發(fā)展趨勢(shì)

MEMS的發(fā)展趨勢(shì)怎么樣?

5G創(chuàng)新,半導(dǎo)體在未來(lái)的發(fā)展趨勢(shì)將會(huì)如何?

功率半導(dǎo)體模塊的發(fā)展趨勢(shì)如何?

半導(dǎo)體芯片產(chǎn)業(yè)的發(fā)展趨勢(shì)

什么是半導(dǎo)體晶圓?

大功率半導(dǎo)體激光器封裝技術(shù)發(fā)展趨勢(shì)及面臨的挑戰(zhàn)

陸芯半導(dǎo)體精密晶圓切割機(jī)領(lǐng)域發(fā)展趨勢(shì)及方向

半導(dǎo)體封裝新紀(jì)元:晶圓級(jí)封裝掀起技術(shù)革命狂潮

2025年功率半導(dǎo)體的五大發(fā)展趨勢(shì)

功率半導(dǎo)體晶圓級(jí)封裝的發(fā)展趨勢(shì)

功率半導(dǎo)體晶圓級(jí)封裝的發(fā)展趨勢(shì)

評(píng)論