了解封裝設(shè)備的原理,有助于設(shè)備的選型及灌膠工藝的深入了解,中匯翰騎小編給大家簡(jiǎn)單介紹下透明屏的封裝工藝;

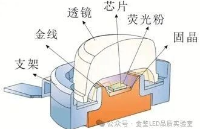

SMD表貼工藝技術(shù)

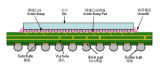

SMD:它是Surface Mounted Devices的縮寫,意為:表面貼裝器件。采用SMD(表貼技術(shù))封裝的LED產(chǎn)品,是將燈杯、支架、晶元、引線、環(huán)氧樹脂等材料封裝成不同規(guī)格的燈珠。用高速貼片機(jī),以高溫回流焊將燈珠焊在電路板上,制成不同間距的顯示單元。

SMD小間距一般是把LED燈珠裸露在外,或采用面罩的方式。由于技術(shù)成熟穩(wěn)定、制造成本低、散熱效果好、維修方便等特點(diǎn),故在LED應(yīng)用市場(chǎng)也占據(jù)了較大份額。但由于存在嚴(yán)重的缺陷,已是無法滿足現(xiàn)在市場(chǎng)的需求。

1、防護(hù)等級(jí)低:時(shí)常會(huì)出現(xiàn)燈珠不亮,列亮,死燈,掉燈,怕冷風(fēng),怕水汽,怕灰塵,怕刮蹭等居多問題,不具備防潮、防水、防塵、防震、防撞。在潮濕的氣候下,容易出現(xiàn)大批次的死燈、壞燈現(xiàn)象。在運(yùn)輸?shù)倪^程中容易出現(xiàn)掉燈,壞燈的現(xiàn)象。也容易受到靜電的影響,造成死燈現(xiàn)象。

2、 對(duì)眼睛傷害大:長(zhǎng)時(shí)間觀看會(huì)出現(xiàn)刺眼、疲勞,不能保護(hù)眼睛。此外,有些劣質(zhì)產(chǎn)品還存在“藍(lán)害”影響,因藍(lán)色LED波長(zhǎng)短,頻率高,人眼直接地、長(zhǎng)期地接受藍(lán)光影響,容易引起視網(wǎng)膜病變。

目前市面上能夠有效解決以上問題的工藝主要有COB、GOB、VOB封裝。

COB封裝工藝

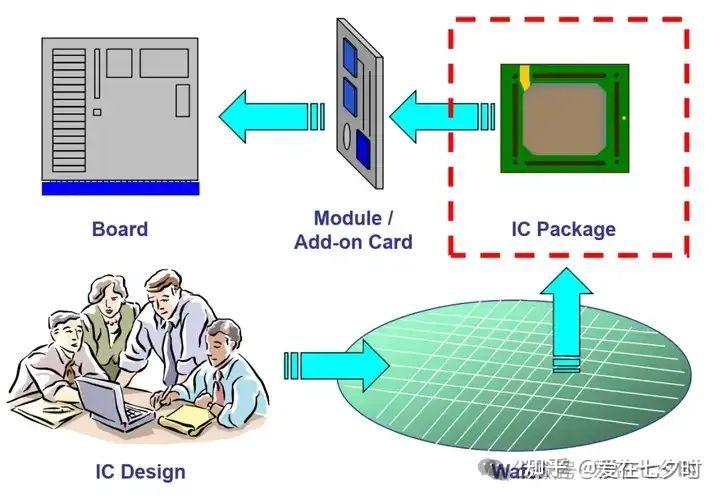

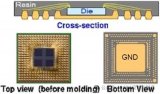

COB :chip on board?發(fā)光芯片在基板上封裝;

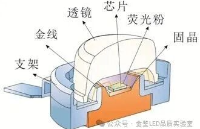

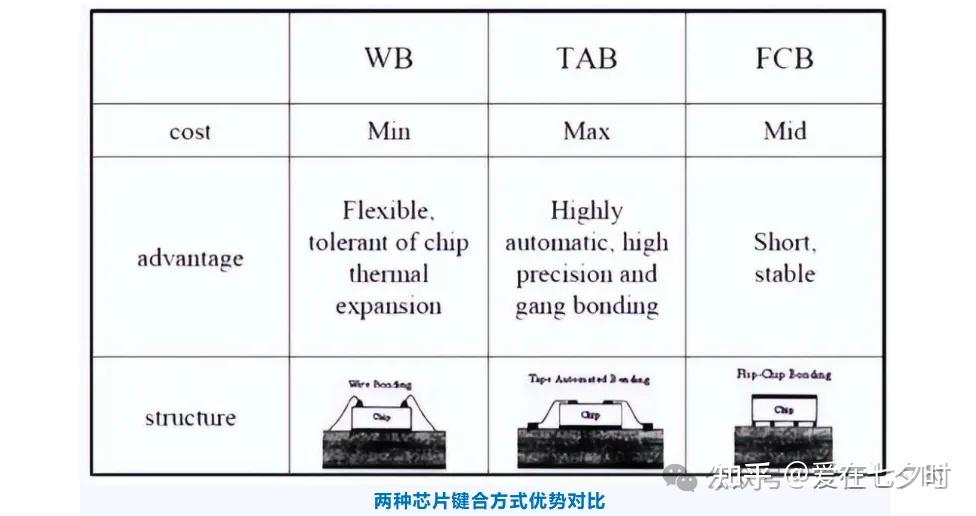

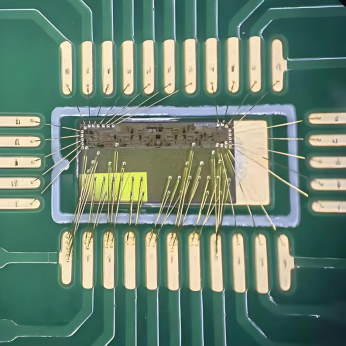

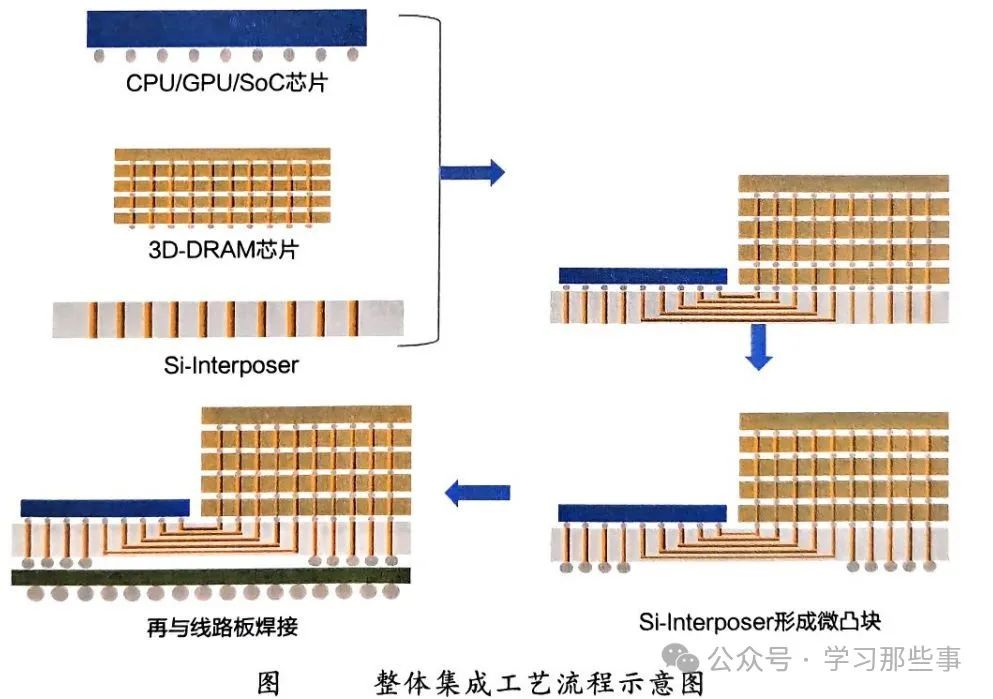

COB指的是在基底表面用導(dǎo)熱環(huán)氧樹脂覆蓋硅片安放點(diǎn),然后將硅片直接安放在基底表面,熱處理至硅片牢固地固定在基底為止,隨后再用絲焊的方法在硅片和基底之間直接建立電氣連接。裸芯片技術(shù)主要有兩種形式:一種是COB技術(shù),另一種是倒裝片技術(shù)(Flip Chip)。板上芯片封裝(COB),半導(dǎo)體芯片交接貼裝在印刷線路板上,芯片與基板的電氣連接用引線縫合方法實(shí)現(xiàn),并用樹脂復(fù)蓋以確保可靠性。雖然COB是簡(jiǎn)單的裸芯片貼裝技術(shù),但它的封裝密度遠(yuǎn)不倒片焊技術(shù)。

COB相對(duì)于SMD的工藝的優(yōu)勢(shì):

1、防磕碰、防撞擊;

2、防氧化、防靜電;

3、防潮、防塵、正面防水、易清洗;

4、點(diǎn)光源到面光源,無像素顆粒感,畫面柔和,不易產(chǎn)生視覺疲勞;

5、有效抑制摩爾紋,減少光線折射,顯示畫面更優(yōu)質(zhì);

6、減少制作工藝步驟,提高品質(zhì)控制,可靠性高,COB產(chǎn)品失效率低;

7、間距更小:采用COB封裝沒有貼片、SMT等步驟,可以完成更小間距的實(shí)現(xiàn),單位內(nèi)顯示像素越多,畫面自然清晰;

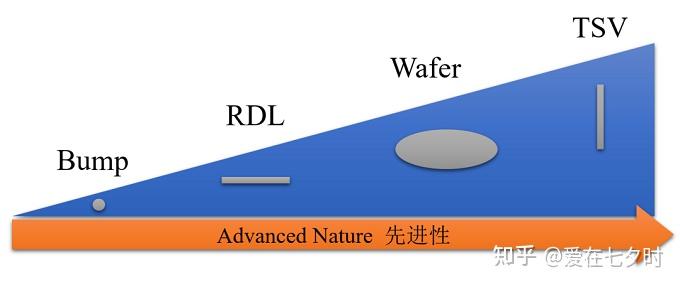

COB正裝與倒裝技術(shù)的區(qū)別?

倒裝LED芯片相對(duì)于正裝芯片來說,是電極芯片的布局和實(shí)現(xiàn)電氣功能的方式不同。倒裝芯片的電極是朝下的,而且不需要正裝芯片的鍵合焊接工藝,這樣可以大大提高生產(chǎn)效率。

COB倒裝技術(shù)優(yōu)勢(shì):

1、有源層更貼近基板,縮短了熱源到基板的熱流路徑,具有較低的熱阻。

2、適合大電流驅(qū)動(dòng),光效更高。

3、優(yōu)越的可靠性,可提高產(chǎn)品壽命,降低產(chǎn)品維護(hù)成本。

4、尺寸可以做到更小,光學(xué)更容易匹配。

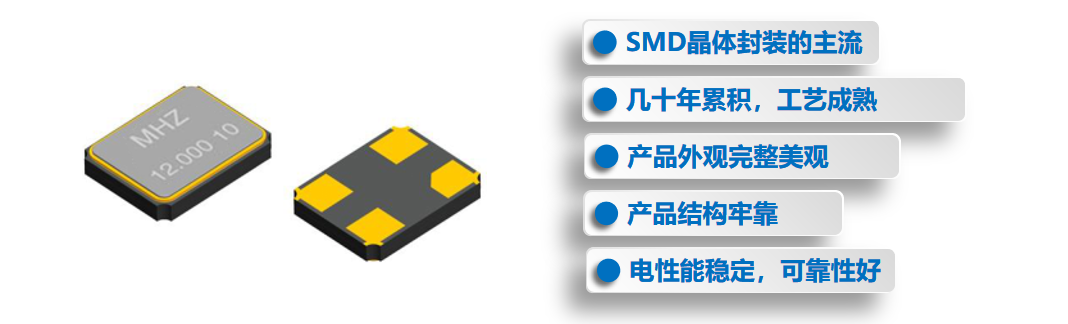

GOB工藝

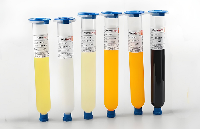

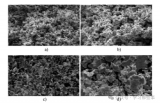

GOB是Glue on board的縮寫,是為了解決LED燈防護(hù)問題的一種技術(shù),是采用了一種先進(jìn)的新型透明材料對(duì)基板及其LED封裝單元進(jìn)行封裝,形成有效的保護(hù)。該材料不僅具備超高的透明性能,同時(shí)還擁有超強(qiáng)的導(dǎo)熱性。使GOB小間距可適應(yīng)任何惡劣的環(huán)境,相比傳統(tǒng)SMD其特點(diǎn)是,具有高防護(hù)性:防潮、防水、防塵、防撞擊、防磕碰、防靜電、防鹽霧、防氧化、防藍(lán)光、防震動(dòng),可以應(yīng)用于更多惡劣的環(huán)境,避免大面積死燈、掉燈等現(xiàn)象發(fā)生。

LED透明屏VOB工藝

VOB是市面上GOB工藝上的一種升級(jí)工藝,采用的進(jìn)口VOB納米膠涂敷,通過納米級(jí)的涂敷機(jī)控制涂層更薄,平整性更高,且LED防護(hù)性更強(qiáng)、故障率更低、黑屏一致性更高、畫面更加柔和,極大地提升了屏幕的觀看顯示效果。

VOB的優(yōu)勢(shì):

1、防護(hù)性更強(qiáng):

防潮、防水、防塵、防撞擊、防磕碰、防靜電、防鹽霧、防氧化、防藍(lán)光、防震動(dòng);這樣可以解決安裝過程中的磕碰,甚至焊盤脫落導(dǎo)致的PCB報(bào)廢。

2、故障率低,可靠性高:

整體的將燈珠不良降低到5PPM以下,這樣客戶不用擔(dān)心交付驗(yàn)收,用戶不用擔(dān)心使用。

3、易維修:

繼承了SMD簡(jiǎn)易單燈維修等優(yōu)點(diǎn),在VOB車間經(jīng)過我司培訓(xùn)合格的工程師, 便可進(jìn)行維修,重新安裝后不會(huì)存在顏色差異。

4、畫面柔和,不易產(chǎn)生視覺疲勞:

VOB工藝將LED燈由點(diǎn)發(fā)光源變成面發(fā)光源,觀看起來畫面柔和,無像素顆粒感,同時(shí)可以減輕摩爾紋效果。

5、黑屏一致性提高,對(duì)比度增高:

VOB工藝涂覆層厚度,顏色可控,有效解決了PCB?墨色不一致的問題,可以提高屏幕底色黑度,增加對(duì)比度,而且不損失視角。

VOB系列產(chǎn)品質(zhì)量控制生產(chǎn)步驟大概分3步:

1.?首先選取最優(yōu)質(zhì)的材料、燈珠、業(yè)內(nèi)超高刷IC方案、高品質(zhì)LED晶片;

2.?產(chǎn)品裝配好后,通過納米級(jí)涂敷機(jī)灌膠前,老化72小時(shí),對(duì)燈進(jìn)行檢測(cè);

3.?灌膠后,再老化24小時(shí),再次確認(rèn)產(chǎn)品質(zhì)量。

?

審核編輯:ymf

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論